一种存储器的写控制电路、写电路及存储器的制作方法

本发明涉及半导体,尤其涉及一种存储器的写控制电路、写电路及存储器。

背景技术:

1、mram(magnetic random access memory,磁随机存储器)主要是通过控制磁隧道结(magnetic tunnel junction,简称mtj)的电阻大小来存储信息。mtj的电阻大小不同是因为mtj内的两个磁阻层的磁状态方向不同。这两个磁阻层通常被称为固定层与自由层,固定层的磁状态方向固定,而自由层的磁状态方向可以改变,自由层的磁状态方向只能改变成两种当中的一种。当自由层的磁状态方向与固定层的磁状态方向相同时,mtj呈现低阻态,被称为p态(平行态);当自由层的磁状态方向与固定层的磁状态方向相反时,mtj呈现高阻态,被称为ap态(反平行态)。因为mtj这两种状态的阻值不同,可以通过感测读电流的大小判断mtj是处于p态还是ap态,即可以读出是二进制逻辑状态的“0”还是“1”。

2、本领域通常把改变自由层的磁状态方向的操作称为写入。写入需要用一定大小的电流在一段时间内持续通过mtj才能完成。控制电流通过mtj时间的信号被称为写使能信号,电流通过mtj时间的长度与写使能信号持续的使能时间宽度(简称写使能信号宽度)相等。写使能信号宽度需要达到一个最小值(该最小值称为写使能信号的时间宽度阈值),才能保证写入成功。在应用过程中,诸如mram之类的电阻式存储器设备也支持其它存储器设备使用的访问协议,例如同步双数据速率协议(ddr、ddr2、ddr3、ddr4)等。同步双数据速率协议一般用于dram(dynamic random access memory,动态随机存取存储器)设备上。mram设备也可以支持诸如同步双数据速率协议等的这种协议。但是,在ddr4协议中,两个写命令信号之间的最小时间间隔(最小时间间隔越小,写速度越快),小于mram设备里需要的写使能信号宽度阈值。在这样的情况下想要mram设备上使用ddr4协议,采用一般的写入方法,上一个写命令信号还未完成,下一个写命令信号就到了,会导致写入冲突。假如把写使能信号宽度减小至小于两个写命令信号之间的最小时间间隔,mtj会因为写时间长度(电流持续通过mtj的时间长度)不够,导致写入失败。

技术实现思路

1、本发明提供了一种存储器的写控制电路、写电路及存储器,既不减小写使能信号宽度,又能够满足写速度要求。

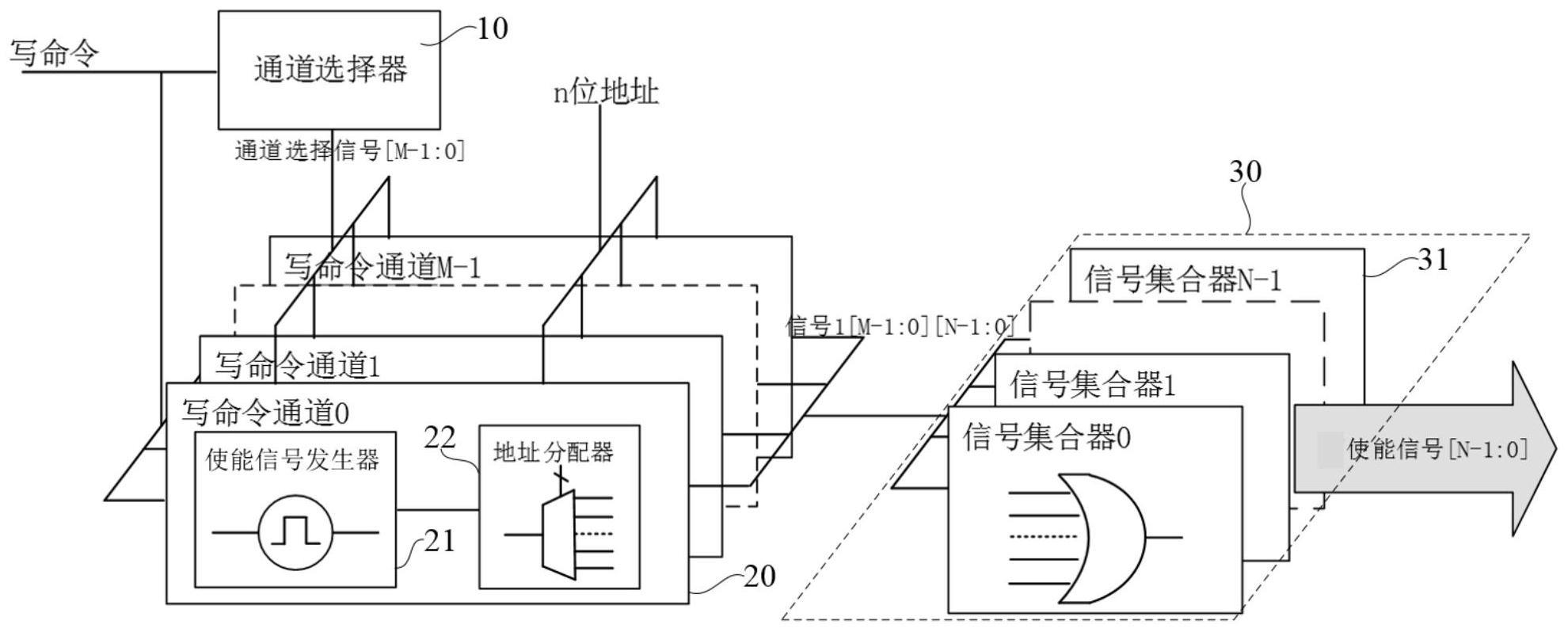

2、第一方面,本发明提供了一种存储器的写控制电路,该写控制电路包括通道选择器、与通道选择器均连接的多个写命令通道、以及与多个写命令通道均连接的信号集合模块。其中,通道选择器控制多个写命令通道中的每个写命令通道依次开启和关闭,以使处于开启状态的写命令通道接收写命令信号、和该写命令信号对应的地址信号。多个写命令通道中的每个写命令通道,用于响应其所接收的写命令信号,产生该写命令信号对应的写使能信号。信号集合模块用于集合且并发的输出多个写命令通道产生的写使能信号。

3、在上述的方案中,通过在存储器的写控制电路中设置多个写命令通道,由通道选择器控制多个写命令通道中的每个写命令通道依次轮流接收写命令信号和对应的地址信号,并使每个写命令通道能够响应其所接收到一个写命令信号和对应的地址信号,产生该写命令信号对应的写使能信号,再由信号集合模块将多个写命令通道集合多个写命令通道产生的写使能信号之后并发的输出。在应用时,通过本技术的写控制电路,在写命令信号的最小间隔时间小于写使能信号宽度阈值的情况下,既能够实时不断的接收传输过来的写命令信号和地址信号,满足写速度要求;又能够使每个写命令通道持续产生达到时间宽度阈值的写使能信号宽度,而不减小写使能信号宽度,完成正常写入,提高写入的效率。同时,还具有实现简单、适用范围广、可扩展性强的优点。

4、在一个具体的实施方式中,写控制电路接收写命令信号的最小间隔时间为t;每个写命令通道响应其所接收的写命令信号,产生该写命令信号对应的写使能信号的时间宽度阈值为t;写命令通道的个数为m,则m×t≥t。以在满足写速度要求和写使能信号宽度要求的情况下,尽量减少写命令通道的个数。

5、在一个具体的实施方式中,多个写命令通道中的每个写命令通道包括:使能信号发生器、以及与使能信号发生器连接的地址分配器。其中,使能信号发生器用于在该写命令通道处于开启状态时,接收写命令信号,并响应其所接收的写命令信号,产生该写命令信号对应的写使能信号。地址分配器用于在该写命名通道处于开启状态时,接收写命令信号对应的地址信号,并响应其所接收的地址信号,将使能信号发生器产生的写使能信号通过信号集合模块输出。便于设置每个写命令通道。

6、在一个具体的实施方式中,通道选择器通过向多个写命令通道中的每个写命令通道发送通道选择信号,控制多个写命令通道中的每个写命令通道依次开启和关闭。在某个写命令通道接收到的通信选择信号为第一信号时,该写命令通道被开启;在某个写命令通道接收到的通道选择信号为第二信号时,该写命令通道被关闭。便于通道选择器控制多个写命令通道中的每个写命令通道,依次轮流的接收写命令信号和对应的地址信号。

7、在一个具体的实施方式中,第一信号为二进制的“1”,第二信号为二进制的“0”,简化通道选择信号的组成方式。

8、在一个具体的实施方式中,地址信号的位宽为n,信号集合模块包含有n个信号集合器,且n=2n,每种地址信号对应一个信号集合器。每个信号集合器均与多个写命令通道连接,以使每个写命令通道将其产生的写使能信号,通过其所接收的地址信号所对应的信号集合器输出。简化信号集合模块的设置,同时便于信号集合模块将多个写命令通道产生的写使能信号集合后并发的对应输出。

9、在一个具体的实施方式中,在写命令通道产生写使能信号时,该写命令通道在每个振荡周期向其所接收的地址信号对应的信号集合器,持续发送写使能信号,而向其他的信号集合器持续发送非使能信号。在写命令通道没有产生写使能信号时,该写命令通道在每个振荡周期向所有的信号集合器均发送非使能信号。便于信号集合模块将多个写命令通道产生的写使能信号进行集合。

10、在一个具体的实施方式中,写使能信号为二进制的“1”,非使能信号为二进制的“0”。n个信号集合器中的每个信号集合器均包含一个逻辑或运算器;逻辑或运算器具有多个逻辑输入端,多个逻辑输入端与多个写命令通道一一对应,且每个逻辑输入端连接对应的写命令通道;逻辑或运算器的逻辑输出端与该信号集合器的输出端连接。便于每个信号集合器将其从多个写命令通道接收的写使能信号或非使能信号进行集合。

11、第二方面,本发明还提供了一种存储器的写电路,该存储器的写电路包括:写命令模块、上述任意一种存储器的写控制电路、以及写驱动电路。其中,写命令模块用于输出写命令信号、以及该写命令信号对应的地址信号,通道选择器和每个写命令通道均与写命令模块连接。写驱动电路与信号集合模块连接,写驱动电路用于接收信号集合模块并发输出的写使能信号。

12、在上述的方案中,通过在存储器的写控制电路中设置多个写命令通道,由通道选择器控制多个写命令通道中的每个写命令通道依次轮流接收写命令信号和对应的地址信号,并使每个写命令通道能够响应其所接收到一个写命令信号和对应的地址信号,产生该写命令信号对应的写使能信号,再由信号集合模块将多个写命令通道集合多个写命令通道产生的写使能信号之后并发的输出。在应用时,通过本技术的写电路,在写命令信号的最小间隔时间小于写使能信号宽度阈值的情况下,既能够实时不断的接收传输过来的写命令信号和地址信号,满足写速度要求;又能够使每个写命令通道持续产生达到时间宽度阈值的写使能信号宽度,而不减小写使能信号宽度,完成正常写入,提高写入的效率。同时,还具有实现简单、适用范围广、可扩展性强的优点。

13、第三方面,本发明还提供了一种存储器,该存储器包括上述的存储器的写电路。通过在存储器的写控制电路中设置多个写命令通道,由通道选择器控制多个写命令通道中的每个写命令通道依次轮流接收写命令信号和对应的地址信号,并使每个写命令通道能够响应其所接收到一个写命令信号和对应的地址信号,产生该写命令信号对应的写使能信号,再由信号集合模块将多个写命令通道集合多个写命令通道产生的写使能信号之后并发的输出。在应用时,通过上述示出的存储器的写电路,在写命令信号的最小间隔时间小于写使能信号宽度阈值的情况下,既能够实时不断的接收传输过来的写命令信号和地址信号,满足写速度要求;又能够使每个写命令通道持续产生达到时间宽度阈值的写使能信号宽度,而不减小写使能信号宽度,完成正常写入,提高写入的效率。同时,还具有实现简单、适用范围广、可扩展性强的优点。

- 还没有人留言评论。精彩留言会获得点赞!