半导体装置的制作方法

半导体装置

1.相关申请的交叉引用

2.本技术要求于2021年6月18日在韩国知识产权局提交的韩国专利申请no.10-2021-0079204的权益,针对所有目的,该申请的全部公开内容以引用方式并入本文中。

技术领域

3.实施例涉及一种半导体装置。

背景技术:

4.半导体装置包括连接至其它外部装置的焊盘,并且焊盘可连接至半导体装置中包括的输入/输出电路,并且输入/输出电路包括发送器和接收器中的至少一个。

技术实现要素:

5.实施例涉及一种半导体装置,该半导体装置包括:多个焊盘,其连接至外部装置;存储器单元阵列,其中设置有多个存储器单元;逻辑电路,其被配置为控制所述存储器单元阵列并且包括连接至所述多个焊盘的多个输入/输出电路;以及至少一个电感器电路,其连接在所述多个焊盘中的至少一个与所述多个输入/输出电路中的至少一个之间。电感器电路包括连接在所述多个焊盘中的所述至少一个与所述多个输入/输出电路中的所述至少一个之间的电感器图案以及设置在所述电感器图案的至少一些部分之间的可变图案。可变图案与所述电感器图案、所述多个焊盘中的所述至少一个和所述多个输入/输出电路中的所述至少一个分离。

6.实施例涉及一种半导体装置,该半导体装置包括:半导体衬底;多个元件,其设置在所述半导体衬底上;以及互连区,其具有设置为连接至所述多个元件的多个布线图案,所述多个布线图案包括连接至多个焊盘之一的电感器图案和与所述电感器图案设置在同一层上的可变图案。所述电感器图案包括在平行于所述半导体衬底的上表面的第一方向上邻近于所述可变图案的两侧的第一线和第二线,并且所述第一线、所述第二线和所述可变图案在与所述第一方向交叉并且平行于所述半导体衬底的所述上表面的第二方向上延伸。

7.实施例涉及一种半导体装置,该半导体装置包括:多个焊盘,其连接至外部装置;输入/输出电路,其连接至所述多个焊盘;以及至少一个电感器电路,其连接在所述多个焊盘中的至少一个和所述输入/输出电路之间。电感器电路包括连接在所述多个焊盘中的至少一个与所述输入/输出电路之间的电感器图案、以及与所述电感器图案分离并且邻近于所述电感器图案的至少一个可变图案。所述电感器图案包括多个线图案,并且所述多个线图案中的邻近于所述可变图案的一些线图案之间的第一间距大于所述线图案的不邻近于所述可变图案的其它部分之间的第二间距。

附图说明

8.通过参照附图详细描述示例实施例,特征将对于本领域技术人员变得明显,在附

图中:

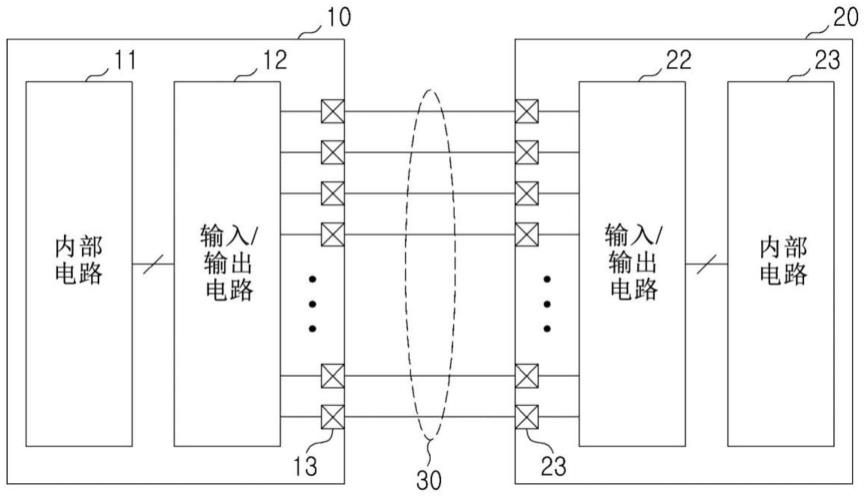

9.图1是示出根据示例实施例的包括半导体装置的系统的示意性框图;

10.图2至图5是被提供为示出根据示例实施例的半导体装置的操作的图;

11.图6和图7是示意性地示出根据示例实施例的半导体装置的图;

12.图8和图9是示意性地示出根据示例实施例的半导体装置中包括的电感器电路的图;

13.图10a至图10d是用于描述根据示例实施例的半导体装置中包括的电感器电路的操作的图;

14.图11a至图11d是示意性地示出根据示例实施例的半导体装置中包括的电感器电路的图;

15.图12和图13是示意性地示出根据示例实施例的半导体装置的图;

16.图14a和图14b是示意性地示出根据示例实施例的半导体装置中包括的电感器电路的图;

17.图15a至图15c是用于描述根据示例实施例的半导体装置中包括的电感器电路的操作的图;

18.图16是示意性地示出根据示例实施例的半导体装置的图;

19.图17是示出根据示例实施例的半导体装置的示意图;

20.图18和图19是示出根据示例实施例的半导体装置的图;以及

21.图20是示出根据示例实施例的包括半导体装置的系统的示意图。

具体实施方式

22.图1是示出根据示例实施例的包括半导体装置的系统的示意性框图。

23.参照图1,根据示例实施例的系统可包括第一半导体装置10和第二半导体装置20,并且第一半导体装置10和第二半导体装置20可连接以能够彼此通信。

24.第一半导体装置10可包括内部电路11、输入/输出电路12和多个焊盘13。

25.第二半导体装置20也可包括内部电路21、输入/输出电路22和多个焊盘23。

26.第一半导体装置10的内部电路11和第二半导体装置20的内部电路21可具有不同结构并且可执行不同功能。例如,第一半导体装置10可为应用处理器,并且其内部电路11可包括cpu、gpu、dsp、npu、存储器接口、显示器接口、电源电路等。作为另一示例,第二半导体装置20可为连接至应用处理器的存储器装置,并且其内部电路21可包括其中设置有存储器单元的存储器单元阵列以及控制存储器单元阵列的外围电路。

27.第一半导体装置10和第二半导体装置20可通过连接焊盘13和23的多条传输线30交换信号。例如,多条传输线30可通过形成在其上安装有第一半导体装置10和第二半导体装置20的印刷电路板(pcb)上的布线图案来设置。在另一实施方式中,第一半导体装置10和第二半导体装置20堆叠在彼此上,多条传输线30可通过在堆叠方向上连接第一半导体装置10和第二半导体装置20的竖直过孔结构来设置。

28.当第一半导体装置10将数据发送至第二半导体装置20时,数据可调制为预定信号然后被发送。在这种情况下,通过确保用于发送数据的信号的完整性,第二半导体装置20可接收和解调信号,以精确恢复通过第一半导体装置10发送的数据。

29.当在输入/输出电路12与多个焊盘13之间以及在调制数据以生成信号的输入/输出电路12中存在寄生成分时,可能难以确保用于发送和接收数据的信号的完整性。

30.关于上面这些,在示例实施例中,电感器电路可连接至多个焊盘13和23中的至少一个与输入/输出电路12和22之间的信号路径。电感器电路可包括具有预定电感的电感器图案,并且可包括设置在电感器图案的至少一些部分之间并且与电感器图案分离的可变图案。通过浮置电感器电路中包括的可变图案或者通过将可变图案连接至预定的电源电压来控制电感器电路的总电感,可确保半导体装置10和20之间交换的信号的完整性并且可提高眼图容限(eye margin)。

31.图2至图5是被提供为示出根据示例实施例的半导体装置的操作的图。

32.首先,图2和图3是示出半导体装置的比较例的图。

33.参照图2,根据比较例的半导体装置50可包括内部电路51、输入/输出电路52和焊盘53。

34.内部电路51可根据半导体装置50的功能包括各种电路,并且输入/输出电路52可包括发送器tx和接收器rx。发送器tx的输出端子和接收器rx的输入端子可连接至焊盘53,并且发送器tx的输入端子和接收器rx的输出端子可连接至内部电路51。

35.在输入/输出电路52与焊盘53之间的信号路径中可存在寄生成分c

par

。从发送器tx输出至焊盘53的信号或者通过接收器rx从焊盘53接收的信号可由于寄生成分c

par

而失真,如下面结合图3的讨论,信号的完整性会劣化并且眼图容限会减小。

36.参照图3,在输入/输出电路52与焊盘53之间交换的信号可为基于中间电压v

ct

摆动的信号。例如,当接收器rx接收信号时,可定义第一有效周期t

v1

(其中接收器rx可恢复有效数据)。当在第一有效周期t

v1

中存在确定接收器rx的操作时序的时钟信号的上升沿或下降沿时,接收器rx可准确地输出数据。在图3所示的比较例中,信号的第一有效周期t

v1

和电压的摆动电平δv1由于寄生成分c

par

会减小,结果,眼图容限减小,导致信号完整性劣化。

37.作为对照,参照图4,根据示例实施例的半导体装置60可包括电感器电路l

pad

。

38.参照图4,电感器电路l

pad

可串联连接在输入/输出电路62与焊盘63之间,例如,电感器电路l

pad

的一端可连接至输入/输出电路62,并且电感器电路l

pad

的另一端可连接至焊盘63。然而,电感器电路l

pad

的连接形式可根据示例实施例不同地修改。

39.电感器电路l

pad

可具有可调整或可变电感而非固定电感。例如,电感器电路l

pad

的至少一部分可连接至内部电路61中包括的至少一个电路元件,并且电感器电路l

pad

的电感可利用电路元件进行调整。

40.电感器电路l

pad

的电感可根据在输入/输出电路62与焊盘63之间存在的寄生成分c

par

设定或确定。电感器电路l

pad

的电感可与寄生成分c

par

的电容组合,并且可确定为可确保在输入/输出电路62与焊盘63之间交换的信号的最大眼图容限的值。

41.参照图5,通过合适地选择电感器电路l

pad

的电感,信号的有效周期可从图3所示的第一有效周期t

v1

增大至第二有效周期t

v2

。另外,电压的摆动电平也可增大至大于图3所示的第一摆动电平δv1的第二摆动电平δv2。

42.图6和图7是示意性地示出根据示例实施例的半导体装置的图。

43.首先,参照图6,半导体装置100可具有中心焊盘115设置在中心区110中的中心焊盘结构。中心焊盘115可通过再分布层105连接至边缘焊盘125和135(其分别设置在半导体

装置100的边缘区120和130中)。

44.半导体装置100可包括形成在半导体衬底上的多个电路元件和连接至所述多个电路元件的多个布线图案。多个布线图案可将多个电路元件彼此连接,或者可将多个电路元件连接至中心焊盘115。例如,在半导体装置100中,连接至中心焊盘115的输入/输出电路可设置在中心区110中。因此,将输入/输出电路和中心焊盘115连接的布线图案的长度可缩短,并且寄生成分可明显减小。

45.参照图7,半导体装置200可为存储器装置并且可包括多个单元存储器区210。

46.半导体装置200可为动态随机存取存储器(dram),并且单元存储器区210可定义为存储体(memory bank)。多个单元存储器区210中的每一个可包括存储器单元阵列211、行解码器212、读出放大器电路(sa)213和列解码器214。

47.半导体装置200的操作可受逻辑电路205控制。逻辑电路205可将外部接收的数据存储在多个单元存储器区210中的至少一个中,或者基于从外部源接收到的地址信息从多个单元存储器区210中的至少一个读取数据,并且可以向外输出读取的数据。

48.逻辑电路205可包括用于将信号发送至外部装置和从外部装置接收信号的输入/输出电路。多个单元存储器区210可设置在逻辑电路205的两侧或相对侧上,并且逻辑电路205可设置在半导体装置200的中心区中。因此,通过将半导体装置200形成为具有如图6所示的示例实施例那样的中心焊盘结构,将逻辑电路205的输入/输出电路与中心焊盘115连接的布线图案的长度可减小,并且寄生成分可减少。在当前示例实施例中,连接输入/输出电路和中心焊盘115的布线图案中的至少一个可包括提供预定电感的电感器电路。

49.电感器电路可按照各种形状实施,并且可具有可调整电感而非固定电感。因此,电感器电路的电感可根据布线图案中存在的寄生成分的电容增大或减小,并且通过中心焊盘115发送和接收的信号的完整性可提高。

50.图8和图9是示意性地示出根据示例实施例的半导体装置中包括的电感器电路的图。

51.参照图8,根据示例实施例的半导体装置可包括电感器电路300,其包括电感器图案310和可变图案320。

52.电感器图案310可包括具有螺旋形的线圈图案、连接至线圈图案的两侧的第一连线301和第二连线302等。线圈图案可包括在第一方向(x轴方向)或第二方向(y轴方向)上延伸的多个线图案。

53.参照图8所示的示例实施例,第一连线301可为从线圈图案的外侧的第一端延伸的线,并且可与线圈图案设置在相同层上。第二连线302可为从线圈图案的内侧的第二端延伸的线,并且可与线圈图案设置在不同的层上。因此,第一连线301和第二连线302可设置在不同层上。

54.可变图案320可在物理上与电感器图案310分离,并且可连接至至少一个开关元件sw。当开关元件sw断开时,可变图案320可浮置,并且当开关元件sw导通时,可变图案320可接收地电源电压。开关元件sw可通过由包括电感器电路300的半导体装置提供的控制信号ctr断开/导通。

55.在设有可变图案320的区域中,电感器图案310中包括的线图案之间的距离可变化。参照图8,邻近于可变图案320的一些线图案之间的第一间距d1可大于不邻近于可变图

案320的一些线图案之间的第二间距d2。例如,可变图案320的宽度可与线图案中的每一个的宽度相同,并且在这种情况下,第一间距d1可为第二间距d2的至少两倍大。

56.随着可变图案320浮置或者连接至地电源电压,可调节邻近于可变图案320的两侧的线之间的互电感。例如,当可变图案320浮置时电感器电路300的总电感可大于当可变图案320连接至地电源电压时的电感器电路300的总电感。因此,当将使电感器电路300的总电感减小时,半导体装置可利用控制信号ctr将开关元件sw导通。

57.接着,参照图9,电感器电路300a可包括电感器图案310、第一可变图案320和第二可变图案330。

58.第一可变图案320和第二可变图案330可设置在不同位置,并且可分别连接至第一开关元件sw1和第二开关元件sw2。因此,第一可变图案320和第二可变图案330可独立浮置,或者可连接至地电源电压。

59.参照图9,当第一可变图案320和第二可变图案330二者都浮置时,电感器电路300a的总电感可具有最大值,并且当接收地电源电压时,第一可变图案320和第二可变图案330可生成电感的最小值。另外,当第一可变图案320和第二可变图案330之一浮置并且另一个接收地电源电压时,总电感可具有中间值。因此,与图8所示的示例实施例相比,可更多样化地调整电感器电路300a的总电感。

60.图10a至图10d是用于描述根据示例实施例的半导体装置中包括的电感器电路的操作的图。

61.图10a示出了参考示例。

62.参照图10a,电感器电路可包括第一线311和第二线312,并且第一线311和第二线312可在第一方向(x轴方向)上邻近,并且在第二方向(y轴方向)上延伸。电感器电路可包括具有螺旋形的电感器图案,例如,如上参照图8和图9所述,并且第一线311和第二线312可为电感器图案的一部分。因此,第一线311的第一电流i1和第二线312的第二电流i2可在相同方向上流动。

63.在图10a所示的参考示例中,在第一线311和第二线312之间未设置另一图案。因此,在图10a所示的参考示例中,通过第一线311和第二线312形成的电感可定义为[l1+l2+m1],其中l1是通过第一电流i1在第一线311中生成的自电感,l2是通过第二电流i2在第二线312中生成的自电感,m1是通过第一电流i1和第二电流i2在第一线311与第二线312之间生成的互电感。在图10a所示的参考示例中生成的电感[l1+l2+m1]可能不适于防止由于连接电感器电路的信号路径的寄生成分导致的信号完整性劣化。例如,为了防止由于寄生成分导致的信号完整性劣化,可需要小于电感[l1+l2+m1]的电感。

[0064]

与上述的相似,在图10b和图10c所示的示例实施例中,电感器电路可包括第一线311和第二线312,第一线311和第二线312可在第一方向(x轴方向)上邻近并且在第二方向(y轴方向)上延伸,电感器电路可包括具有螺旋形的电感器图案,第一线311和第二线312可为电感器图案的一部分。参照图10b和图10c,在当前示例实施例中,通过将可变图案230设置在第一线311和第二线312之间,并且浮置可变图案或者将可变图案连接至地电源电压,第一线311和第二线312中生成的总电感可减少。将更详细地描述这一点。

[0065]

参照图10b,可变图案320可设置在第一线311和第二线312之间,同时可变图案320在第一方向上设置在第一线311和第二线312之间,从而第一线311和第二线312在第一方向

上邻近于可变图案320的两侧。

[0066]

在另一实施方式(在图10a和图10b中未示出)中,可变图案320可在第二方向上在第一线311和第二线312之间延伸。

[0067]

在图10b所示的示例实施例中,可变图案320浮置。因此,第一线311和第二线312生成的总电感可定义为[l1+l2+m2]。互电感m2(第一线311和第二线312之间生成的互电感)可比上面参照图10a描述的互电感m1具有更低的值。在图10b所示的示例实施例中,可变图案320设置在第一线311和第二线312之间,使得第一线311和第二线312之间的间距增大,结果,与图10a的互电感m1相比,第一线311和第二线312之间的互电感m2可减小。

[0068]

接着,参照图10c,在第一方向上设置在第一线311和第二线312之间的可变图案320(同时第一线311和第二线312在第一方向上邻近于可变图案320的两侧)可连接至地电源电压gnd。在图10c所示的示例实施例中,第一线311和第二线312之间的距离通过可变图案320增大,以获得减小互电感的效果,此外,通过将可变图案320偏压到地电源电压gnd,可进一步减小互电感。因此,考虑到半导体装置的输入/输出电路与焊盘之间的寄生成分,为了减小电感器电路的电感,连接至可变图案320的开关元件可导通,以将可变图案320偏压到地电源电压gnd等,如图10c所示。

[0069]

在实施方式(未示出)中,可变图案320也可偏压至除地电源电压以外的电压。

[0070]

与上述的相似,在图10b和图10c所示的示例实施例中,电感器电路可包括第一线311和第二线312,第一线311和第二线312可在第一方向(x轴方向)上邻近并且在第二方向(y轴方向)上延伸,并且电感器电路可包括具有螺旋形的电感器图案,第一线311和第二线312可为电感器图案的一部分。参照图10d,可变图案320a可包括在第一方向上延伸的区和在第二方向上延伸的区二者。因此,可变图案320a不仅可设置在在第二方向上延伸的第一线311和第二线312之间,还可设置在在第一方向上延伸的第三线313和第四线314之间。

[0071]

图11a至图11d是示意性地示出根据示例实施例的半导体装置中包括的电感器电路的图。

[0072]

参照图11a至图11d,根据示例实施例的电感器电路可包括第一线311和第二线312以及多个可变图案320、330a和330b。

[0073]

第一线311和第二线312可在第一方向(x轴方向)上彼此邻近。第一线311、第二线312和多个可变图案320、330a和330b可在第二方向(y轴方向)上延伸。

[0074]

参照图11a和图11b,第一线311、第二线312和可变图案320和330a可设置在第一层m1和第二层m2中。例如,第一可变图案320可与第一线311和第二线312一起设置在第二层m2中,并且第二可变图案330a可形成在第一层m1中。如上参照图8和图9所述,电感器图案可包括螺旋形线圈图案、从线圈图案的外侧延伸的第一连线301和从线圈图案的内侧延伸的第二连线302,第二连线302可设置在与第一连线301和线圈图案的层不同的层上。在当前示例实施例中,第一连线301可与第二可变图案330a设置在同一第一层m1中。

[0075]

在当前示例实施例中,参照图11a,第一电流i1和第二电流i2可在第二方向上流动,第一可变图案320可偏压至地电源电压。

[0076]

在另一状态下(图11a中未示出),第二可变图案330a可浮置。

[0077]

在另一状态下,参照图11b,第一可变图案320和第二可变图案330a二者可偏压至地电源电压。因此,与图11a所示的示例实施例中的电感器电路提供的总电感相比,图11b所

示的示例实施例中的电感器电路提供的总电感可较小。这是因为在图11b所示的示例实施例中,第一可变图案320和第二可变图案330a二者均偏压至地电源电压,从而相对于图11a所示的示例实施例,第一线311与第二线312之间的互电感可进一步极大减小。

[0078]

参照图11c和图11d,第一线311、第二线312以及可变图案320和330b可设置在第一层m1和第二层m2中。在当前示例实施例中,参照图11c和11d,第二层m2中的第一可变图案320、第一线311和第二线312的厚度可大于第一层m1中的第二可变图案330b的厚度。通过在第二层m2中将线圈图案和第一可变图案320形成得较厚,电感器电路的电阻可较小。

[0079]

电感器电路提供的总电感可与上面参照图11a和11b所述的相似地确定。在图11c所示的示例实施例中,第一可变图案320偏压至地电源电压,并且第二可变图案330b浮置,而在图11d所示的示例实施例中,第一可变图案320和第二可变图案330b二者偏压至地电源电压。因此,与图11c所示的示例实施例中的电感器电路提供的总电感相比,图11d所示的示例实施例中的电感器电路提供的总电感可相对较小。

[0080]

图12和图13是示意性地示出根据示例实施例的半导体装置的图。

[0081]

首先参照图12,根据示例实施例的半导体装置400可包括电感器电路。

[0082]

半导体装置400可包括器件区tra和互连区mpa。器件区tra可包括半导体衬底401和形成在半导体衬底401上的多个元件410。互连区mpa可包括连接至多个元件410的多个布线图案420和连接至多个布线图案420的再分布层440。

[0083]

多个元件410可包括形成在半导体衬底401上的晶体管。例如,多个元件410中的每一个可包括源极/漏极区411和栅极结构415。栅极结构415可包括栅极绝缘层412、栅电极层413和栅极间隔件414。器件接触件cnt可连接至源极/漏极区411和栅极结构415,并且器件接触件cnt可连接至多个布线图案420中的至少一个。

[0084]

多个布线图案420可分开设置在多个布线层421至423上。例如,设置在第一布线层421中的第一布线图案可通过器件接触件cnt连接至多个元件410。设置在第二布线层422中的第二布线图案可通过第一过孔结构v1连接至下布线图案,并且设置在第三布线层423中的第三布线图案可通过第二过孔结构v2连接至中间布线图案。在图12所示的示例实施例中,布线图案420示为设置在三个布线层421至423中,但是其中设置有布线图案420的布线层的数量可不同地修改。

[0085]

多个布线图案420中的每一个的厚度可根据其上分别设置布线图案420的布线层421至423确定。例如,参照图12,设置在第一布线层421中的第一布线图案的厚度可最小,而设置在第三布线层423中的第三布线图案的厚度可最大。随着在垂直于半导体衬底401的上表面的方向上与半导体衬底401相距的距离增大,布线图案420的厚度可增大。

[0086]

设置在第三布线层423中的第三布线图案的至少一些区域可提供多个中心焊盘430。中心焊盘430可为设置在半导体装置400的中心区中的焊盘,并且可通过第一钝化层435暴露。中心焊盘430可连接至形成在比第三布线层423高的位置的再分布层440。

[0087]

再分布层440可包括第一再分布层441、rdl过孔442(再分布层过孔)和第二再分布层443。第一再分布层441可为直接连接至中心焊盘430的层,并且可通过rdl过孔442连接至第二再分布层443。第二再分布层443的至少一部分可提供设置在半导体装置400的边缘区中的边缘焊盘450。边缘焊盘450可通过第二钝化层455暴露于外部,并且可通过导线等连接至例如其上安装有半导体装置400的衬底的焊盘。

[0088]

在根据图12所示的示例实施例的半导体装置400中,电感器电路可形成在连接中心焊盘430和边缘焊盘450的再分布层440中。

[0089]

电感器电路可包括螺旋形线圈图案,如上所述,并且至少两层可用于形成电感器电路。例如,在图12所示的示例实施例中,利用第一再分布层441和第二再分布层443(它们相对于半导体衬底401的上表面分别形成在不同高度)实施再分布层440,并且在再分布层440中形成电感器电路。

[0090]

更详细地说,第一再分布层441可包括从线圈图案的内侧延伸的第一连线,第二再分布层443可包括线圈图案和从线圈图案的外侧延伸的第二连线。另外,与线圈图案分离并且邻近于线圈图案的可变图案可形成在第二再分布层443上。

[0091]

可变图案可连接至多个元件410中的至少一个开关元件,通过断开开关元件以将可变图案浮置或者导通开关元件以将可变图案偏压至电源电压,可调整电感器电路的电感。通过调整电感器电路的电感,可明显减少由于互连区mpa中存在的寄生成分导致的信号完整性劣化,并且信号的眼图容限可提高。

[0092]

参照图13,根据示例实施例的半导体装置500可包括器件区tra和互连区mpa。器件区tra可包括半导体衬底501和多个元件510。多个元件510的配置可类似于上面参照图12描述的配置。

[0093]

在图13所示的示例实施例中,互连区mpa可包括连接至多个元件510的多个布线图案520和连接至多个布线图案520的再分布层550等。多个布线图案520可分开设置在所述多个布线层521至524上,设置在第一布线层521上的第一布线图案可通过器件接触件cnt连接至多个元件510。随着与半导体衬底501的上表面相距的距离增大,布线图案520的厚度可增大。

[0094]

在图13所示的示例实施例中,电感器电路可形成在布线图案520中的设置在最高位置上的第三布线层523和第四布线层524中。如上所述,当电感器电路包括螺旋形线圈图案时,至少两层可用于实施电感器电路。在图13所示的示例实施例中,可利用第三布线层523和第四布线层524实施电感器电路。

[0095]

更详细地说,从线圈图案的内侧延伸的第一连线可形成在第三布线层523中。另外,线圈图案、从线圈图案的外侧延伸的第二连线和与线圈图案分离并且邻近于线圈图案的可变图案可形成在第四布线层524中。通过在布线图案520的层中的具有最大厚度的第四布线层524上形成线圈图案、第二连线、可变图案等,可显著降低电感器电路的电阻。

[0096]

连接至线圈图案的第二连线的至少部分区域在半导体装置500的中心区中通过第一钝化层535暴露于外侧,并且可提供中心焊盘530。中心焊盘530可连接至再分布层550。再分布层550的至少一些区域可通过第二钝化层555暴露于外部,以提供边缘焊盘560。

[0097]

在图12所示的示例实施例中,电感器电路可形成在连接至半导体装置400的中心焊盘430的再分布层440上。另一方面,在图13所示的示例实施例中,可利用半导体装置500的布线图案520的层中的连接至再分布层550的布线层523和524中的一些形成电感器电路。如参照图12和图13的描述,电感器电路可由具有相对大的厚度的布线图案形成,因此电感器电路的电阻可减小,从而明显减少半导体装置400、500由于电感器电路造成的性能下降。

[0098]

图14a和图14b是示意性地示出根据示例实施例的半导体装置中包括的电感器电路的图。

[0099]

参照图14a,根据示例实施例的电感器电路600包括电感器图案610和可变图案620。电感器图案610可包括线圈图案和连接至线圈图案的两侧的第一连线601和第二连线602等。

[0100]

第一连线601可为从线圈图案的一侧延伸的线,第二连线602可为从线圈图案的另一侧延伸的线。在图14a所示的示例实施例中,第一连线601和第二连线602可与线圈图案设置在同一层上。因此,电感器图案610可设置在一层上。

[0101]

可变图案620可在物理上与电感器图案610分离并且可连接至至少一个开关元件sw。例如,当开关元件sw断开时,可变图案620可浮置,并且当开关元件sw导通时,可变图案620可接收地电源电压。

[0102]

在另一实施方式(未示出)中,可变图案620可通过导通开关元件sw接收除地电源电压以外的电源电压作为偏置电压。

[0103]

开关元件sw可通过包括电感器电路600的半导体装置提供的控制信号ctr导通/断开。

[0104]

邻近于可变图案620两侧的线之间的互电感可通过将可变图案620设置在它们之间以及浮置可变图案620或者将可变图案620连接至地电源电压来调整。例如,当可变图案620浮置时的电感器电路300的总电感可与当可变图案620连接至地电源电压时的电感器电路300的总电感不同。因此,半导体装置可设为其中通过导通或断开开关元件sw来使半导体装置输入/输出的信号的眼图容限明显增大的条件,并且可参照该条件设置开关元件sw。

[0105]

参照图14b,电感器电路600a可包括电感器图案610、第一可变图案620和第二可变图案630。第一可变图案620和第二可变图案630可设置在不同位置,并且可分别连接至第一开关元件sw1和第二开关元件sw2。因此,第一可变图案620和第二可变图案630可各自独立浮置,或者连接至地电源电压。

[0106]

在图14b所示的示例实施例中,电感器电路600a的总电感在当第一可变图案620和第二可变图案630二者均浮置时可具有最小值,并且当第一可变图案620和第二可变图案630二者均偏压至地电源电压时可具有最大值。另外,当第一可变图案620和第二可变图案630之一浮置而另一个接收地电源电压时,总电感可具有中间值。因此,与图14a所示的示例实施例相比,电感器电路600a的总电感可更多样化地调整。

[0107]

图15a至图15c是用于描述根据示例实施例的半导体装置中包括的电感器电路的操作的图。

[0108]

图15a示出了参考示例。

[0109]

在图15a至图15c中,电感器电路可包括第一线611和第二线612,第一线611和第二线612可在第一方向(x轴方向)上邻近,并且可在第二方向(y轴方向)上延伸。这里,电感器电路包括具有如上面参照图14a和图14b描述的形状的电感器图案,第一线611和第二线612可为电感器图案的一部分。因此,第一线611的第一电流i1和第二线612的第二电流i2可在相反的方向上流动。

[0110]

在图15a所示的参考示例中,另一图案未设置在第一线611和第二线612之间。因此,在图15a所示的参考示例中,通过第一线611和第二线612形成的电感可定义为[l1-l2]。l1可为通过第一电流i1在第一线611中生成的自电感,l2可为通过第二电流i2在第二线612中生成的自电感。由于第一电流i1和第二电流i2在相反方向上流动,因此第一线611和第二

线612中分别生成的自电感可具有彼此抵消的效果。图15a所示的示例实施例中生成的电感可不适于防止由于连接电感器电路的信号路径的寄生成分导致的信号完整性劣化。例如,为了防止由于寄生成分导致的信号完整性劣化,可需要大于电感[l1-l2]的电感。

[0111]

在图15b和图15c所示的示例实施例中,通过在第一线611和第二线612之间设置可变图案和浮置可变图案或将可变图案连接至地电源电压,通过第一线611和第二线612生成的总电感可增大。现在,将参照图15b和图15c更详细地描述这一点。

[0112]

首先,参照图15b和15c,可变图案620设置在第一线611和第二线612之间,因此,第一线611和第二线612之间在第一方向上的间隔可增大。因此,第一线611中生成的电感l1和第二线612中生成的电感l2彼此抵消的效果可减少,并且电感器电路的总电感可增大。

[0113]

参照图15b,可变图案620可浮置。参照图15c,可变图案620可偏压至地电源电压。通过增大第一线611和第二线612之间在第一方向上的间距可提供屏蔽效果。另外,通过将可变图案620偏压至地电源电压,因此,与图15b所示的示例实施例相比,电感器电路的总电感可进一步显著增大。

[0114]

在实施方式(未示出)中,可变图案620可偏压至除地电源电压之外的电压。

[0115]

图16是示意性地示出根据示例实施例的半导体装置的图。

[0116]

参照图16,根据示例实施例的半导体装置700可包括电感器电路。

[0117]

半导体装置700可包括器件区tra和互连区mpa。器件区tra可包括半导体衬底701和形成在半导体衬底701上的多个元件710,并且多个元件710的配置可类似于上面参照图12和图13描述的配置。互连区mpa可包括连接至多个元件710的多个布线图案720、连接至多个布线图案720的再分布层740等。

[0118]

多个布线图案720可分开设置在多个布线层721至723上,并且多个布线图案720中的每一个的厚度可通过其上分别设置有布线图案720的布线层721至723确定。参照图16,设置在第一布线层721上的第一布线图案的厚度可小于设置在第三布线层723上的第三布线图案的厚度。

[0119]

设置在第三布线层723上的第三布线图案的至少一些区域可提供多个中心焊盘730。中心焊盘730可为设置在半导体装置700的中心区中的焊盘,并且可通过第一钝化层735暴露。中心焊盘730可连接至第一钝化层735上的再分布层740。

[0120]

电感器电路可形成在再分布层740上,并且电感器电路可具有上面参照图14a和14b描述的形状。因此,提供电感器电路的所有布线图案可形成在一层上,并且电感器电路可通过仅一个再分布层740实施。形成在再分布层740中的电感器电路可包括电感器图案和可变图案。

[0121]

可变图案可连接至多个元件710中的至少一个开关元件,并且通过断开开关元件以浮置可变图案,或者导通开关元件以对可变图案施偏压至电源电压,可调整电感器电路的电感。通过调整电感器电路的电感,可防止由于互连区mpa等中存在的寄生成分导致的信号完整性劣化,并且可提高信号的眼图容限。

[0122]

图17是示出根据示例实施例的包括半导体装置的半导体模块的示意图。

[0123]

参照图17,根据示例实施例的半导体模块800可包括模块衬底810和半导体装置820。半导体装置820可包括电感器电路。

[0124]

半导体装置820可安装在模块衬底810上。半导体装置820可包括多个第一焊盘

pad1,第一焊盘pad1可经由导线825连接至形成在模块衬底810上的多个第二焊盘pad2。例如,第一焊盘pad1可为通过半导体装置820中包括的再分布层提供的边缘焊盘。

[0125]

第二焊盘pad2可通过形成在模块衬底810上的衬底布线815连接至第三焊盘pad3。第三焊盘pad3可为用于将半导体模块800连接至其它外部半导体装置、半导体模块、衬底等的焊盘。

[0126]

如上所述,半导体装置820可包括用于确保信号完整性的电感器电路。例如,电感器电路可连接在半导体装置820的第一焊盘pad1与输入/输出电路之间,并且可包括电感器图案和可变图案。可变图案与电感器图案分离并且是邻近于电感器图案的图案,并且可浮置或者可接收预定电源电压作为偏置电压。在半导体装置820的制造中,电感器电路可设为提供通过在浮置可变图案或对可变图案施偏压至电源电压的同时通过测量半导体装置820输入/输出的信号的眼图容限能够确保信号完整性的电感值。

[0127]

另一方面,在图17所示的示例实施例中,电感器电路817也可形成在连接第二焊盘pad2和第三焊盘pad3的衬底布线815中的至少一个上。例如,电感器电路817可形成在高速发送和接收信号的信号路径上。当半导体装置820是存储器装置时,电感器电路817可连接至发送和接收数据信号的第三焊盘pad3的一部分。

[0128]

图18和图19是示出根据示例实施例的半导体装置的图。

[0129]

在图18所示的示例实施例中,半导体装置900可为易失性存储器装置。半导体装置900可包括连接至位线bl和字线wl的多个存储器单元mc,并且多个存储器单元mc中的每一个可包括单元开关tr和单元电容器cc。例如,通过导通单元开关tr并且为单元电容器cc充电或放电,可在多个存储器单元mc中的每一个中存储数据,并且通过导通单元开关tr和测量单元电容器cc的电压,可读取存储在多个存储器单元mc中的每一个中的数据。

[0130]

另一方面,在图19所示的示例实施例中,半导体装置900a可为非易失性存储器装置。在图19所示的半导体装置900a中,存储器单元mc1至mc8可以三维结构形成在衬底上。例如,半导体装置900a中包括的多个存储器单元串ns11至ns33可在垂直于衬底的方向上形成。

[0131]

参照图19,半导体装置900a可包括连接在位线bl1至bl3与公共源极线csl之间的多个存储器单元串ns11至ns33。多个存储器单元串ns11至ns33中的每一个可包括串选择晶体管sst、多个存储器单元mc1至mc8和地选择晶体管gst。虽然图19示出了多个存储器单元串ns11至ns33中的每一个包括八个存储器单元mc1至mc8,但是这一点可改变。

[0132]

串选择晶体管sst可连接至对应的串选择线ssl1至ssl3。多个存储器单元mc1至mc8可分别连接至对应的字线wl1至wl8。字线wl1至wl8中的一条或多条可设为伪字线。地选择晶体管gst可连接至对应的地选择线gsl1至gsl3。串选择晶体管sst可连接至对应的位线bl1至bl3,并且地选择晶体管gst可连接至公共源极线csl。

[0133]

字线wl1至wl8中的每一个可共同连接至设置在相同高度的多个存储器单元mc1至mc8,并且地选择线gsl1至gsl3和串选择线ssl1至ssl3可分别分离。虽然图19示出了八条字线wl1至wl8和三条位线bl1至bl3,但是这一点可改变。

[0134]

根据图18和图19所示的示例实施例的半导体装置900和900a可以高速执行接收和存储数据以及输出存储的数据的操作,并且因此可与显著高频的时钟信号同步操作。随着时钟信号的频率增大,信号的眼图容限可由于输入/输出信号中和在连接输入/输出信号和

焊盘的信号路径中存在的寄生成分的电容而减小。提供能够减小由于寄生成分的电容造成的影响的电感的电感器电路可连接至连接输入/输出信号和焊盘的信号路径。另外,至少一个可变图案可包括在电感器电路中,以调整电感器电路的电感,并且可选择是否将偏置电压输入至可变图案。因此,在高速输入和输出信号的半导体装置900和900a中可确保信号完整性。

[0135]

图20是示出根据示例实施例的包括半导体装置的系统的示意图。

[0136]

参照图20,移动装置1000可包括相机1100、显示器1200、音频处理单元1300、调制解调器1400、dram 1500a和1500b、闪速存储器装置1600a和1600b以及输入/输出装置1700a和1700b、传感器装置1800和应用处理器(下文中,“ap”)1900。

[0137]

移动装置1000可实施为笔记本计算机、便携式终端、智能电话、平板pc、可佩戴装置、医疗保健装置或物联网(iot)装置。另外,移动装置1000可实施为服务器或个人计算机。

[0138]

移动装置1000中包括的各种组件可与预定时钟同步操作。例如,显示器1200可根据预定刷新率显示画面,并且dram 1500a和1500b以及闪速存储器装置1600a和1600b也按照预定速度存储和读取数据,或者可根据预定时钟操作以相对于其它外部装置发送和接收数据。输入/输出装置1700a和1700b以及应用处理器1900也可根据预定时钟操作。

[0139]

相机1100可根据用户的控制捕获静态图像或动态图像。移动装置1000可利用相机1100捕获的静态图像/视频获取特定信息,或者将静态图像/视频转换为诸如文本等的其他类型的数据,并且可以存储转换后的数据。相机1100可包括具有不同的视角或光圈值的多个相机。另外,除通过拍摄对象生成实际图像的相机之外,相机1100还可包括通过使用对象和/或背景的深度信息生成深度图像的相机。

[0140]

显示器1200还可通过提供触摸屏功能用作移动装置1000的输入装置。另外,显示器1200可以与指纹传感器等集成提供,以提供移动装置1000的安全功能。音频处理单元1300可以处理存储在闪速存储器装置1600a和1600b中的音频数据,或者包括在通过调制解调器1400或输入/输出装置1700a和1700b从外部接收的内容中的音频数据。

[0141]

调制解调器1400调制并发送信号以发送/接收有线/无线数据,同时解调从外部接收的信号以恢复原始信号。输入/输出装置1700a和1700b是提供数字输入/输出的装置,并且可以是可连接到外部记录介质的端口、诸如触摸屏或机械按键的输入装置、以及能够以触觉方式输出振动的输出装置等。

[0142]

传感器装置1800可以包括从其外部收集各种信息的多个传感器。传感器装置1800可包括检测光亮度的照度传感器、用于检测移动装置1000的移动的陀螺传感器、用于从与移动装置1000接触和/或靠近移动装置1000的用户身体获取生物测定信息的生物传感器等。

[0143]

ap 1900可以控制移动装置1000的整体操作。详细地说,ap 1900可以控制显示器1200在屏幕上显示闪速存储器装置1600a和1600b中存储的部分内容。此外,当通过输入/输出装置1700a和1700b接收到用户输入时,ap 1900可以执行与用户输入相对应的控制操作。

[0144]

ap 1900可包括加速器块1920,其是用于ai数据操作的专用电路。在另一实施方式中,可以与ap 1900分开提供单独的加速器芯片,并且dram 1500b可以额外连接到加速器块1920或加速器芯片。加速器块1920是专业地执行ap 1900的特定功能的功能块,并且可以包括作为专门处理图形数据的功能块的图形处理单元(gpu)、作为专业地执行ai计算和推理

的块的神经处理单元(npu)、作为专门用于数据处理的块的数据处理单元(dpu)等。

[0145]

根据示例实施例,如上所述的电感器电路可在移动装置1000中彼此连接以彼此通信的组件中以各种方式使用。例如,根据示例实施例,电感器电路可应用于用于在相机1100、显示器1200、音频处理单元1300、调制解调器1400、dram 1500a和1500b、闪速存储器装置1600a和1600b、输入/输出装置1700a和1700b、传感器装置1800以及ap 1900中的至少一个中输入/输出信号的焊盘,以提高信号的眼图容限。

[0146]

作为总结和回顾,输入/输出电路中以及输入/输出电路与焊盘之间可存在寄生成分。输入/输出到焊盘的信号的完整性可因寄生成分而劣化。

[0147]

如上所述,实施例可提供一种半导体装置,其中通过将具有可调节电感的电感器连接到连接输入/输出电路和焊盘的路径,可以显著降低通过焊盘输入/输出的信号的完整性的劣化。

[0148]

根据示例实施例,通过将具有可调节电感的电感器连接到连接输入/输出电路和焊盘的路径,可以基于路径中存在的寄生成分的电容来设置电感器的电感。因此,尽管存在寄生成分,也可以确保通过焊盘的信号输入/输出的完整性,并且支持高速数据通信的半导体装置的性能可以得到改善。

[0149]

本文公开了示例实施例,尽管采用了特定术语,但它们仅在一般和描述性意义上被使用和解释,而不用于限制的目的。在一些情况下,随着本技术的提交,对于本领域普通技术人员显而易见的是,除非另有明确指示,否则结合特定实施例描述的特征、特性和/或元件可单独使用或与结合其他实施例描述的特征、特性和/或元件结合使用。因此,本领域技术人员将理解,在不脱离如所附权利要求所述的本发明的精神和范围的情况下,可以对形式和细节进行各种改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1