集成电路及其设计方法与流程

1.本公开涉及双端口静态随机存取存储器(sram)单元以及设计双端口sram单元的方法,更具体地,涉及双端口sram单元的布局。

背景技术:

2.由于半导体用户的积极需求和半导体制造商的不断努力,与半导体器件相关的技术持续在全球范围内实现显著增长。此外,半导体制造商努力使半导体器件更小型化、高度集成并具有大容量,同时推动研发以实现更高的速度并实现更稳定和流畅的运行。这些半导体制造商的努力带来微处理技术、微器件技术和电路设计技术的进步,使得诸如动态随机存取存储器(dram)或sram的半导体存储单元的技术取得显著成就。

3.具体地,在sram领域,已经开发出与现有的单端口sram相比能够执行高速读取和写入操作的双端口sram。在相关技术的单端口sram中,一个单位存储单元包括六个晶体管。例如,相关技术的单端口sram包括两个负载晶体管、两个驱动晶体管和两个有源晶体管以顺序地执行读取和写入操作。然而,双端口sram被配置为通过将两个有源晶体管添加到相关技术的单端口sram来以双模式执行读取和写入操作,并用于要求高速度的集成电路中。

技术实现要素:

4.一个或更多个示例实施方式提供一种能够通过在位线之间设置字线来消除在位线之间发生的干扰的集成电路。

5.此外,一个或更多个示例实施方式提供一种能够通过在位线和电源线之间布置虚设线来屏蔽位线的集成电路。

6.此外,一个或更多个示例实施方式提供一种集成电路,该集成电路能够通过在第一方向上相邻的不同位单元之间包括边界虚设线来改善在不同位单元中包括的位线之间发生的串扰现象。

7.本公开所要解决的技术问题不限于上述技术问题,其它未提及的技术问题将从以下描述而被本领域技术人员清楚地理解。

8.根据一示例实施方式的一方面,提供一种集成电路,该集成电路包括:双端口静态随机存取存储器(sram)单元,包括多个晶体管;位线对(bit line pair),连接到双端口sram单元,该位线对包括在第一方向上彼此间隔开并在垂直于第一方向的第二方向上延伸的第一位线和第二位线;电源线组,包括多条电源线,该多条电源线在第一方向上彼此间隔开、在第一方向上与位线对间隔开并在第二方向上延伸,该电源线组配置为将电压施加到双端口sram单元;以及第一字线,提供在第一位线和第二位线之间并且连接到双端口sram单元。

9.根据一示例实施方式的一方面,提供一种集成电路,该集成电路包括:第一位单元和在第一方向上与第一位单元相邻的第二位单元;边界虚设线,在第一位单元和第二位单元之间的边界处在垂直于第一方向的第二方向上延伸并电独立于第一位单元和第二位单

元;第一位线对,连接到第一位单元,第一位线对包括在第二方向上延伸并在第一方向上彼此间隔开的第一位线和第二位线;第一互补位线对,在第一方向上与第一位线对间隔开并且连接到第一位单元,第一互补位线对包括与第一位线互补的第一互补位线和与第二位线互补的第二互补位线;包括多条电源线的电源线组,提供在第一位线对和第一互补位线对之间并在第一方向上与第一位线对间隔开,该电源线组配置为将电压施加到第一位单元;第一字线,提供在第一位线和第二位线之间并且连接到第一位单元;以及第二字线,提供在第一互补位线和第二互补位线之间并且连接到第一位单元。

10.根据一示例实施方式的一方面,提供一种设计集成电路的方法,该方法包括:形成第一位单元;在第一位单元上形成包括第一位线和第二位线的第一位线对,第一位线和第二位线在第一方向上彼此间隔开并在垂直于第一方向的第二方向上延伸;在第一位单元上形成第一互补位线对,第一互补位线对包括在第一方向上彼此间隔开并在第二方向上延伸的第一互补位线和第二互补位线;以及在第一位单元上形成在第一位线与第二位线之间的第一字线以及在第一互补位线与第二互补位线之间的第二字线。

附图说明

11.从以下结合附图的详细描述,以上和/或其它的方面将被更清楚地理解,附图中:

12.图1是根据示例实施方式的集成电路(ic)的框图;

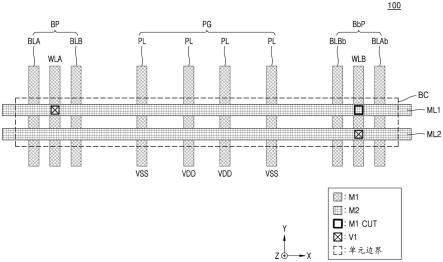

13.图2是根据一示例实施方式的位单元的布局图;

14.图3是根据示例实施方式的双端口sram的电路图;

15.图4是根据一示例实施方式的位单元的布局图;

16.图5是根据一示例实施方式的位单元的布局图;

17.图6是沿着图5的线c-c'截取的剖视图;

18.图7是根据一示例实施方式的位单元的布局图;

19.图8是根据一示例实施方式的位单元的布局图;

20.图9是根据一示例实施方式的位单元的布局图;

21.图10是根据一示例实施方式的位单元的布局图;

22.图11是根据一示例实施方式的位单元的剖视图;

23.图12是示出根据一示例实施方式的设计ic的方法的流程图;

24.图13是示出根据示例实施方式的设计ic的方法的流程图;

25.图14是示出根据示例实施方式的制造ic的方法的流程图;

26.图15是示出根据一示例实施方式的包括ic的片上系统(soc)的框图;以及

27.图16是示出根据一示例实施方式的包括存储程序的存储器的计算系统的框图。

具体实施方式

28.在下文,将参照附图描述本公开的各种实施方式。在下文,布局图中的水平方向被定义为第一方向x,布局图中的垂直方向被定义为第二方向y,与布局图基本上垂直的方向被定义为第三方向z。因此,第二方向y可以表示与第一方向x垂直的方向。附图中由箭头所指的方向和其相反方向将被描述为同一方向。上述方向的定义在下文的所有附图中都是相同的。在本说明书的附图中,为了便于图示,可能仅示出一部分。当参照附图进行描述时,对

相同或相应的部件给出相同的附图标记,并将省略对其的重复描述。

29.图1是根据一示例实施方式的集成电路的框图。

30.参照图1,集成电路10可以接收命令cmd、地址addr、时钟信号clk和写入数据data_in,并输出读取数据data_out。例如,集成电路10可以接收指示写入的命令cmd(其可以被称为写入命令)、地址addr(其可以被称为写入地址)和写入数据data_in并可以将写入数据data_in存储在存储单元块11的与该地址addr对应的区域中。此外,集成电路10可以接收指示读取的命令cmd(其可以被称为读取命令)和地址addr(其可以被称为读取地址),并可以将存储在存储单元块11的与该地址addr对应的区域中的读取数据data_out输出到外部。

31.存储单元块11可以包括多个位单元12。所述多个位单元12可以以规则的间隔布置。所述多个位单元12可以提供在字线wl和位线bl的交叉点处。也就是,所述多个位单元12中的每个可以连接到多条字线wl中的至少一条并可以连接到多条位线bl中的至少一条。

32.所述多个位单元12中的每个可以是存储单元。例如,所述多个位单元12中的每个可以是静态随机存取存储器(sram)或易失性存储单元诸如例如动态随机存取存储器(dram)。特别地,所述多个位单元12中的每个可以是能够同时执行写入操作和读取操作的双端口sram(dpsram)单元。根据一示例实施方式,位单元12可以是非易失性存储单元,诸如闪存、电阻随机存取存储器(rram)等。将主要参照dpsram单元描述本公开的示例实施方式,但是本公开的实施方式不限于此。

33.根据一示例实施方式,集成电路10可以包括列驱动器13、行驱动器14和控制块15。列驱动器13可以通过多条位线bl连接到存储单元块11。列驱动器13可以基于列地址col从所述多条位线bl选择至少一条位线。例如,列驱动器13可以选择图2的第一位线bla和图2的第一互补位线blab,第一互补位线blab与图2的第一位线bla互补。第一位线bla和第一互补位线blab可以连接到所述多个位单元12中的任何一个。因此,当列驱动器13选择第一位线bla和第一互补位线blab时,连接到第一位线bla和第一互补位线blab的多个位单元12可以被选择。

34.列驱动器13可以基于控制信号ctr执行读取操作或写入操作。列驱动器13可以通过感测经由所述多条位线bl接收的电流和/或电压来识别存储在多个位单元12当中的连接到被激活的字线的位单元中的值,并可以基于所识别的值输出读取数据data_out。列驱动器13可以基于写入数据data_in将电流和/或电压施加到所述多条位线bl,并可以将值写入所述多个位单元12中的连接到被激活的字线的一个。根据一示例实施方式,列驱动器13可以包括执行读取操作的读取电路和执行写入操作的写入电路。根据一示例实施方式,列驱动器13可以包括用于对所述多条位线bl进行预充电的位线预充电电路。

35.行驱动器14可以通过多条字线wl连接到存储单元块11。行驱动器14可以基于行地址row激活所述多条字线wl当中的至少一条字线。也就是,行驱动器14可以从所述多条字线wl当中选择至少一条字线。因此,可以从所述多个位单元12当中选择连接到被激活的字线的位单元。

36.控制块15可以接收命令cmd、地址addr和时钟信号clk,并可以产生行地址row、列地址col和控制信号ctr。例如,控制块15可以通过对命令cmd进行解码来识别读取命令,并可以产生行地址row、列地址col和控制信号ctr以从存储单元块11读取该读取数据data_out。此外,控制块15可以通过解码命令cmd来识别写入命令,并可以产生行地址row、列地址

col和控制信号ctr以将数据data_in写入存储单元块11。

37.主要参照dpsram单元来描述本公开的示例实施方式,使得所述多个位单元12中的每个可以连接到两条字线、两条位线和两条互补位线。在下文,将详细描述所述多个位单元12中的每个的布局。

38.图2是根据一示例实施方式的位单元的布局图。具体地,图2是示出连接到图1的所述多个位单元12中的任意一个位单元的位线和字线在沿第一方向x和第二方向y形成的平面上的布局的平面图。在图2中,为了便于图示,可以仅示出一些层,并且为了示出在上布线层的图案和下布线层的图案之间的连接,通路也可以被显示,尽管通路在上布线层的图案之下。为了描述的方便,可以省略构成位单元的其它部件。

39.参照图2,集成电路100可以包括位单元bc。位单元bc可以连接到第一位线bla和第二位线blb。第一位线bla和第二位线blb可以在第一方向x上彼此间隔开。第一位线bla和第二位线blb可以在第二方向y上延伸。第一位线bla和第二位线blb可以构成位线对bp。

40.位单元bc可以连接到第一互补位线blab和第二互补位线blbb。第一互补位线blab可以与第一位线bla互补,第二互补位线blbb可以与第二位线blb互补。第一互补位线blab和第二互补位线blbb可以在第一方向x上彼此间隔开。第一互补位线blab和第二互补位线blbb可以在第二方向y上延伸。第一互补位线blab和第二互补位线blbb可以构成互补位线对bbp。互补位线对bbp和位线对bp可以在第一方向x上彼此间隔开而在其间具有预定间隔。

41.位单元bc可以连接到电源线组pg。电源线组pg可以提供在位线对bp和互补位线对bbp之间。电源线组pg可以包括多条电源线pl。所述多条电源线pl可以在第一方向x上彼此间隔开而在其间具有预定间隔,并可以每条在第二方向y上延伸。

42.所述多条电源线pl中的每条可以将电源电压vdd或接地电压vss施加到位单元bc。例如,电源线组pg可以包括四条电源线pl。当按第一方向x的顺序描述时,这四条电源线pl可以按接地电压vss、电源电压vdd、电源电压vdd和接地电压vss的顺序将电压施加到位单元bc。然而,本公开不限于此,并且在另一示例实施方式中,这四条电源线pl可以交替地将电源电压vdd和接地电压vss施加到位单元bc。也就是,可以按接地电压vss、电源电压vdd、接地电压vss和电源电压vdd的顺序将电压施加到这四条电源线pl。

43.位单元bc可以连接到第一字线wla和第二字线wlb。第一字线wla和第二字线wlb可以在第一方向x上彼此间隔开。第一字线wla和第二字线wlb可以在第二方向y上延伸。

44.第一字线wla可以提供在位线对bp之间。也就是,第一字线wla可以提供在第一位线bla和第二位线blb之间。第二字线wlb可以提供在互补位线对bbp之间。也就是,第二字线wlb可以提供在第一互补位线blab和第二互补位线blbb之间。在本实施方式中,一条字线被提供在位线对bp或互补位线对bbp之间,但是不限于此,并且在另一实施方式中,两条或更多条字线可以提供在位线对或互补位线对之间。

45.位线对bp、互补位线对bbp、电源线组pg、第一字线wla和第二字线wlb可以形成在从基板起的同一层上。位线对bp、互补位线对bbp、电源线组pg、第一字线wla和第二字线wlb可以由相同的布线形成。这将参照图6详细描述。

46.第一金属布线ml1和第二金属布线ml2可以提供在位线对bp上。第一金属布线ml1和第二金属布线ml2可以在第二方向y上彼此间隔开,并可以在第一方向x上延伸。第一金属布线ml1和第二金属布线ml2可以与位线对bp和互补位线对bbp交叉。第一金属布线ml1和第

二金属布线ml2可以包括具有优良导电性的金属材料。在一示例实施方式中,第一金属布线ml1和第二金属布线ml2可以连接到外部电源。

47.通路v1可以形成在第一字线wla和第二字线wlb上。通路v1可以由具有优异导电性的金属材料形成。通路v1可以将第一字线wla连接到第一金属布线ml1并可以将第二字线wlb连接到第二金属布线ml2。因此,第一字线wla和第一金属布线ml1可以电连接到彼此,第二字线wlb和第二金属布线ml2可以电连接到彼此。也就是,施加到第一金属布线ml1和第二金属布线ml2的电压可以通过通路v1分别传输到第一字线wla和第二字线wlb。

48.第一字线wla和第二字线wlb可以被切割区域m1 cut切割。也就是,第一字线wla和第二字线wlb可以在第二方向y上延伸,并可以被切割区域m1 cut部分地切断。因此,从金属布线ml1和ml2传输到字线wla和wlb的电压可以不被位单元bc和在第二方向y上相邻的其它位单元共用。在图2中,切割区域m1 cut被示出为仅在第二字线wlb上,但是不限于此,还可以形成在第一字线wla上。例如,用于切割第一字线wla的切割区域m1 cut可以形成在沿第二方向y与位单元bc相邻的另一位单元中。

49.由于第二字线wlb形成在第二金属布线ml2下面并且切割区域m1cut形成在与第二字线wlb和第二金属布线ml2重叠的部分中,所以尽管第二字线wlb可能在布局图中呈现为连续的,但是实质上,第二字线wlb可以在第二金属布线ml2下面是部分不连续的。由于字线wla和wlb包括切割区域m1 cut,所以多个电压可以被施加到在第二方向y上延伸的字线wla和wlb。

50.由于第一字线wla提供在位线对bp之间并且第二字线wlb提供在互补位线对bbp之间,所以根据示例实施方式的位单元bc可以屏蔽位线对bp和互补位线对bbp。因此,在第一位线bla和第二位线blb之间以及在第一互补位线blab和第二互补位线blbb之间发生的串扰被最小化或者能够被防止,并且可以提供执行稳定操作的集成电路100。此外,由于位线对bp和互补位线对bbp之间的耦合被改善,所以集成电路100的操作速度可以提高。

51.在下文,将详细描述构成位单元bc并提供在位线对bp下面的晶体管。

52.图3是根据一示例实施方式的位单元的电路图。具体地,它是根据一示例实施方式的dpsram单元的等效电路图。

53.参照图3,位单元bc可以包括第一传输晶体管pg1、第二传输晶体管pg2、第三传输晶体管pg3、第四传输晶体管pg4、第一上拉晶体管pu1、第二上拉晶体管pu2、第一下拉晶体管pd1和第二下拉晶体管pd2。

54.第一至第四传输晶体管pg1、pg2、pg3和pg4以及第一下拉晶体管pd1和第二下拉晶体管pd2可以是n型晶体管,第一上拉晶体管pu1和第二上拉晶体管pu2可以是p型晶体管。

55.第一上拉晶体管pu1和第一下拉晶体管pd1可以构成第一反相器,第二上拉晶体管pu2和第二下拉晶体管pd2可以构成第二反相器。

56.具体地,第一上拉晶体管pu1的漏极端子可以连接到第一下拉晶体管pd1的漏极端子,第一上拉晶体管pu1的栅极可以电连接到第一下拉晶体管pd1的栅极。电源电压vdd可以被施加到第一上拉晶体管pu1的源极端子,接地电压vss可以被施加到第一下拉晶体管pd1的源极端子。因此,第一上拉晶体管pu1和第一下拉晶体管pd1可以构成第一反相器。

57.类似地,第二上拉晶体管pu2的漏极端子可以连接到第二下拉晶体管pd2的漏极端子,第二上拉晶体管pu2的栅极可以电连接到第二下拉晶体管pd2的栅极。电源电压vdd可以

被施加到第二上拉晶体管pu2的源极端子,接地电压vss可以被施加到第二下拉晶体管pd2的源极端子。因此,第二上拉晶体管pu2和第二下拉晶体管pd2可以构成第二反相器。

58.连接到彼此的第一上拉晶体管pu1的栅极和第一下拉晶体管pd1的栅极可以对应于第一反相器的输入端子,并且连接到第一上拉晶体管pu1的漏极端子和第一下拉晶体管pd1的漏极端子的第一节点n1可以对应于第一反相器的输出端子。

59.连接到彼此的第二上拉晶体管pu2的栅极和第二下拉晶体管pd2的栅极可以对应于第二反相器的输入端子,并且连接到第二上拉晶体管pu2的漏极端子和第二下拉晶体管pd2的漏极端子的第二节点n2可以对应于第二反相器的输出端子。

60.第一反相器和第二反相器可以以锁存结构彼此联接。也就是,第一上拉晶体管pu1的栅极和第一下拉晶体管pd1的栅极可以连接到第二节点n2,并且第二上拉晶体管pu2的栅极和第二下拉晶体管pd2的栅极可以连接到第一节点n1。

61.第一传输晶体管pg1的漏极端子和第二传输晶体管pg2的源极端子可以连接到第一节点n1。第一传输晶体管pg1的源极端子可以连接到第一位线bla,第二传输晶体管pg2的漏极端子可以连接到第二位线blb。也就是,第一传输晶体管pg1和第二传输晶体管pg2可以连接到第一节点n1。

62.类似地,第三传输晶体管pg3的漏极端子和第四传输晶体管pg4的源极端子可以连接到第二节点n2。第三传输晶体管pg3的源极端子可以连接到第一互补位线blab,第四传输晶体管pg4的漏极端子可以连接到第二互补位线blbb。也就是,第三传输晶体管pg3和第四传输晶体管pg4可以连接到第二节点n2。

63.第一传输晶体管pg1的栅极和第三传输晶体管pg3的栅极可以连接到第一字线wla,第二传输晶体管pg2的栅极和第四传输晶体管pg4的栅极可以连接到第二字线wlb。

64.根据本公开的一示例实施方式,位单元bc可以包括连接到第一节点n1的第一传输晶体管pg1和第二传输晶体管pg2以及连接到第二节点n2的第三传输晶体管pg3和第四传输晶体管pg4以实现双端口。

65.具体地,通过使用第一字线wla、第一位线bla和第一互补位线blab,逻辑数据可以被写入到第一节点n1和第二节点n2中,或者存储在第一节点n1和第二节点n2中的逻辑数据可以被读取。类似地,通过使用第二字线wlb、第二位线blb和第二互补位线blbb,逻辑数据可以被写入到第一节点n1和第二节点n2中,或者存储在第一节点n1和第二节点n2中的逻辑数据可以被读取。位单元bc可以通过该双端口同时执行写入操作和读取操作。

66.图4和图5是根据示例实施方式的位单元的布局图。具体地,图4是用于说明参照图2和图3描述的位单元bc的晶体管的图,图5是用于说明提供在晶体管上的位线、字线和连接到字线的金属布线的图。在下文,将参照图2和图3进行描述。

67.参照图4,位单元bc可以包括第一传输晶体管区域pg1r、第二传输晶体管区域pg2r、第三传输晶体管区域pg3r、第四传输晶体管区域pg4r、第一上拉晶体管区域pu1r、第二上拉晶体管区域pu2r、第一下拉晶体管区域pd1r和第二下拉晶体管区域pd2r。

68.第一传输晶体管区域pg1r、第二传输晶体管区域pg2r、第三传输晶体管区域pg3r、第四传输晶体管区域pg4r、第一上拉晶体管区域pu1r、第二上拉晶体管区域pu2r、第一下拉晶体管区域pd1r和第二下拉晶体管区域pd2r可以是形成参照图3描述的第一传输晶体管pg1、第二传输晶体管pg2、第三传输晶体管pg3、第四传输晶体管pg4、第一上拉晶体管pu1、

第二上拉晶体管pu2、第一下拉晶体管pd1和第二下拉晶体管pd2的相应区域。

69.第一传输晶体管区域pg1r和第二传输晶体管区域pg2r可以在第二方向y上彼此相邻。第三传输晶体管区域pg3r和第四传输晶体管区域pg4r可以在第二方向y上彼此相邻。第一传输晶体管区域pg1r和第三传输晶体管区域pg3r可以在第一方向x上彼此间隔开。第二传输晶体管区域pg2r和第四传输晶体管区域pg4r可以在第一方向x上彼此间隔开。

70.第一上拉晶体管区域pu1r和第二上拉晶体管区域pu2r可以提供在第一传输晶体管区域pg1r和第三传输晶体管区域pg3r之间以及在第二传输晶体管区域pg2r和第四传输晶体管区域pg4r之间。具体地,第一上拉晶体管区域pu1r可以比第二上拉晶体管区域pu2r相对更靠近第二传输晶体管区域pg2r提供,并且第二上拉晶体管区域pu2r可以比第一上拉晶体管区域pu1r相对更靠近第三传输晶体管区域pg3r提供。第一上拉晶体管区域pu1r和第二上拉晶体管区域pu2r可以提供在沿第二方向y的不同轴线上。第一上拉晶体管区域pu1r和第二上拉晶体管区域pu2r可以在第一方向x上彼此相邻地提供且在其间具有预定间隔。

71.第一下拉晶体管区域pd1r可以提供在第二传输晶体管区域pg2r和第一上拉晶体管区域pu1r之间。第一下拉晶体管区域pd1r可以与第二传输晶体管区域pg2r和第一上拉晶体管区域pu1r间隔开。第一下拉晶体管区域pd1r的面积可以大于第二传输晶体管区域pg2r和第一上拉晶体管区域pu1r中的每个的面积。

72.第二下拉晶体管区域pd2r可以提供在第三传输晶体管区域pg3r和第二上拉晶体管区域pu2r之间。第二下拉晶体管区域pd2r可以与第三传输晶体管区域pg3r和第二上拉晶体管区域pu2r间隔开。第二下拉晶体管区域pd2r的面积可以大于第三传输晶体管区域pg3r和第二上拉晶体管区域pu2r中的每个的面积。

73.位单元bc可以包括多个有源图案rx。所述多个有源图案rx可以被提供为在第一方向x上彼此间隔开,并且每个可以在第二方向y上延伸。所述多个有源图案rx中的每个可以是其中形成n型晶体管的p型有源图案或其中形成p型晶体管的n型有源图案。

74.有源图案rx可以在第一方向x上具有各种宽度。例如,形成在第一上拉晶体管区域pu1r中的有源图案的宽度w1可以比形成在第一下拉晶体管区域pd1r中的有源图案的宽度w2窄。第一下拉晶体管区域pd1r和第二下拉晶体管区域pd2r中的每个可以包括在第一方向x上彼此间隔开的两个有源图案。

75.多个晶体管可以形成在所述多个有源图案rx中。晶体管可以是由以鳍的形式延伸的有源图案和栅电极形成的鳍式场效应晶体管(finfet),或者可以是由栅电极和彼此平行地延伸的多个纳米线形成的环绕栅极fet(gaafet),或者可以是由栅电极和彼此平行地延伸的多个纳米片形成的多桥沟道fet(mbcfet)。

76.晶体管可以包括叉片fet(forkfet),该叉片fet(forkfet)具有其中n型晶体管和p型晶体管相邻的结构,因为用于p型晶体管的纳米片和用于n型晶体管的纳米片通过电介质壁分隔开。晶体管可以包括垂直fet(vfet),该垂直fet包括在z轴方向上彼此间隔开的源极区和漏极区以及围绕沟道区的栅电极。除了场效应晶体管(fet)诸如互补fet(cfet)、负fet(ncfet)、碳纳米管(cnt)fet等之外,晶体管还可以包括双极结型晶体管和其它三维晶体管。

77.在此示例实施方式中,晶体管可以在下面被描述为gaafet,但是它们不限于此。将参照图11详细描述晶体管。

78.多个栅电极gt可以在第二方向y上彼此间隔开,并可以在第一方向x上延伸。因此,所述多个栅电极gt可以与所述多个有源图案rx部分地重叠。所述多个栅电极gt可以具有与形成在所述多个有源图案rx中的晶体管的栅极端相对应的结构,并且所述多个栅电极gt和所述多个有源图案rx可以形成多个晶体管。每一个位单元bc的两个栅电极gt可以彼此间隔开。

79.所述多个栅电极gt在第一方向x上延伸,但是可以是部分不连续的。电压可以通过栅极接触cb和栅极通路vb被施加到所述多个栅电极gt。当在附图中仅示出栅极通路vb时,可以省略提供在栅极通路vb下面的栅极接触cb。

80.所述多个栅电极gt可以包括导电材料。例如,所述多个栅电极gt可以包括半导体材料(例如掺杂的硅、掺杂的锗、掺杂的硅-锗等)、金属(例如钨、铝等)、金属化合物(例如金属硅化物等)、导电的金属氮化物(例如钛氮化物、钽氮化物、钨氮化物等)以及过渡金属(例如钛、钽等)中的至少一种。

81.gaa图案gaa可以提供在所述多个有源图案rx上。gaa图案gaa可以与栅电极gt部分地重叠。gaa图案gaa可以形成在所述多个有源图案rx与栅电极gt交叉的位置。gaa图案gaa可以包括多个纳米线或多个纳米片。在这种情况下,晶体管可以是包括多个纳米线或纳米片的gaafet。gaa图案gaa不限于图4所示的,可以形成比图示的数量更多数量的gaa图案gaa,并且平面形状可以形成为各种形状。

82.多个源极/漏极接触ca可以形成在所述多个有源图案rx上。源极/漏极接触ca可以在第一方向x上延伸。源极/漏极通路va可以形成在源极/漏极接触ca上。源极/漏极接触ca可以在第一方向x上延伸并可以是部分不连续的。源极/漏极接触ca可以提供在所述多个栅电极gt之间。因此,源极/漏极接触ca和所述多个栅电极gt可以不重叠。源极/漏极接触ca和源极/漏极通路va可以被电连接。源极/漏极接触ca和源极/漏极通路va可以将被提供为限定晶体管的源极区和漏极区的电压传输到该晶体管的源极/漏极区。

83.参照图5,位线bla和blb、互补位线blab和blbb、电源线pl以及字线wla和wlb可以提供在所述多个栅电极gt上。位线bla和blb、互补位线blab和blbb、电源线pl以及字线wla和wlb可以在第一方向x上彼此间隔开,并可以在第二方向y上延伸。根据一示例实施方式,如以上参照图2所述,字线wla和wlb可以包括切割区域m1 cut。

84.金属布线ml1和ml2可以提供在位线bla和blb上。金属布线ml1和ml2可以在第二方向y上彼此间隔开并可以在第一方向x上延伸。金属布线ml1和ml2可以在第三方向z上与所述多个栅电极gt重叠。因此,在附图中可以省略栅电极gt。

85.为了便于图示,第一通路v1被示出,尽管第一通路v1位于金属布线ml1和ml2下面。金属布线ml1和ml2可以使用第一通路v1电连接到字线wla和wlb。第一金属布线ml1可以通过第一通路v1连接到第一字线wla,第二金属布线m2可以通过第一通路v1连接到第二字线wlb。

86.在下文,为了帮助理解图4和图5所示的集成电路100,将描述沿着图5的线c-c'的堆叠结构。

87.图6是沿着图5的线c-c'截取的剖视图。具体地,作为用于说明图4和图5的堆叠结构的示意图,为了便于描述,省略了晶体管,并且任意地示出栅电极gt、接触ca和cb、通路va、vb和v1、第一字线wla、第二位线blb和第一金属布线ml1的尺寸。因此,图6可以与实际位

单元bc的剖视图不同。

88.参照图6,连接到晶体管的栅电极gt的栅极接触cb和连接到该晶体管的源极/漏极区的源极/漏极接触ca可以形成在第一层f1上。第一层f1可以被称为“接触层”或“m0层”。位单元bc和第一层f1可以在工艺线前端(feol)工艺中形成。

89.连接到栅极接触cb的栅极通路vb和连接到源极/漏极接触ca的源极/漏极通路va可以形成在第二层f2中。第二层f2可以被称为“接触通路层”或“v0层”。

90.第一字线wla和第二位线blb可以形成在第三层f3上。如上所述,位线对bp、互补位线对bbp、电源线组pg以及字线wla和wlb可以形成在同一层上,例如,可以形成在第三层f3上。第三层f3可以被称为“第一布线层”或“m1层”。位线对bp、互补位线对bbp、电源线组pg以及字线wla和wlb可以被称为“第一布线”。

91.第一通路v1可以形成在第四层f4中。第一通路v1可以连接到第一字线wla。第四层可以被称为“第一通路层”。

92.第一金属布线ml1可以形成在第五层f5上。根据一示例实施方式,如上所述,第二金属布线ml2可以形成在与第一金属布线ml1相同的布线层上,例如,第二金属布线ml2也可以形成在第五层f5上。第五层f5可以被称为“第二布线层”或“m2层”。第一金属布线ml1和第二金属布线ml2可以被称为“第二布线”。

93.尽管图6示出第一层f1至第五层f5,但是本公开不限于此,因此,根据另一示例实施方式,第二通路层、第三布线层、第三通路层、第四布线层等可以进一步形成在第五层f5上。第二层f2至第五层f5可以在工艺线后端(beol)工艺中形成。接触面积可以从第二层f2到第五层f5减小。

94.图7是根据另一示例实施方式的位单元的布局图。为方便起见,省略与图2中的图示重复的描述。

95.参照图7,集成电路200还可以包括虚设线dm。

96.虚设线dm可以形成为在第二方向y上延伸。虚设线dm可以提供在位线对bp和电源线组pg之间,和/或可以提供在互补位线对bbp和电源线组pg之间。

97.虚设线dm可以电独立于位单元bc。虚设线dm可以是电独立于位单元bc的电源线。也就是,虚设线dm不电连接到位单元bc,但是可以电连接到在第二方向y上与位单元bc相邻的另一位单元。根据一实施方式,虚设线dm可以电连接到在第二方向y上以预定距离彼此间隔开的位单元bc和另一些位单元。因此,虚设线dm可以将电源电压vdd或接地电压vss施加到另一些位单元。根据一实施方式,电源电压vdd或接地电压vss被施加到虚设线dm,但是电压可以不被提供到除了位单元bc之外的位单元,以及可选地,可以没有电压被施加。

98.集成电路200可以包括各种数量的虚设线dm。尽管图7示出包括两条虚设线dm,但是本公开不限于此,因此,根据另一示例实施方式,可以包括一条虚设线或者可以包括两条或更多条虚设线dm。根据一示例实施方式,一条或更多条虚设线dm可以提供在位线对bp和电源线组pg之间。

99.在此示例实施方式中,通过包括提供在位线对bp和电源线组pg之间和/或提供在互补位线对bbp和电源线组pg之间的至少一条虚设线dm,第二位线blb和第二互补位线blbb中的至少一条可以被屏蔽。因此,可以最小化或防止位线对bp和互补位线对bbp的耦合,并且可以提供执行稳定操作的集成电路200。

100.图8是根据另一示例实施方式的位单元的布局图。为了方便起见,省略与图2和图7中的图示重复的描述。

101.参照图8,集成电路300还可以包括边界虚设线bdm。

102.边界虚设线bdm可以形成为在第二方向y上延伸。边界虚设线bdm可以提供在位单元bc和在第一方向x上相邻的另一位单元之间的边界处。因此,边界虚设线bdm可以提供在位单元bc的第一位线bla和在第一方向x上与位单元bc相邻的另一位单元的第一互补位线blab之间。

103.边界虚设线bdm可以电独立于位单元bc。边界虚设线bdm可以是电独立于位单元bc的电源线。也就是,边界虚设线bdm不电连接到位单元bc,但是可以电连接到在第二方向y上与位单元bc相邻的另一位单元。根据一实施方式,边界虚设线bdm可以电连接到在第二方向y上以预定距离彼此间隔开的位单元bc和另一些位单元。因此,边界虚设线bdm可以将电源电压vdd或接地电压vss施加到另一些位单元。根据一实施方式,电源电压vdd或接地电压vss被施加到边界虚设线bdm,但是电压可以不被提供到除了位单元bc之外的位单元,以及可选地,可以没有电压被施加。

104.集成电路300可以包括可变数量的边界虚设线bdm。在图8中,示出包括两条边界虚设线bdm,但是本公开不限于此,因此,根据另一示例实施方式,集成电路可以仅包括一条边界虚设线,或者集成电路可以包括两条或更多条边界虚设线。根据一示例实施方式,一条或更多条边界虚设线bdm可以提供在位单元bc之间。

105.在此示例实施方式中,通过包括提供在位单元bc和在第一方向x上相邻的另一位单元之间的边界处的至少一条边界虚设线bdm,第一位线bla和第一互补位线blab中的至少一条可以被屏蔽。因此,可以最小化或防止位线对bp和互补位线对bbp的耦合,并且可以提供执行稳定操作的集成电路300。

106.图9是根据另一示例实施方式的位单元的布局图。具体地,图9是用于说明图8的集成电路300的图。在下文,将参照图4至图8进行描述。

107.参照图9,集成电路300可以包括位单元bc。位单元bc可以与以上参照图4和图5描述的位单元bc相同。根据一示例实施方式,可以如图5所示省略虚设线dm和边界虚设线bdm。

108.集成电路300还可以包括虚设线dm和边界虚设线bdm。虚设线dm和边界虚设线bdm可以电独立于位单元bc。也就是,虚设线dm和边界虚设线bdm仅在位单元bc上在第二方向y上延伸,并且位单元bc可以不包括连接到虚设线dm和边界虚设线bdm的接触或通路。

109.虚设线dm和边界虚设线bdm可以形成在与位线bla、blb、blab和blbb、字线wla和wlb以及电源线pl相同的布线层上。参照图6,虚设线dm和边界虚设线bdm可以形成在第三层f3中。当集成电路300还包括虚设线dm和边界虚设线bdm时,除了位线对bp、互补位线对bbp、电源线组pg以及字线wla和wlb之外,“第一布线”还可以包括虚设线dm和边界虚设线bdm。

110.图10是根据另一示例实施方式的位单元的布局图。具体地,图10是包括多个位单元c1、c2、c3和c4的集成电路400的布局图。将参照图2至图9进行描述。

111.参照图10,集成电路400可以包括多个位单元c1、c2、c3和c4。所述多个位单元c1、c2、c3和c4可以被提供为彼此相邻。第一位单元c1可以在第一方向x上与第二位单元c2相邻并可以在第二方向y上与第三位单元c3相邻。第四位单元c4可以在第二方向y上与第二位单元c2相邻并可以在第一方向x上与第三位单元c3相邻。

112.所述多个位单元c1、c2、c3和c4中的每个可以包括有源图案和形成在有源图案中的晶体管,如以上参照图3和图4所述的。由于有源图案可以在第二方向y上延伸,所以在第二方向y上相邻的位单元(例如第一位单元c1和第三位单元c3)可以共用有源图案。

113.如以上参照图2所述,所述多个位单元c1、c2、c3和c4可以连接到位线对bp1和bp2、互补位线对bbp1和bbp2、电源线组pg1和gp2以及字线wla、wlb、wlc和wld。字线wla、wlb、wlc和wld可以提供在位线对bp1或bp2之间或在互补位线对bbp1或bbp2之间。因此,位线对bp1和bp2或互补位线对bbp1和bbp2可以被字线屏蔽。

114.在第二方向y上相邻的位单元可以共用位线对bp1和bp2以及互补位线对bbp1和bbp2。例如,第一位单元c1和第三位单元c3可以共用第一位线对bp1和第一互补位线对bbp1,第二位单元c2和第四位单元c4可以共用第二位线对bp2和第二互补位线对bbp2。也就是,第一位单元c1和第三位单元c3可以都连接到第一位线对bp1和第一互补位线对bbp1,第二位单元c2和第四位单元c4可以都连接到第二位线对bp2和第二互补位线对bbp2。

115.第一金属对mp1可以包括第一金属线mla和第二金属线mlb,第二金属对mp2可以包括第三金属线mlc和第四金属线mld。在第一方向x上相邻的位单元可以共用金属对mp1和mp2。例如,第一位单元c1和第二位单元c2可以共用第一金属对mp1,第三位单元c3和第四位单元c4可以共用第二金属对mp2。也就是,第一位单元c1和第二位单元c2中的每个可以连接到第一金属对mp1,第三位单元c3和第四位单元c4中的每个可以连接到第二金属对mp2。

116.金属对mp1和mp2可以通过第一通路v1连接到字线wla、wlb、wlc和wld。字线wla、wlb、wlc和wld可以由切割区域m1 cut分隔开。例如,第一位单元c1的第一字线wla和第三位单元c3的第三字线wlc可以被形成在第三位单元c3中的切割区域m1 cut分隔开。因此,不同的电压可以通过第一金属布线mla和第三金属布线mlc施加到第一字线wla和第三字线wlc。切割区域m1 cut可以形成在沿第一方向x彼此相邻的位单元中的相同位置。例如,第一位单元c1和第二位单元c2可以包括形成在相同位置的切割区域m1 cut。

117.也就是,在第二方向y上相邻的位单元可以共用位线对bp1和bp2以及互补位线对bbp1和bbp2,并且在第一方向x上相邻的位单元可以共用金属对mp1和mp2。可以通过位线对bp1和bp2、互补位线对bbp1和bbp2以及金属对mp1和mp2对所述多个位单元c1、c2、c3和c4执行写入操作或读取操作。

118.如以上在图7和图8中所述的,集成电路400还可以包括在第二方向y上与所述多个位单元c1、c2、c3和c4交叉的虚设线dm和边界虚设线bdm。

119.至少一条虚设线dm可以提供在电源线组pg1和pg2与位线对bp1和bp2之间,和/或可以提供在电源线组pg1和pg2与互补位线对bbp1和bbp2之间。

120.至少一条边界虚设线bdm可以提供在沿第一方向x相邻的位单元之间的边界处。至少一条边界虚设线bdm可以提供在连接到不同位单元的位线之间。例如,至少一条边界虚设线bdm可以提供在第一位单元c1的第一互补位线blab和第二位单元c2的第一位线bla之间。

121.根据一实施方式,虚设线dm和边界虚设线bdm可以被省略或者可以提供得比图10所示的更多。

122.图11是根据示例实施方式的位单元的剖视图。具体地,图11的集成电路500可以包括gaafet,并且gaafet可以包括mbcfet。图11是用于说明形成在图4的有源图案rx中的gaafet的图,具体地,是用于说明mbcfet的图。因此,尽管在图11中示出纳米片,但是本公开

不限于此,因此,根据另一示例实施方式,集成电路可以被实现为包括纳米线。图11是沿着图4的线a-a'和b-b'截取的剖视图,并且省略图4的接触ca和cb以及通路va和vb。

123.参照图11,集成电路500可以包括从半导体基板sub突出并在第二方向y上延伸的鳍型有源区fa。半导体基板sub可以包括导电区,例如掺有杂质的阱或掺有杂质的结构。鳍型有源区fa可以对应于图4的有源图案rx。

124.限定鳍型有源区fa的沟槽tr可以形成在半导体基板sub中。沟槽tr可以填充有浅沟槽隔离(sti)膜i1。sti膜i1可以包括绝缘材料。

125.纳米片堆叠结构nss可以与鳍型有源区fa的上表面top间隔开。纳米片堆叠结构nss可以在与鳍型有源区fa的上表面top间隔开的位置面对鳍型有源区fa的上表面top。纳米片堆叠结构nss可以对应于图4的gaa图案gaa。

126.纳米片堆叠结构nss可以包括平行于鳍型有源区fa的上表面top延伸的纳米片n1、n2和n3。纳米片n1、n2和n3可以依次堆叠在鳍型有源区fa的上表面top上,并且每个可以具有沟道区。纳米片n1、n2和n3可以由与半导体基板sub的材料相同的材料制成。

127.在此示例实施方式中,尽管示出一个纳米片堆叠结构nss和栅电极gt形成在一个鳍型有源区fa上并且三个纳米片n1、n2和n3堆叠在鳍型有源区fa上,但是本公开不限于此。此外,纳米片堆叠结构nss的截面形状被示出为矩形,但是不限于此,并且纳米片堆叠结构nss可以具有各种截面形状,这取决于鳍型有源区fa的截面形状和栅电极gt的截面形状。

128.栅电极gt可以形成在鳍型有源区fa上。栅电极gt可以在第一方向x上延伸。栅电极gt可以覆盖纳米片堆叠结构nss。栅电极gt可以形成为围绕纳米片n1、n2和n3的至少一部分。

129.源极/漏极区sd可以形成在鳍型有源区fa上。源极/漏极区sd可以连接到相邻纳米片n1、n2和n3的一端。

130.栅电极gt可以包括覆盖纳米片堆叠结构nss的上表面的主栅电极gtm和形成在鳍型有源区fa和纳米片n1、n2和n3之间的子栅电极gts。主栅电极gtm和子栅电极gts可以连接到彼此。主栅电极gtm的厚度可以大于每个子栅电极gts的厚度。

131.子栅电极gts当中的最靠近鳍型有源区fa提供的子栅电极的两个侧壁可以覆盖有覆盖鳍型有源区fa的上表面top的缓冲层bl。缓冲层bl可以包括与鳍型有源区fa的材料不同的材料。

132.栅极电介质膜gd可以形成在纳米片堆叠结构nss和栅电极gt之间。栅极电介质膜gd可以覆盖多个纳米片n1、n2和n3中的每个的表面。栅极电介质膜gd可以包括高k材料。

133.第一绝缘间隔物is1可以形成为覆盖子栅电极gts的侧壁中的至少一些。第一绝缘间隔物is1可以在子栅电极gts和源极/漏极区sd之间。第一绝缘间隔物is1可以在纳米片n1、n2和n3之间。

134.绝缘衬垫il、第二绝缘间隔物is2和保护膜pf可以形成在纳米片堆叠结构nss上。绝缘衬垫il、第二绝缘间隔物is2和保护膜pf可以覆盖主栅电极gtm的侧壁。绝缘衬垫il可以形成在栅电极gt的侧壁上并可以部分地覆盖纳米片n1、n2和n3当中的提供在最高水平处的纳米片n3的上表面。第二绝缘间隔物is2可以形成在绝缘衬垫il上,并且保护膜pf可以形成在第二绝缘间隔物is2上。在一些实施方式中,可以省略保护膜pf。

135.可以在栅电极gt上形成层间绝缘膜i2。层间绝缘膜i2可以包括硅氧化物。穿过层

间绝缘膜i2和保护膜pf连接到源极/漏极区sd的接触插塞cp可以形成在源极/漏极区sd上。接触插塞cp可以由金属、导电的金属氮化物或其组合形成。

136.图12是示出根据一示例实施方式的设计集成电路的方法的示例的流程图。该集成电路可以是以上参照图1至图11描述的集成电路100至500之一。在下文,将参照图1至图11进行描述。

137.参照图12,图12的设计方法可以由包括执行一系列指令的至少一个处理器的计算系统来执行。如图12所示,设计集成电路的方法可以包括操作s10、s20和s30。

138.在操作s10中,可以获得输入数据。输入数据可以是定义集成电路的数据,并可以包括例如图14的网表d13并且稍后参照图14进行描述。输入数据可以包括关于集成电路中包括的位单元和位单元的连接的信息。

139.在操作s20中,可以执行布局和布线(p&r)。p&r可以基于图14的位单元库d12执行并且稍后参照图14进行描述。操作s20可以包括多个操作s21、s22和s23。标准单元库(d15)用于设计其中设置多个标准单元的半导体集成电路,标准单元库(d15)可以包括关于所述多个标准单元的特性信息。

140.在操作s21中,位单元可以布置在预定位置。位单元可以是dpsram单元。

141.在操作s22中,位线、字线和电源线可以布置在位单元上。位线、字线和电源线可以布置在第一布线层上。字线可以通过被提供在位线之间来屏蔽位线。虚设线和边界虚设线可以进一步布置在位单元上。虚设线可以提供在位线和电源线之间,边界虚设线可以提供在包括在不同位单元中的位线之间。

142.在操作s23中,金属布线可以布置在位线、字线和电源线上。金属布线可以提供在第二布线层上。金属布线可以通过通路电连接到字线。

143.在操作s30中,可以生成输出数据。输出数据可以指限定集成电路的布局的数据。例如,它可以包括稍后参照图14描述的图14的布局数据d14。

144.图13是示出根据示例实施方式的设计集成电路的方法的示例的流程图。具体地,图13是说明图12的操作s22的流程图。在下文,将参照图10和图12进行描述。

145.如图13所示,操作s22中的布置位线、字线和电源线的操作可以包括操作s22_1、s22_2、s22_3和s22_4。根据一示例实施方式,可以并行地执行操作s22_1、s22_2、s22_3和s22_4。

146.在操作s22_1中,位线对bp和互补位线对bbp可以布置在位单元上。位线对bp和互补位线对bbp可以布置为在第一方向x上彼此间隔开。包括多条电源线pl的电源线组pg可以提供在位线对bp和互补位线对bbp之间。

147.在操作s22_2中,字线wla和wlb可以布置在位单元上。字线wla和wlb可以提供在位线对bp之间和在互补位线对bbp之间。

148.在操作s22_3中,至少一条虚设线dm可以布置在位单元上。该至少一条虚设线dm可以提供在位线对bp和电源线组pg之间和/或可以提供在互补位线对bbp和电源线组pg之间。在一些实施方式中,可以省略操作s22_3。

149.在操作s22_4中,边界虚设线bdm可以布置在位单元上。边界虚设线bdm可以提供在沿第一方向x彼此相邻的不同位单元之间的边界处。边界虚设线bdm可以提供在连接到不同位单元的位线之间。在一些实施方式中,可以省略操作s22_4。

150.在操作s22_4之后,可以执行图12的操作s30。

151.图14是示出根据示例实施方式的制造集成电路的方法的示例的流程图。该集成电路可以是以上参照图1至图11描述的集成电路100至500之一。在下文,将参照图1至图11进行描述。

152.参照图14,位单元库d12可以包括关于包括在图1的存储单元块11中的位单元12的信息。例如,位单元库d12可以包括位单元12的布局信息等。位单元库d12可以包括限定位单元12的布局的数据d12_1、d12_2等。例如,位单元库d12可以包括限定以上参照图2至图10描述的集成电路100至400的布局的数据。

153.在操作s110中,可以执行用于从rtl数据d11生成网表数据d13的逻辑综合操作。例如,半导体设计工具参考位单元库d12并从以硬件描述语言(hdl)编写的rtl数据d11进行逻辑综合,以生成包含比特流或网表的网表数据d13。hdl可以包括vhsic硬件描述语言(vhdl)和verilog。在逻辑综合过程中,可以参考位单元库d12的信息。

154.在操作s120中,可以执行用于从网表数据d13生成布局数据d14的p&r操作。操作s120可以包括多个操作s121、s122和s123。操作s121和s122可以对应于图12的操作s20。

155.在操作s121中,可以执行布置位单元的操作。例如,半导体设计工具(例如p&r工具)可以从网表数据d13参考位单元库d12放置多个位单元。

156.在操作s122中,可以执行生成互连的操作。互连可以包括包含位线、互补位线、电源线、字线、虚设线和边界虚设线的第一布线,并且可以包括包含电连接到字线的金属布线的第二布线。根据一实施方式,可以省略虚设线和边界虚设线。

157.互连可以被形成为使得字线提供在位线之间和在互补位线之间。此外,可以在位线和电源线之间提供虚设线,或者可以在相邻的位单元之间的边界处在位线之间提供边界虚设线。通过互连操作,电信号可以被传输到位单元。可以形成至少一个接触和至少一个通路以用于互连。

158.在操作s123中,可以执行生成布局数据d14的操作。布局数据d14可以包括位单元和互连的几何信息。布局数据d14可以具有诸如gdsii的格式。布局数据d14可以对应于图12的输出数据。

159.在操作s130中,可以通过对布局数据d14执行光学邻近校正(opc)来确定在掩模上的图案。也就是,具有期望形状的图案可以通过在布局数据d14中校正由光的特性引起的诸如折射的变形现象来形成。在一些实施方式中,可以在操作s130中有限地修改集成电路的布局。通过这样,可以优化集成电路的结构。操作s130可以被称为设计修饰(design polishing)。

160.在操作s140中,可以执行制造掩模的操作。为了形成在操作s130中确定的图案,可以制造至少一个掩模。掩模可以包括光掩模。

161.在操作s150中,可以执行制造集成电路的操作。例如,集成电路可以通过使用在操作s140中制造的所述至少一个掩模对多个层进行图案化来制造。操作s150可以包括多个操作s151和s152。

162.在操作s151中,可以执行工艺线前端(feol)工艺。feol可以指在基板上形成各个元件。各个元件可以包括晶体管、电容器、电阻器等。feol工艺包括晶片的平坦化操作、清洁晶片的操作、形成沟槽的操作、形成阱的操作、形成栅极线的操作以及形成源极和漏极的操

作。例如,操作s151可以对应于图12的操作s21和s22的至少一部分。

163.在操作s152中,可以执行工艺线后端(beol)工艺。beol可以指互连各个元件的工艺。例如,beol工艺可以包括栅极、源极和漏极区的硅化操作、添加电介质的操作、平坦化操作、形成孔的操作、添加金属层的操作、形成通路的操作、形成钝化层的操作等。例如,操作s152可以对应于图12的操作s22和操作s23的至少一部分。

164.在操作s152之后,封装的集成电路ic可以用作各种应用中的部件。

165.图15是示出根据一示例实施方式的片上系统(soc)的框图。

166.soc 1000是集成电路并可以包括根据一示例实施方式的集成电路。soc1000实现复杂的功能块(诸如在一个芯片中执行各种功能的知识产权(ip)),并且根据示例实施方式布置的有源区、标准单元和位单元可以被包括在soc1000的各个功能块中。

167.参照图15,soc 1000可以包括调制解调器1200、显示控制器1300、存储器1400、外部存储器控制器1500、中央处理单元(cpu)1600、事务单元1700、电源管理集成电路(pmic)1800和图形处理单元(gpu)1900,并且soc 1000的每个功能块可以通过系统总线201彼此通信。

168.可控制soc 1000的整体操作的cpu 1600可以控制其它功能块(即调制解调器1200、显示控制器1300、存储器1400、外部存储器控制器1500、事务单元1700、pmic 1800和gpu 1900)的操作。调制解调器1200可以解调从soc 1000的外部接收的信号,或者可以调制在soc 1000内部产生的信号并将调制后的信号发送到外部。外部存储器控制器1500可以控制将数据发送到连接到soc 1000的外部集成电路和从连接到soc 1000的外部集成电路接收数据的操作。例如,存储在外部集成电路中的程序和/或数据可以在外部存储器控制器1500的控制下被提供到cpu 1600或gpu 1900。gpu 1900可以执行与图形处理相关的程序指令。gpu 1900可以通过外部存储器控制器1500接收图形数据,并可以通过外部存储器控制器1500将由gpu 1900处理的图形数据发送到soc 1000的外部。事务单元1700可以监控每个功能块的数据事务,并且pmic 1800可以根据事务单元1700的控制来控制提供给每个功能块的电力。显示控制器1300可以通过控制在soc 1000外部的显示器(或显示装置)而将在soc 1000内部产生的数据发送到显示器。

169.存储器1400可以包括非易失性存储器,诸如电可擦除可编程只读存储器(eeprom)、闪存、相变随机存取存储器(pram)、电阻随机存取存储器(rram)、纳米浮置栅极存储器(nfgm)、聚合物随机存取存储器(poram)、磁随机存取存储器(mram)、铁电随机存取存储器(fram)等,并且可以包括易失性存储器,诸如动态随机存取存储器(dram)、静态随机存取存储器(sram)、移动dram、双倍数据速率同步动态随机存取存储器(ddr sdram)、低功率ddr(lpddr)sdram、图形ddr(gddr)sdram、rambus动态随机存取存储器(rdram)等。

170.图16是示出根据一示例实施方式的包括存储程序的存储器的计算系统的框图。根据示例实施方式,包括在用于制造集成电路的方法(例如图14的方法)中的操作和包括在设计集成电路的方法(例如图12和图13的方法)中的操作中的至少一些可以由计算系统2000执行。

171.参照图16,计算系统2000可以是诸如桌面计算机、工作站、服务器等的固定计算系统,并且可以是诸如膝上型计算机的便携式计算系统。

172.计算系统2000可以包括处理器2100、输入/输出(i/o)装置2200、网络接口2300、随

机存取存储器(ram)2400、只读存储器(rom)2500和存储装置2600。处理器2100、i/o装置2200、网络接口2300、ram 2400、rom 2500和存储装置2600可以连接到总线2700,并可以通过总线2700彼此通信。

173.处理器2100可以被称为处理单元,并且例如可以包括能够执行任意指令集(例如,英特尔架构-32(ia-32)、64位扩展ia-32、x86-64、powerpc、sparc、mips、arm、ia-64等)的至少一个内核,诸如微处理器、应用处理器(ap)、数字信号处理器(dsp)和图形处理单元(gpu)。例如,处理器2100可以通过总线2700访问存储器(即ram 2400或者rom 2500),并可以执行存储在ram 2400或rom 2500中的指令。

174.ram 2400可以存储程序2410或其至少一部分以用于制造根据示例实施方式的集成电路,并且程序2410可以使处理器2100执行制造集成电路的方法中包括的操作和设计集成电路的方法中包括的操作中的至少一些。也就是,程序2410可以包括可由处理器2100执行的多个指令,并且包括在程序2410中的所述多个指令可以使处理器2100执行例如包括在以上参照图12至图14描述的流程图中的操作中的至少一些。

175.即使供应到计算系统2000的电力被切断,存储装置2600也不会丢失存储的数据。例如,存储装置2600可以包括非易失性集成电路,并可以包括诸如磁带、光盘或磁盘的存储介质。此外,存储装置2600可以从计算系统2000可移除。存储装置2600可以存储根据一示例实施方式的程序2410,并且在程序2410被处理器2100执行之前,程序2410或其至少一部分可以从存储装置2600加载到ram 2400中。可选地,存储装置2600可以存储以程序语言编写的文件,并且通过编译器等从文件生成的程序2410或其至少一部分可以被加载到ram 2400中。此外,存储装置2600可以存储数据库(db)2610,并且数据库2610可以包括设计集成电路所需的信息,例如图14的位单元库d12。

176.存储装置2600可以存储将由处理器2100处理的数据或已由处理器2100处理的数据。也就是,处理器2100可以通过根据程序2410处理存储在存储装置2600中的数据来生成数据,并可以将生成的数据存储在存储装置2600中。例如,存储装置2600可以存储图14的rtl数据d11、网表数据d13和/或布局数据d14。

177.i/o装置2200可以包括诸如键盘和点击装置的输入装置,并可以包括诸如显示装置和打印机的输出装置。例如,通过i/o装置2200,用户可以触发通过处理器2100执行程序2410,输入图14的rtl数据d11和/或网表数据d13,并检查图14的布局数据d14。

178.网络接口2300可以提供对计算系统2000外部的网络的访问。例如,网络可以包括多个计算系统和通信链路,并且通信链路可以包括有线链路、光链路、无线链路或任何其它类型的链路。

179.尽管已经具体示出和描述了示例实施方式,但是将理解,在不脱离所附权利要求的精神和范围的情况下,可以在其中进行形式和细节上的各种改变。

180.本技术基于2021年6月30日在韩国知识产权局提交的韩国专利申请第10-2021-0085765号并要求其优先权,该韩国专利申请的公开内容通过引用整体地结合于此。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1