存储器单元、阵列电路结构及数据处理方法

本公开至少一实施例涉及一种存储器单元、阵列电路结构及数据处理方法。

背景技术:

1、近年来,基于忆阻器阵列利用物理定律实现模拟计算成为新兴的研究热点。忆阻器是一种新型的微纳电子器件,其电阻状态可以通过外在电压激励进行调节。基于忆阻器的神经形态计算突破了传统计算设备的冯诺依曼架构,计算和存储在相同的地方完成,减少了数据搬运的时间,计算时所需能效较高、功耗较低、面积较小。

技术实现思路

1、本公开的实施例提供一种存储器单元、阵列电路结构及数据处理方法。

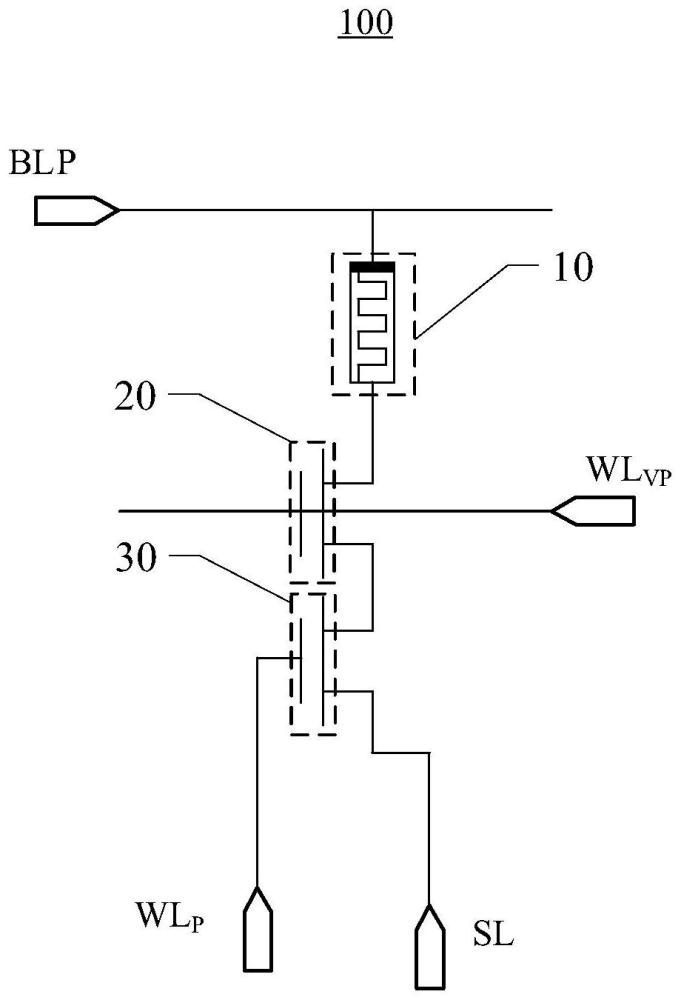

2、本公开的实施例提供一种存储器单元,包括:至少一个阻变器件和至少两个开关元件,每个开关元件包括第一极、第二极以及控制极,其中,所述至少一个阻变器件包括第一阻变器件,所述至少两个开关元件包括第一开关元件以及第二开关元件,所述第一阻变器件的第一端与第一位线端连接;所述第一开关元件的第一极与所述第一阻变器件的第二端连接,所述第一开关元件的第二极与所述第二开关元件的第一极连接,所述第一开关元件的控制极与第一字线端连接;所述第二开关元件的第二极与源线端连接,所述第二开关元件的控制极与选择控制端连接。

3、例如,在本公开的一些实施例中,所述至少一个阻变器件还包括第二阻变器件,所述至少两个开关元件还包括第三开关元件和第四开关元件,所述第二阻变器件的第一端与第二位线端连接;所述第三开关元件的第一极与所述第二阻变器件的第二端连接,所述第三开关元件的第二极与所述第四开关元件的第一极连接,所述第三开关元件的控制极与第二字线端连接;所述第四开关元件的第二极与所述源线端连接,所述第四开关元件的控制极与所述选择控制端连接。

4、例如,在本公开的一些实施例中,所述至少一个阻变器件还包括第三阻变器件,所述至少两个开关元件还包括第五开关元件,所述第三阻变器件的第一端与第二位线端连接;所述第五开关元件的第一极与所述第三阻变器件的第二端连接,所述第五开关元件的第二极与所述源线端连接,所述第五开关元件的控制极与第二字线端连接。

5、例如,在本公开的一些实施例中,所述阻变器件为阻变式存储器(rram)、flash、sram、dram、pcram、mram、feram中的任一种;所述开关元件为晶体管。

6、本公开的实施例提供一种阵列电路结构,包括:多个阵列排布为m行n列的如上述任一项所述的存储器单元;多条信号控制线,包括:m条第一位线、m条第一字线、n条选择控制线以及n条源线,m和n为正整数;所述m条第一位线和所述m条第一字线分别与所述m行一一对应,所述n条选择控制线和所述n条源线分别与所述n列一一对应,每条第一位线与所述第一位线对应的一行存储器单元中的第一位线端连接,每条第一字线与所述第一字线对应的一行存储器单元中的第一字线端连接,每条选择控制线与所述选择控制线对应的一列存储器单元中的选择控制端连接,每条源线与所述源线对应的一列存储器单元中的源线端连接。

7、例如,在本公开的一些实施例中,在所述存储器单元还包括所述第二阻变器件、所述第三开关元件以及所述第四开关元件的情况下,所述第二阻变器件的第一端与第二位线端连接;所述第三开关元件的控制极与第二字线端连接;所述多条信号控制线还包括m条第二位线和m条第二字线,所述m条第二位线和所述m条第二字线分别与所述m行一一对应,每条第二位线与所述第二位线对应的一行存储器单元中的第二位线端连接,每条第二字线与所述第二字线对应的一行存储器单元中的第二字线端连接。

8、例如,在本公开的一些实施例中,在所述阵列电路结构还包括所述第三阻变器件和所述第五开关元件的情况下,所述第三阻变器件的第一端与第二位线端连接;所述第五开关元件的控制极与第二字线端连接;所述多条信号控制线还包括m条第二位线和m条第二字线,所述m条第二位线和所述m条第二字线与分别所述m行一一对应,每条第二位线与所述第二位线对应的一行存储器单元中的第二位线端连接,每条第二字线与所述第二字线对应的一行存储器单元中的第二字线端分别连接。

9、本公开的实施例还提供一种数据处理方法,包括:至少通过所述m条第一字线、所述n条选择控制线选择所述阵列电路结构中的所述至少一个存储器单元;对所述至少一个存储器单元执行数据处理操作,以利用所述至少一个存储器单元执行相应的数据处理。

10、例如,在本公开的一些实施例中,所述多个存储器单元中的每个在接收到对应的第一字线所施加的开启信号以及对应的选择控制线所施加的开启信号时被打开,所述至少通过所述m条第一字线、所述n条选择控制线选择所述阵列电路结构中的所述至少一个存储器单元,包括:针对所述至少一个存储器单元中的任一存储器单元:确定所述任一存储器单元所在的目标行及目标列;通过所述目标行对应的第一字线向所述目标行施加开启信号;通过所述目标列对应的选择控制线向所述目标列施加开启信号,以选择所述任一存储器单元。

11、例如,在本公开的一些实施例中,在所述多条信号控制线还包括m条第二字线的情况下,所述多个存储器单元中的每个在接收到对应的第一字线和第二字线所施加的开启信号以及对应的选择控制线所施加的开启信号时被打开,所述至少通过所述m条第一字线、所述n条选择控制线选择所述阵列电路结构中的所述至少一个存储器单元,包括:针对所述至少一个存储器单元中的任一存储器单元:确定所述任一存储器单元所在的目标行及目标列;通过所述目标行对应的第一字线向所述目标行施加开启信号;通过所述目标列对应的选择控制线向所述目标列施加开启信号;通过所述目标行对应的第二字线向所述目标行施加开启信号,以选择所述任一存储器单元。

12、例如,在本公开的一些实施例中,所述多个存储器单元中的每个在接收对应的第一字线所施加的开启信号以及对应的选择控制线所施加的开启信号时被打开,所述至少一个存储器单元排列为w行u列的阵列形式,w为正整数且小于等于m,u为正整数且小于等于n,所述至少通过所述m条第一字线、所述n条选择控制线选择所述阵列电路结构中的所述至少一个存储器单元,包括:通过排列为所述阵列形式的所述w行存储器单元对应的w条第一字线分别向所述w行施加开启信号,通过排列为所述阵列形式的所述u列存储器单元对应的u条选择控制线分别向所述u列施加开启信号,以选择所述至少一个存储器单元。

13、例如,在本公开的一些实施例中,在所述多条信号控制线还包括m条第二字线的情况下,所述多个存储器单元中的每个在接收对应的第一字线和第二字线所施加的开启信号以及对应的选择控制线所施加的开启信号时被打开,所述至少一个存储器单元排列为w行u列的阵列形式,w为正整数且小于等于m,u为正整数且小于等于n,所述至少通过所述m条第一字线、所述n条选择控制线选择所述阵列电路结构中的所述至少一个存储器单元,包括:通过排列为所述阵列形式的所述w行存储器单元对应的w条第一字线分别向所述w行施加开启信号;通过排列为所述阵列形式的所述u列存储器单元对应的u条选择控制线分别向所述u列施加开启信号;通过排列为所述阵列形式的所述w行存储器单元对应的w条第二字线分别向所述w行施加开启信号,以选择所述至少一个存储器单元。

14、例如,在本公开的一些实施例中,所述对所述至少一个存储器单元执行数据处理操作,以利用所述至少一个存储器单元执行相应的数据处理,包括:对所选择的所述至少一个存储器单元执行置位操作或复位操作;其中,所述置位操作包括使得所述阻变器件从第一阻态变为第二阻态,所述复位操作包括使得所述阻变器件从所述第二阻态变为所述第一阻态,所述阻变器件在所述第一阻态时的阻值大于在所述第二阻态时的阻值。

15、例如,在本公开的一些实施例中,所述对所述至少一个存储器单元执行数据处理操作,以利用所述至少一个存储器单元执行相应的数据处理,还包括:对所选择的所述至少一个存储器单元执行读取操作;其中,所述读取操作包括:向所述至少一个存储器单元对应的位线施加读取电压,读取所述存储器单元中的阻变器件产生的对应于所述阻变器件的阻值的读取电流。

- 还没有人留言评论。精彩留言会获得点赞!