存储系统以及控制存储系统的方法与流程

本发明的实施方式涉及存储系统以及控制存储系统的方法。

背景技术:

1、以往,已知具备非易失性存储器的存储系统。非易失性存储器在一例中是nand型的闪速存储器(flash memory)。

技术实现思路

1、一个实施方式的目的在于,提供一种读性能高的存储系统以及对能够提高读性能的存储系统进行控制的方法。

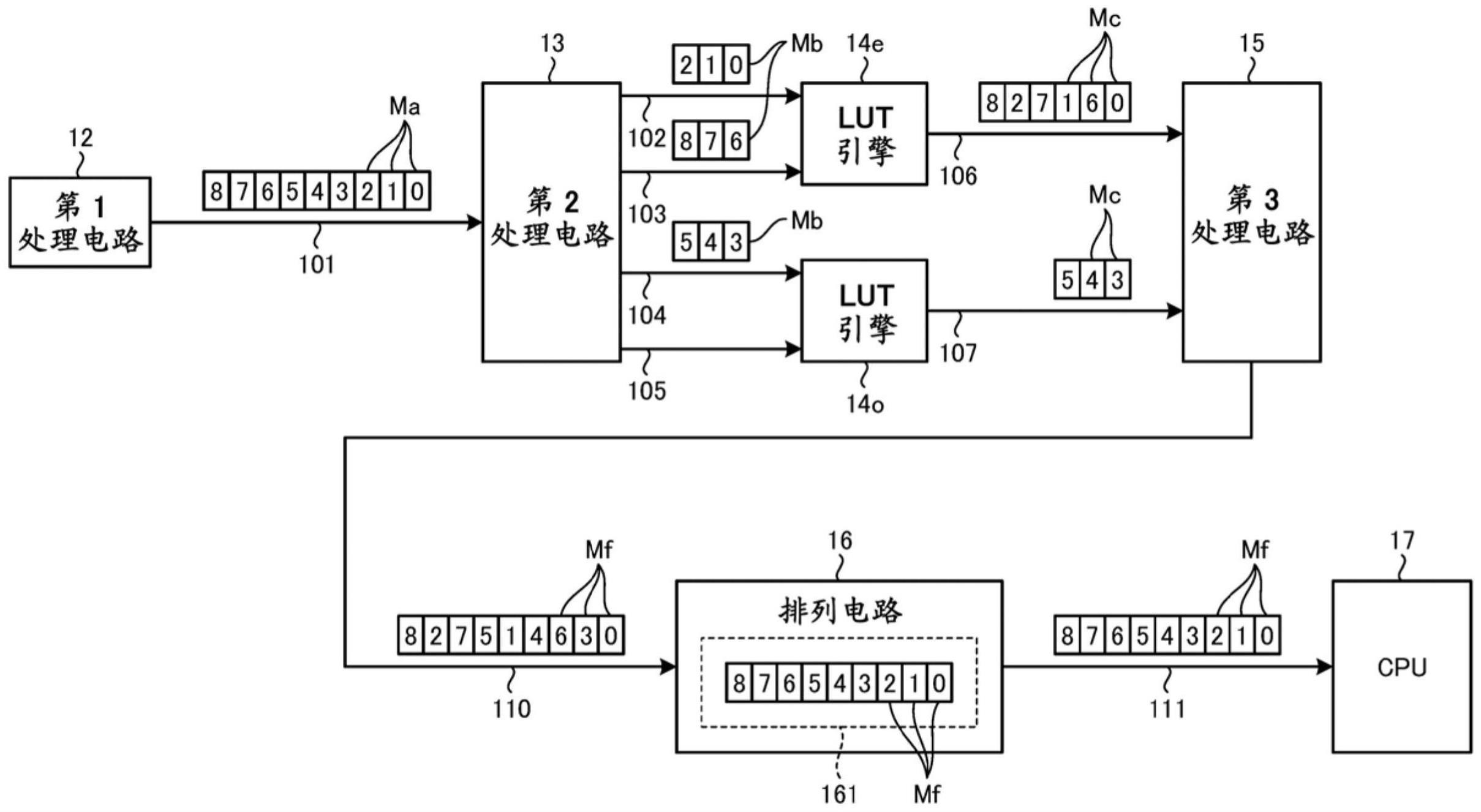

2、一个实施方式的存储系统能够与主机连接。存储系统具备:第1存储器、第2存储器、以及存储控制器。所述第1存储器是构成为保存从所述主机接收到的数据的非易失性存储器。所述第2存储器,构成为保存将所述主机使用的逻辑地址与所述数据在所述第1存储器内被保存的位置按每个第1数据单位进行关联的管理信息。所述存储控制器具备:第1电路、第2电路、多个第3电路、第4电路、第5电路、以及第6电路。所述存储控制器从所述主机接收指定了多个所述第1数据单位的大小的连续的逻辑地址范围的读请求。所述第1电路构成为,响应于所述读请求的接收,按所述逻辑地址的顺序发行请求所述逻辑地址范围所包含的全部第1数据单位的读取的所述多个第1子命令。所述多个第1子命令的每一个分别请求1个第1数据单位的读取。所述第2电路构成为,对所述多个第1子命令的每一个附加与发行顺序对应的第1连续编号,将分别附加了所述第1连续编号的所述多个第1子命令向所述多个第3电路分配。所述多个第3电路的每一个构成为,通过参照所述管理信息来确定所述多个第1子命令中的分配给该第3电路自身的第1子命令相关的第1数据单位的数据的保存位置,将表示所确定出的所述保存位置的位置信息附加给所述第1子命令。所述第4电路构成为,从所述多个第3电路取得分别被附加了所述位置信息的多个所述第1子命令。所述第5电路构成为,使通过所述第4电路取得的所述多个第1子命令按基于所述第1连续编号的顺序进行排列。所述第6电路构成为,基于排列后的所述多个第1子命令执行对所述第1存储器的读动作。

技术特征:

1.一种存储系统,是能够与主机连接的存储系统,具备:

2.根据权利要求1所述的存储系统,

3.根据权利要求1所述的存储系统,

4.根据权利要求3所述的存储系统,

5.根据权利要求3所述的存储系统,

6.根据权利要求1至5中任一项所述的存储系统,

7.一种控制存储系统的方法,

技术总结

提供一种读性能高的存储系统以及对能够提高读性能的存储系统进行控制的方法。第1电路在从主机接收到指定了预定大小以上的逻辑地址范围的读请求的情况下,按逻辑地址的顺序发行各自是每个第1数据单位的子命令的多个第1子命令。第2电路向所述多个第1子命令的每一个附加发行顺序所对应的连续编号。多个第3电路针对所述多个第1子命令的每一个,分担执行基于管理信息确定第1数据单位的位置的处理。第5电路在由所述多个第3电路进行的处理之后,使所述多个第1子命令基于连续编号按逻辑地址顺序排列。第6电路基于按逻辑地址顺序排列后的所述多个第1子命令执行对第1存储器的读动作。

技术研发人员:本谷彻,田所三德,横山知典,市场冬树,港健亮,冈公久

受保护的技术使用者:铠侠股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!