半导体集成电路的制作方法

本发明的实施方式涉及一种半导体集成电路。

背景技术:

1、在半导体集成电路中,配置于衬底上的电路块相互之间通过信号线连接。在传输输入到电路块的数据及从电路块输出的数据的信号线(以下,也称为“传送线路”)中,数据在高电平与低电平之间重复转换。因此,在传送线路中因电荷充放电引起的消耗电流较大。

技术实现思路

1、本发明的实施方式想要解决的问题在于提供一种减少传送线路的消耗电流的半导体集成电路。

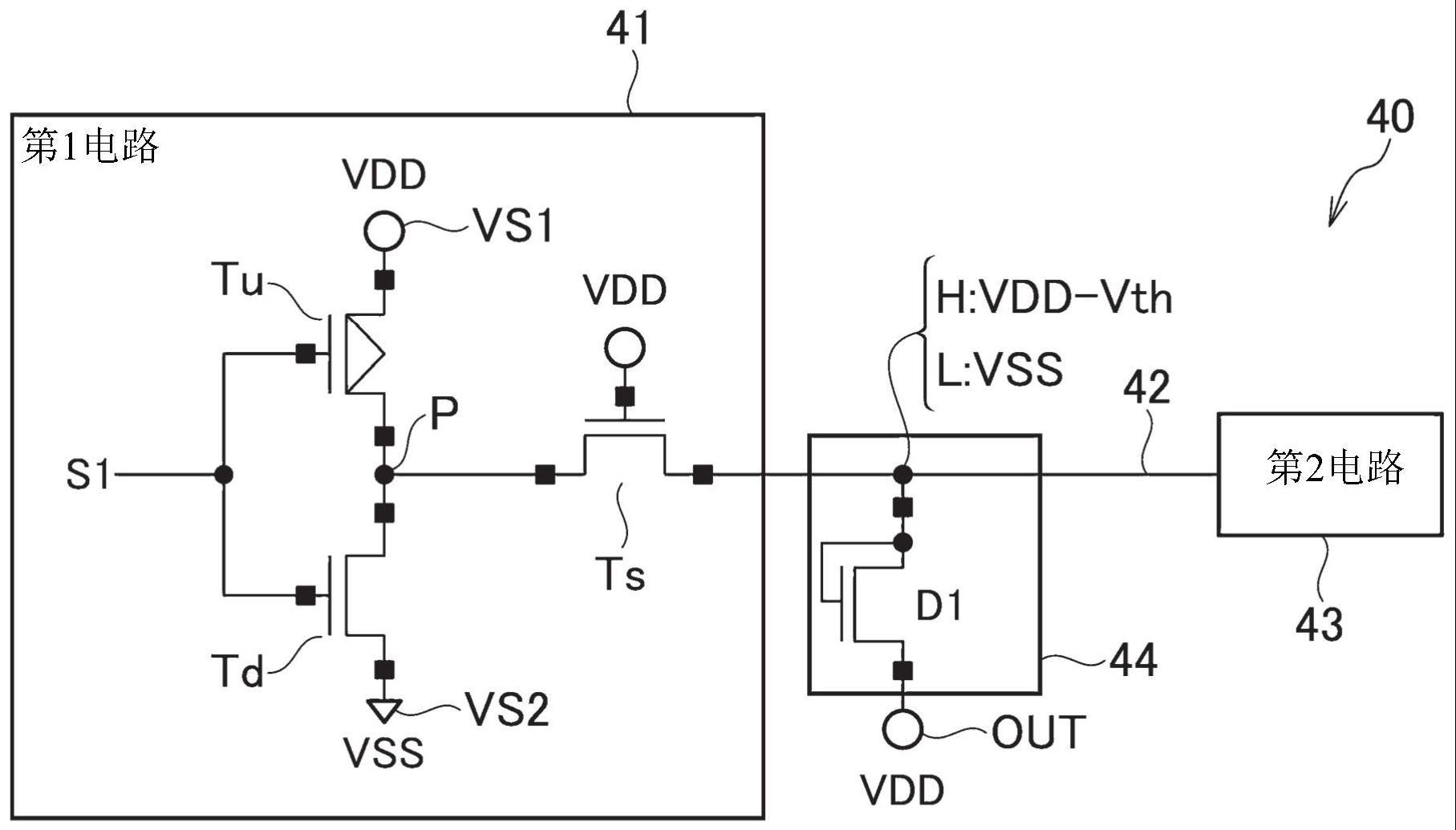

2、实施方式的半导体集成电路具备:第1电路,具有电平移位晶体管;传送线路,传输从第1电路输出的信号;第2电路,输入在传送线路传输的信号;及保护电路,连接于传送线路。第1电路连接于被供给第1电压的电源线,将具有比第1电压降低相当于电平移位晶体管的阈值电压的电压的振幅的信号输出到传送线路。保护电路在传送线路的电压上升到特定的设定电压的情况下,使电流从传送线路流出。

技术特征:

1.一种半导体集成电路,具备:

2.根据权利要求1所述的半导体集成电路,其中所述第1电路具有连接于所述电源线的cmos驱动器,

3.根据权利要求2所述的半导体集成电路,其中所述保护电路连接于所述传送线路与输出端子之间,

4.根据权利要求3所述的半导体集成电路,其中所述保护电路具有二极管,所述二极管的阳极连接于所述传送线路,所述二极管的阴极连接于所述输出端子。

5.根据权利要求3所述的半导体集成电路,其中所述保护电路具有n沟道型mos晶体管,所述n沟道型mos晶体管一个端子与栅极连接于所述传送线路,所述n沟道型mos晶体管的另一个端子连接于所述输出端子。

6.根据权利要求3所述的半导体集成电路,其中所述保护电路具有第1主电极连接于所述传送线路,第2主电极设定为低于所述设定电压的电压的晶体管,

7.根据权利要求3所述的半导体集成电路,其中所述保护电路具有将p沟道型mos晶体管与n沟道型mos晶体管级联连接的构成,

8.根据权利要求1到7中任一权利要求所述的半导体集成电路,其中所述传送线路是双向传输所述信号的信号线。

技术总结

本发明提供一种减少传送线路的消耗电流的半导体集成电路。本发明的半导体集成电路具备:第1电路,具有电平移位晶体管;传送线路,传输从第1电路输出的信号;第2电路,被输入在传送线路传输的信号;及保护电路,连接于传送线路。第1电路连接于被供给第1电压的电源线,将具有比第1电压降低相当于电平移位晶体管的阈值电压的电压的振幅的信号输出到传送线路。保护电路在传送线路的电压上升到特定的设定电压的情况下,使电流从传送线路流出。

技术研发人员:杉本贵宏

受保护的技术使用者:铠侠股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!