包括时钟路径的半导体装置及半导体系统的制作方法

包括时钟路径的半导体装置及半导体系统

1.相关申请的交叉引用

2.本技术要求于2021年9月15日在韩国知识产权局提交的申请号为10-2021-0123073的韩国申请的优先权,该申请通过引用被整体合并于此。

技术领域

3.各个实施例总体上涉及集成电路技术,并且更具体地涉及包括时钟路径的半导体装置。

背景技术:

4.电子设备包括许多电子元件,并且作为电子设备的计算机系统包括各自被配置为包括半导体的许多半导体装置。配置计算机系统的半导体装置可以包括发送电路和接收电路以与彼此进行通信。半导体装置可以通过对系统时钟信号进行缓冲或分频来生成具有各种相位的内部时钟信号。因为半导体装置通过各种内部电路来生成内部时钟信号,所以可能出现异步延迟。因此,可能出现内部时钟信号和系统时钟信号之间的相位差。通常,半导体装置可以设有延迟锁定环电路以通过补偿异步延迟来生成具有与系统时钟信号同步的相位的延迟时钟信号。通过对从延迟锁定环电路生成的时钟信号进行分频,半导体装置可以生成具有不同相位的多个内部时钟信号。而且,半导体装置可以同步于系统时钟信号、基于多个内部时钟信号来生成数据时钟信号。

技术实现要素:

5.在实施例中,半导体装置可以包括内部时钟生成电路、停止控制电路以及数据时钟生成电路。内部时钟生成电路可以被配置为基于参考时钟信号来生成具有不同相位的多个内部时钟信号。停止控制电路可以被配置为基于多个内部时钟信号来生成停止信号,以及被配置为基于参考时钟信号和停止信号来生成时钟电平信号。数据时钟生成电路可以被配置为基于多个内部时钟信号、停止信号和时钟电平信号来生成数据时钟信号和互补数据时钟信号。

6.在实施例中,半导体装置可以包括内部时钟生成电路、停止控制电路以及数据时钟生成电路。内部时钟生成电路可以被配置为基于参考时钟信号来生成具有不同相位的多个内部时钟信号。停止控制电路可以被配置为基于多个内部时钟信号来生成停止信号,被配置为基于参考时钟信号和停止信号来生成时钟电平信号,以及被配置为基于多个内部时钟信号、停止信号和时钟电平信号来生成多个输出时钟信号。数据时钟生成电路可以被配置为基于多个输出时钟信号来生成数据时钟信号和互补数据时钟信号。

7.在实施例中,半导体系统可以包括第一半导体装置和第二半导体装置。第一半导体装置可以被配置为提供系统时钟信号,以及被配置为基于数据时钟信号和互补数据时钟信号来生成命令信号。第二半导体装置可以被配置为基于系统时钟信号来生成多个内部时钟信号。第二半导体装置可以被配置为基于多个内部时钟信号来生成数据时钟信号和互补

数据时钟信号。第二半导体装置可以被配置为当系统时钟信号停止时将数据时钟信号和互补数据时钟信号固定为不同的逻辑电平,以及被配置为基于命令信号来调整用于驱动数据时钟信号和互补数据时钟信号的驱动力。

附图说明

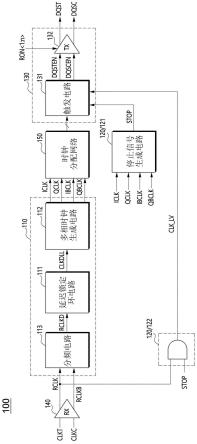

8.图1是示出根据实施例的包括时钟路径的半导体装置的配置的图。

9.图2是示出图1所示的停止信号生成电路的配置的图。

10.图3是示出图1所示的触发电路的配置的框图。

11.图4是示出图3所示的第一触发电路的配置的图。

12.图5是示出图3所示的第二触发电路的配置的图。

13.图6和图7是示出根据实施例的半导体装置的操作的图。

14.图8是示出根据实施例的半导体装置的配置的图。

15.图9是示出图8所示的输出时钟生成电路的配置的图。

16.图10是示出图8所示的触发电路的配置的图。

17.图11是示出根据实施例的半导体装置的配置的图。

18.图12是示出根据实施例的半导体装置的配置的图。

19.图13是示出根据实施例的半导体系统的配置的图。

具体实施方式

20.图1是示出根据实施例的包括时钟路径的半导体装置100的配置的图。参考图1,半导体装置100可以接收成对的系统时钟信号clkt和clkc并且可以输出成对的数据时钟信号dqst和dqsc。成对的系统时钟信号clkt和clkc可以是从外部装置(未图示)向半导体装置100提供的外部信号。成对的系统时钟信号clkt和clkc可以包括系统时钟信号clkt和互补系统时钟信号clkc。互补系统时钟信号clkc可以相对于系统时钟信号clkt具有180

°

的相位差。半导体装置100可以包括时钟路径。通过时钟路径,半导体装置100可以从成对的系统时钟信号clkt和clkc生成成对的数据时钟信号dqst和dqsc。成对的数据时钟信号dqst和dqsc可以包括数据时钟信号dqst和互补数据时钟信号dqsc。互补数据时钟信号dqsc可以相对于数据时钟信号dqst具有180

°

的相位差。时钟路径可以包括所有内部电路,成对的系统时钟信号clkt和clkc通过上述内部电路被传播,直到成对的数据时钟信号dqst和dqsc被生成为止。

21.半导体装置100可以包括内部时钟生成电路110、停止控制电路120以及数据时钟生成电路130。内部时钟生成电路110可以接收参考时钟信号rclk,并且可以基于参考时钟信号rclk来生成多个内部时钟信号iclk、qclk、ibclk和qbclk。在实施例中,内部时钟生成电路110还可以接收互补参考时钟信号rclkb,并且可以基于参考时钟信号rclk和互补参考时钟信号rclkb来生成多个内部时钟信号iclk、qclk、ibclk和qbclk。参考时钟信号rclk可以是通过缓冲成对的系统时钟信号clkt和clkc所生成的时钟信号。半导体装置100还可以包括时钟接收器(rx)140。时钟接收器140可以从外部装置接收成对的系统时钟信号clkt和clkc,并且可以通过有区别地放大成对的系统时钟信号clkt和clkc来生成参考时钟信号rclk。参考时钟信号rclk可以具有对应于系统时钟信号clkt的相位。实际上,由于出现在时

钟接收器140中的延迟,参考时钟信号rclk可以具有略微地滞后于系统时钟信号clkt的相位。内部时钟生成电路110可以对参考时钟信号rclk执行延迟锁定操作,以生成具有不同相位的多个内部时钟信号iclk、qclk、ibclk和qbclk。例如,多个内部时钟信号iclk、qclk、ibclk和qbclk可以包括第一内部时钟信号iclk、第二内部时钟信号qclk、第三内部时钟信号ibclk和第四内部时钟信号qbclk。第一至第四内部时钟信号iclk、qclk、ibclk和qbclk可以相对彼此依次具有90

°

的相位差。第一内部时钟信号iclk可以具有相比第二内部时钟信号qclk超前90

°

的相位。第二内部时钟信号qclk可以具有相比第三内部时钟信号ibclk超前90

°

的相位。第三内部时钟信号ibclk可以具有相比第四内部时钟信号qbclk超前90

°

的相位。第四内部时钟信号qbclk可以具有相比第一内部时钟信号iclk超前90

°

的相位。

22.内部时钟生成电路110可以包括延迟锁定环电路111和多相时钟生成电路112。延迟锁定环电路111可以通过接收参考时钟信号rclk以及对参考时钟信号rclk执行延迟锁定操作来生成延迟锁定时钟信号clkdll。在半导体装置100的时钟路径中,由于时钟接收器140和稍后描述的内部电路,可能出现延迟。因此,可能存在如下情况,即,通过时钟路径传播的时钟信号最终相对于系统时钟信号clkt具有相位差。延迟锁定环电路111可以将参考时钟信号rclk延迟以补偿时钟路径的传播延迟,由此使成对的数据时钟信号dqst和dqsc与成对的系统时钟信号clkt和clkc同步。例如,延迟锁定环电路111延迟参考时钟信号rclk的延迟时间量与传播延迟的时间量的总和可以对应于成对的系统时钟信号clkt和clkc的周期的倍数。延迟锁定环电路111可以包括被配置为执行延迟锁定操作的任何类型的延迟锁定环。例如,延迟锁定环电路111可以包括数字延迟锁定环。

23.多相时钟生成电路112可以耦接到延迟锁定环电路111,并且可以从延迟锁定环电路111接收延迟锁定时钟信号clkdll。多相时钟生成电路112可以基于延迟锁定时钟信号clkdll来生成多个内部时钟信号iclk、qclk、ibclk和qbclk。多相时钟生成电路112可以通过对延迟锁定时钟信号clkdll另外执行延迟锁定操作来生成第一至第四内部时钟信号iclk、qclk、ibclk和qbclk。多相时钟生成电路112可以对延迟锁定时钟信号clkdll进行分频,并且可以对经分频的时钟信号的相位进行插值以生成第一至第四内部时钟信号iclk、qclk、ibclk和qbclk。多相时钟生成电路112可以包括被配置为生成具有不同相位的多个时钟信号的任何类型的时钟生成器。例如,多相时钟生成电路112可以包括另一数字延迟锁定环、模拟延迟锁定环和相位插值器中的至少一个。

24.内部时钟生成电路110还可以包括分频电路113。分频电路113可以对参考时钟信号rclk进行分频以生成经分频参考时钟信号rclkd。分频电路113可以对参考时钟信号rclk的频率进行分频以生成经分频参考时钟信号rclkd。经分频参考时钟信号rclkd可以具有比参考时钟信号rclk低的频率。例如,经分频参考时钟信号rclkd的频率可以是参考时钟信号rclk的频率的一半(1/2)。当设有分频电路113时,延迟锁定环电路111可以接收经分频参考时钟信号rclkd并且可以对经分频参考时钟信号rclkd执行延迟锁定操作。在实施例中,当延迟锁定环电路111接收经分频参考时钟信号rclkd并且对经分频参考时钟信号rclkd执行延迟锁定操作时,可以调整更新延迟锁定环电路111的延迟时间量的周期,并且因此可以减少用于延迟锁定操作的功率消耗。此外,在一些实施例中,因为延迟锁定环电路111对具有较低频率的时钟信号执行延迟锁定操作,所以可以提高延迟锁定操作的可靠性。

25.可以提供停止控制电路120以便监测半导体装置100的参数。半导体装置100的参

数可以是包括半导体装置100的任何类型的操作状态或规格的值或信息。例如,半导体装置100的参数可以是被配置为生成成对的数据时钟信号dqst和dqsc的数据时钟生成电路130的操作电阻值。操作电阻值可以与驱动成对的数据时钟信号dqst和dqsc的驱动力和/或强度有关。通过将成对的数据时钟信号dqst和dqsc固定为不同的逻辑电平,停止控制电路120可以允许接收成对的数据时钟信号dqst和dqsc的外部装置监测和/或测量半导体装置100的操作电阻值。外部装置可以将成对的系统时钟信号clkt和clkc固定为特定逻辑电平,以测量半导体装置100的操作电阻值。例如,半导体装置100可以从外部装置接收被固定为低逻辑电平的系统时钟信号clkt以及被固定为高逻辑电平的互补系统时钟信号clkc。例如,半导体装置100可以从外部装置接收被固定为高逻辑电平的系统时钟信号clkt以及被固定为低逻辑电平的互补系统时钟信号clkc。

26.停止控制电路120可以接收参考时钟信号rclk以及多个内部时钟信号iclk、qclk、ibclk和qbclk,并且可以生成停止信号stop和时钟电平信号clk_lv。基于多个内部时钟信号iclk、qclk、ibclk和qbclk,停止控制电路120可以生成停止信号stop。停止控制电路120可以检测多个内部时钟信号iclk、qclk、ibclk和qbclk的逻辑电平以生成停止信号stop。基于参考时钟信号rclk和停止信号stop,停止控制电路120可以生成时钟电平信号clk_lv。当停止信号stop变为使能时,停止控制电路120可以提供参考时钟信号rclk作为时钟电平信号clk_lv。

27.停止控制电路120可以包括停止信号生成电路121和选通电路122。停止信号生成电路121可以接收多个内部时钟信号iclk、qclk、ibclk和qbclk。停止信号生成电路121可以检测多个内部时钟信号iclk、qclk、ibclk和qbclk的逻辑电平以生成停止信号stop。当多个内部时钟信号iclk、qclk、ibclk和qbclk全部具有相同的逻辑电平时,停止信号生成电路121可以使能停止信号stop。例如,当多个内部时钟信号iclk、qclk、ibclk和qbclk全部具有高逻辑电平时,停止信号生成电路121可以使能停止信号stop。当成对的系统时钟信号clkt和clkc的逻辑电平被固定时,从内部时钟生成电路110输出的第一至第四内部时钟信号iclk、qclk、ibclk和qbclk全部可以被固定为高逻辑电平。当第一至第四内部时钟信号iclk、qclk、ibclk和qbclk全部具有高逻辑电平时,停止控制电路120可以检测出成对的系统时钟信号clkt和clkc被停止,并且可以使能停止信号stop。

28.选通电路122可以接收参考时钟信号rclk和停止信号stop。选通电路122可以基于参考时钟信号rclk和停止信号stop来生成时钟电平信号clk_lv。选通电路122可以基于停止信号stop来对参考时钟信号rclk进行选通。当停止信号stop处于禁止状态中时,选通电路122可以阻止参考时钟信号rclk而不将参考时钟信号rclk提供为时钟电平信号clk_lv。当停止信号stop变为使能时,选通电路122可以提供参考时钟信号rclk作为时钟电平信号clk_lv。选通电路122可以包括与门。该与门可以接收参考时钟信号rclk和停止信号stop,并且可以对参考时钟信号rclk和停止信号stop执行与运算以输出时钟电平信号clk_lv。

29.数据时钟生成电路130可以基于多个内部时钟信号iclk、qclk、ibclk和qbclk、停止信号stop以及时钟电平信号clk_lv来生成数据时钟信号dqst和互补数据时钟信号dqsc。当停止信号stop处于禁止状态中时,数据时钟生成电路130可以基于多个内部时钟信号iclk、qclk、ibclk和qbclk来生成数据时钟信号dqst和互补数据时钟信号dqsc。数据时钟信号dqst和互补数据时钟信号dqsc可以根据多个内部时钟信号iclk、qclk、ibclk和qbclk的

逻辑电平的周期性改变而切变。当停止信号stop变为使能时,数据时钟生成电路130可以基于时钟电平信号clk_lv来生成数据时钟信号dqst和互补数据时钟信号dqsc。根据时钟电平信号clk_lv,数据时钟生成电路130可以将数据时钟信号dqst和互补数据时钟信号dqsc固定为不同的逻辑电平。例如,数据时钟生成电路130可以将数据时钟信号dqst固定为对应于时钟电平信号clk_lv的逻辑电平,并且可以将互补数据时钟信号dqsc固定为与时钟电平信号clk_lv相反的逻辑电平。

30.数据时钟生成电路130可以包括触发电路131和数据时钟发送器(tx)132。触发电路131可以接收多个内部时钟信号iclk、qclk、ibclk和qbclk、停止信号stop以及时钟电平信号clk_lv,并且可以生成数据时钟驱动信号dqsten和互补数据时钟驱动信号dqscen。当停止信号stop变为禁止时,触发电路131可以基于多个内部时钟信号iclk、qclk、ibclk和qbclk来生成数据时钟驱动信号dqsten和互补数据时钟驱动信号dqscen。当停止信号stop变为使能时,触发电路131可以基于时钟电平信号clk_lv将数据时钟驱动信号dqsten和互补数据时钟驱动信号dqscen固定为特定逻辑电平。触发电路131可以将数据时钟驱动信号dqsten固定为对应于时钟电平信号clk_lv的逻辑电平,并且可以将互补数据时钟驱动信号dqscen固定为与时钟电平信号clk_lv相反的逻辑电平。

31.数据时钟发送器132可以接收数据时钟驱动信号dqsten和互补数据时钟驱动信号dqscen,并且可以生成数据时钟信号dqst和互补数据时钟信号dqsc。数据时钟发送器132可以向外部装置输出数据时钟信号dqst和互补数据时钟信号dqsc。数据时钟发送器132可以接收电阻设置信号ron《1:n》(

‘

n’是等于或大于2的整数)。可以根据电阻设置信号ron《1:n》来确定数据时钟发送器132的操作电阻值。基于电阻设置信号ron《1:n》,可以确定数据时钟发送器132用来基于数据时钟驱动信号dqsten和互补数据时钟驱动信号dqscen驱动数据时钟信号dqst和互补数据时钟信号dqsc的驱动力和/或强度。电阻设置信号ron《1:n》可以确定数据时钟发送器132用来将数据时钟信号dqst和互补数据时钟信号dqsc上拉驱动为高逻辑电平的驱动力和/或强度,并且可以确定数据时钟发送器132用来将数据时钟信号dqst和互补数据时钟信号dqsc下拉驱动为低逻辑电平的驱动力和/或强度。

32.半导体装置100还可以包括时钟分配网络150。时钟分配网络150可以耦接在内部时钟生成电路110和数据时钟生成电路130之间。时钟分配网络150可以是时钟树。时钟分配网络150可以从多相时钟生成电路112接收多个内部时钟信号iclk、qclk、ibclk和qbclk,并且可以驱动多个内部时钟信号iclk、qclk、ibclk和qbclk。时钟分配网络150可以向数据时钟生成电路130提供被驱动的多个内部时钟信号iclk、qclk、ibclk和qbclk。时钟分配网络150可以驱动第一至第四内部时钟信号iclk、qclk、ibclk和qbclk,并且可以向数据时钟生成电路130提供第一至第四内部时钟信号iclk、qclk、ibclk和qbclk。在实施例中,时钟分配网络150可以被提供在延迟锁定环电路111和多相时钟生成电路112之间。在实施例中,当时钟分配网络150设置在延迟锁定环电路111和多相时钟生成电路112之间时,时钟分配网络150可以被配置为驱动延迟锁定时钟信号clkdll以向多相时钟生成电路112提供延迟锁定时钟信号clkdll。

33.图2是示出图1所示的停止信号生成电路121的配置的图。参考图2,停止信号生成电路121可以包括预备停止信号生成器210和停止信号驱动器220。预备停止信号生成器210可以接收多个内部时钟信号iclk、qclk、ibclk和qbclk,并且可以基于多个内部时钟信号

iclk、qclk、ibclk和qbclk来生成预备停止信号stop_pre。预备停止信号生成器210可以检测多个内部时钟信号iclk、qclk、ibclk和qbclk的逻辑电平以生成预备停止信号stop_pre。当多个内部时钟信号iclk、qclk、ibclk和qbclk的逻辑电平周期性地改变时,预备停止信号生成器210可以周期性地使能和禁止预备停止信号stop_pre。当多个内部时钟信号iclk、qclk、ibclk和qbclk被固定为特定逻辑电平时,预备停止信号生成器210可以使能预备停止信号stop_pre并且可以保持预备停止信号stop_pre被使能。停止信号驱动器220可以接收预备停止信号stop_pre,并且可以基于预备停止信号stop_pre生成停止信号stop。当预备停止信号stop_pre保持使能达预定时间量时,停止信号驱动器220可以使能停止信号stop。当预备停止信号stop_pre被周期性地使能和禁止时,停止信号驱动器220可以不使能停止信号stop。当多个内部时钟信号iclk、qclk、ibclk和qbclk被固定为特定逻辑电平并且预备停止信号stop_pre保持使能时,停止信号驱动器220可以使能停止信号stop。这里所使用的关于参数的词语“预定”(诸如预定时间)意味着在处理或算法中使用参数之前确定了该参数的值。对于某些实施例,在处理或算法开始之前确定参数的值。在其他实施例中,在处理或算法期间、但是在处理或算法中使用参数之前,确定该参数的值。

34.预备停止信号生成器210可以包括第一触发器211、第二触发器212、第三触发器213、第四触发器214、第一反相器215、第二反相器216和与门217。第一至第四触发器211、212、213和214中的每一个可以是sr触发器。第一触发器211可以在置位节点s接收第一内部时钟信号iclk,可以在复位节点r接收第三内部时钟信号ibclk,并且可以在输出节点q输出第一边沿信号iedge。当第一内部时钟信号iclk从低逻辑电平转换为高逻辑电平时,第一触发器211可以将第一边沿信号iedge使能为高逻辑电平。当第三内部时钟信号ibclk从低逻辑电平转换为高逻辑电平时,第一触发器211可以将第一边沿信号iedge禁止为低逻辑电平。第二触发器212可以在置位节点s接收第二内部时钟信号qclk,可以在复位节点r接收第四内部时钟信号qbclk,并且可以在输出节点q输出第二边沿信号qedge。当第二内部时钟信号qclk从低逻辑电平转换为高逻辑电平时,第二触发器212可以将第二边沿信号qedge使能为高逻辑电平。当第四内部时钟信号qbclk从低逻辑电平转换为高逻辑电平时,第二触发器212可以将第二边沿信号qedge禁止为低逻辑电平。第三触发器213可以在置位节点s接收第三内部时钟信号ibclk,可以在复位节点r接收第一内部时钟信号iclk,并且可以在输出节点q输出第三边沿信号ibedge。当第三内部时钟信号ibclk从低逻辑电平转换为高逻辑电平时,第三触发器213可以将第三边沿信号ibedge使能为高逻辑电平。当第一内部时钟信号iclk从低逻辑电平转换为高逻辑电平时,第三触发器213可以将第三边沿信号ibedge禁止为低逻辑电平。第四触发器214可以在置位节点s接收第四内部时钟信号qbclk,可以在复位节点r接收第二内部时钟信号qclk,并且可以在输出节点q输出第四边沿信号qbedge。当第四内部时钟信号qbclk从低逻辑电平转换为高逻辑电平时,第四触发器214可以将第四边沿信号qbedge使能为高逻辑电平。当第二内部时钟信号qclk从低逻辑电平转换为高逻辑电平时,第四触发器214可以将第四边沿信号qbedge禁止为低逻辑电平。第一反相器215可以接收第一边沿信号iedge,并且可以使第一边沿信号iedge反相以输出经反相第一边沿信号iedgeb。第二反相器216可以接收第二边沿信号qedge,并且可以使第二边沿信号qedge反相以输出经反相第二边沿信号qedgeb。与门217可以接收第一反相器215的输出、第二反相器216的输出、第三边沿信号ibedge和第四边沿信号qbedge。与门217可以对经反相第一边沿

信号iedgeb、经反相第二边沿信号qedgeb、第三边沿信号ibedge和第四边沿信号qbedge执行与运算以输出预备停止信号stop_pre。例如,当系统时钟信号clkt被固定为特定逻辑电平并且参考时钟信号rclk被固定为低逻辑电平或高逻辑电平时,第一至第四内部时钟信号iclk、qclk、ibclk和qbclk可以依次转换为高逻辑电平。因此,第一触发器211和第二触发器212可以分别生成具有低逻辑电平的第一边沿信号iedge和第二边沿信号qedge,并且第三触发器213和第四触发器214可以分别生成具有高逻辑电平的第三边沿信号ibedge和第四边沿信号qbedge。与门217可以接收具有高逻辑电平的经反相第一边沿信号iedgeb、经反相第二边沿信号qedgeb、第三边沿信号ibedge和第四边沿信号qbedge,并且因此与门217可以使能预备停止信号stop_pre并且可以保持预备停止信号stop_pre被使能。

35.停止信号驱动器220可以包括第一晶体管221、第二晶体管222、电容器223和反相器224。第一晶体管221和第二晶体管222中的每一个可以是p沟道mos晶体管。第一晶体管221可以在其栅极接收预备停止信号stop_pre,并且可以在其源极耦接到供应第一电源电压vdd的节点,并且可以在其漏极耦接到检测节点sn。第二晶体管222可以在其栅极和漏极耦接到供应第二电源电压vss的节点,并且可以在其源极耦接到检测节点sn。第二电源电压vss可以具有比第一电源电压vdd低的电压电平。例如,第一电源电压vdd可以是半导体装置100的供给电压,并且第二电源电压vss可以是接地电压。电容器223可以在其一端耦接到检测节点sn,并且可以在其另一端耦接到供应第二电源电压vss的节点。反相器224可以在其输入节点耦接到检测节点sn,并且可以在其输出节点输出停止信号stop。停止信号驱动器220还可以包括第三晶体管225。第三晶体管225可以是p沟道mos晶体管。第三晶体管225可以耦接在第一晶体管221和供应第一电源电压vdd的节点之间,并且可以接收复位信号rst。当复位信号rst被使能时,第三晶体管225可以阻止第一电源电压vdd而不将第一电源电压vdd提供到第一晶体管221。当复位信号rst被禁止时,第三晶体管225可以向第一晶体管221提供第一电源电压vdd。当预备停止信号stop_pre被周期性地使能时,停止信号驱动器220可以周期性地向检测节点sn提供第一电源电压vdd,并且因此电容器223中的电荷量可以被保持并且检测节点sn可以保持为高逻辑电平。当预备停止信号stop_pre保持使能达预定时间量或更多时间量时,在上述预定时间量内,可以不将第一电源电压vdd提供到检测节点sn,并且可以使电容器223放电,并且因此检测节点sn的逻辑电平可以改变为低逻辑电平。当检测节点sn变为具有低逻辑电平时,停止信号stop可以被使能。预定时间量可以取决于电容器223的电容。

36.图3是示出图1所示的触发电路131的配置的框图。参考图3,触发电路131可以包括第一触发电路310和第二触发电路320。第一触发电路310可以接收多个内部时钟信号iclk、qclk、ibclk和qbclk、停止信号stop以及时钟电平信号clk_lv,并且可以生成数据时钟驱动信号dqsten。当停止信号stop处于禁止状态中时,第一触发电路310可以根据多个内部时钟信号iclk、qclk、ibclk和qbclk的逻辑电平来使能和禁止数据时钟驱动信号dqsten。当停止信号stop变为使能时,第一触发电路310可以根据时钟电平信号clk_lv将数据时钟驱动信号dqsten固定为特定逻辑电平。第二触发电路320可以接收多个内部时钟信号iclk、qclk、ibclk和qbclk、停止信号stop以及时钟电平信号clk_lv,并且可以生成互补数据时钟驱动信号dqscen。当停止信号stop处于禁止状态中时,第二触发电路320可以根据多个内部时钟信号iclk、qclk、ibclk和qbclk的逻辑电平来使能和禁止互补数据时钟驱动信号dqscen。当

停止信号stop变为使能时,第二触发电路320可以根据时钟电平信号clk_lv将互补数据时钟驱动信号dqscen固定为特定逻辑电平。

37.图4是示出图3所示的第一触发电路310的配置的图。参考图4,第一触发电路310可以包括第一与非门411、第二与非门412、第三与非门413、第四与非门414、第一反相器421、第二反相器422、第三反相器423、第四反相器424、第五反相器425、第六反相器426、第七反相器427、第八反相器428、第五与非门431、第六与非门432、第七与非门433、第八与非门434、第九与非门441、第十与非门442、第九反相器451、第十一与非门452、第十二与非门453、第十三与非门454以及与门461。第一与非门411可以接收第二电源电压vss和第一内部时钟信号iclk。第二与非门412可以接收第二电源电压vss和第三内部时钟信号ibclk。第三与非门413可以接收第一电源电压vdd和第二内部时钟信号qclk。第四与非门414可以接收第一电源电压vdd和第四内部时钟信号qbclk。第一反相器421可以接收第一与非门411的输出并且可以使第一与非门411的输出反相。第二反相器422可以接收第二内部时钟信号qclk并且可以使第二内部时钟信号qclk反相。第三反相器423可以接收第二与非门412的输出并且可以使第二与非门412的输出反相。第四反相器424可以接收第四内部时钟信号qbclk并且可以使第四内部时钟信号qbclk反相。第五反相器425可以接收第三与非门413的输出并且可以使第三与非门413的输出反相。第六反相器426可以接收第三内部时钟信号ibclk并且可以使第三内部时钟信号ibclk反相。第七反相器427可以接收第四与非门414的输出并且可以使第四与非门414的输出反相。第八反相器428可以接收第一内部时钟信号iclk并且可以使第一内部时钟信号iclk反相。

38.第五与非门431可以接收第一反相器421的输出和第二反相器422的输出。第六与非门432可以接收第三反相器423的输出和第四反相器424的输出。第七与非门433可以接收第五反相器425的输出和第六反相器426的输出。第八与非门434可以接收第七反相器427的输出和第八反相器428的输出。第九与非门441可以接收第五与非门431的输出和第六与非门432的输出。第十与非门442可以接收第七与非门433的输出和第八与非门434的输出。第九反相器451可以接收停止信号stop并且可以使停止信号stop反相。第十一与非门452可以接收第九与非门441的输出和第九反相器451的输出。第十二与非门453可以接收第十与非门442的输出和第九反相器451的输出。第十三与非门454可以接收停止信号stop和时钟电平信号clk_lv的互补信号,即互补时钟电平信号clk_lvb。与门461可以接收第十一与非门452的输出、第十二与非门453的输出和第十三与非门454的输出,并且可以生成数据时钟驱动信号dqsten。

39.图5是示出图3所示的第二触发电路320的配置的图。参考图5,第二触发电路320可以包括第一与非门511、第二与非门512、第三与非门513、第四与非门514、第一反相器521、第二反相器522、第三反相器523、第四反相器524、第五反相器525、第六反相器526、第七反相器527、第八反相器528、第五与非门531、第六与非门532、第七与非门533、第八与非门534、第九与非门541、第十与非门542、第九反相器551、第十一与非门552、第十二与非门553、第十三与非门554以及与门561。第一与非门511可以接收第一电源电压vdd和第一内部时钟信号iclk。第二与非门512可以接收第一电源电压vdd和第三内部时钟信号ibclk。第三与非门513可以接收第二电源电压vss和第二内部时钟信号qclk。第四与非门514可以接收第二电源电压vss和第四内部时钟信号qbclk。第一反相器521可以接收第一与非门511的输

出并且可以使第一与非门511的输出反相。第二反相器522可以接收第二内部时钟信号qclk并且可以使第二内部时钟信号qclk反相。第三反相器523可以接收第二与非门512的输出并且可以使第二与非门512的输出反相。第四反相器524可以接收第四内部时钟信号qbclk并且可以使第四内部时钟信号qbclk反相。第五反相器525可以接收第三与非门513的输出并且可以使第三与非门513的输出反相。第六反相器526可以接收第三内部时钟信号ibclk并且可以使第三内部时钟信号ibclk反相。第七反相器527可以接收第四与非门514的输出并且可以使第四与非门514的输出反相。第八反相器528可以接收第一内部时钟信号iclk并且可以使第一内部时钟信号iclk反相。

40.第五与非门531可以接收第一反相器521的输出和第二反相器522的输出。第六与非门532可以接收第三反相器523的输出和第四反相器524的输出。第七与非门533可以接收第五反相器525的输出和第六反相器526的输出。第八与非门534可以接收第七反相器527的输出和第八反相器528的输出。第九与非门541可以接收第五与非门531的输出和第六与非门532的输出。第十与非门542可以接收第七与非门533的输出和第八与非门534的输出。第九反相器551可以接收停止信号stop并且可以使停止信号stop反相。第十一与非门552可以接收第九与非门541的输出和第九反相器551的输出。第十二与非门553可以接收第十与非门542的输出和第九反相器551的输出。第十三与非门554可以接收停止信号stop和时钟电平信号clk_lv。与门561可以接收第十一与非门552的输出、第十二与非门553的输出和第十三与非门554的输出,并且可以生成互补数据时钟驱动信号dqscen。

41.[表1]

[0042]

iclkqclkibclkqbclkdqstendqscenllhhlhhllhhlhhlllhlhhlhl

[0043]

(“l”表示低逻辑电平,并且“h”表示高逻辑电平。)

[0044]

表1示出当停止信号stop被禁止时的第一触发电路310的操作和第二触发电路320的操作。当停止信号stop被禁止时,第一触发电路310和第二触发电路320可以根据第一至第四内部时钟信号iclk、qclk、ibclk和qbclk的逻辑电平来周期性地使能数据时钟驱动信号dqsten和互补数据时钟驱动信号dqscen。当第一内部时钟信号iclk和第二内部时钟信号qclk具有低逻辑电平并且第三内部时钟信号ibclk和第四内部时钟信号qbclk具有高逻辑电平时,第一触发电路310可以将数据时钟驱动信号dqsten禁止为低逻辑电平,并且第二触发电路320可以将互补数据时钟驱动信号dqscen使能为高逻辑电平。当第一内部时钟信号iclk和第四内部时钟信号qbclk具有高逻辑电平并且第二内部时钟信号qclk和第三内部时钟信号ibclk具有低逻辑电平时,第一触发电路310可以将数据时钟驱动信号dqsten使能为高逻辑电平,并且第二触发电路320可以将互补数据时钟驱动信号dqscen禁止为低逻辑电平。当第一内部时钟信号iclk和第二内部时钟信号qclk具有高逻辑电平并且第三内部时钟信号ibclk和第四内部时钟信号qbclk具有低逻辑电平时,第一触发电路310可以将数据时钟驱动信号dqsten禁止为低逻辑电平,并且第二触发电路320可以将互补数据时钟驱动信号dqscen使能为高逻辑电平。当第一内部时钟信号iclk和第四内部时钟信号qbclk具有低

逻辑电平并且第二内部时钟信号qclk和第三内部时钟信号ibclk具有高逻辑电平时,第一触发电路310可以将数据时钟驱动信号dqsten使能为高逻辑电平,并且第二触发电路320可以将互补数据时钟驱动信号dqscen禁止为低逻辑电平。

[0045]

[表2]

[0046]

stopclk_lvdqstendqscenhllhhhhl

[0047]

(“l”表示低逻辑电平,并且“h”表示高逻辑电平。)

[0048]

表2示出当停止信号stop被使能时的第一触发电路310的操作和第二触发电路320的操作。当停止信号stop被使能时,第一触发电路310和第二触发电路320可以根据时钟电平信号clk_lv将数据时钟驱动信号dqsten和互补数据时钟驱动信号dqscen固定为特定逻辑电平。当停止信号stop被使能为高逻辑电平并且时钟电平信号clk_lv具有低逻辑电平时,第一触发电路310可以将数据时钟驱动信号dqsten固定为低逻辑电平,并且第二触发电路320可以将互补数据时钟驱动信号dqscen固定为高逻辑电平。当停止信号stop被使能为高逻辑电平并且时钟电平信号clk_lv具有高逻辑电平时,第一触发电路310可以将数据时钟驱动信号dqsten固定为高逻辑电平,并且第二触发电路320可以将互补数据时钟驱动信号dqscen固定为低逻辑电平。

[0049]

图6和图7是示出根据实施例的半导体装置100的操作的图。在下文中,将参考图1至图7描述根据实施例的半导体装置100的操作。在正常操作期间,半导体装置100可以接收周期性地切变的成对的系统时钟信号clkt和clkc。经分频参考时钟信号rclkd的周期可以比系统时钟信号clkt的周期长。例如,经分频参考时钟信号rclkd的周期可以是系统时钟信号clkt的周期的两倍长。将不示出由于时钟接收器140和分频电路113引起的传播延迟。内部时钟生成电路110可以对经分频参考时钟信号rclkd执行延迟锁定操作,并且可以生成相对于彼此依次具有90

°

的相位差的第一至第四内部时钟信号iclk、qclk、ibclk和qbclk。当成对的系统时钟信号clkt和clkc以及参考时钟信号rclk周期性地切变时,第一至第四内部时钟信号iclk、qclk、ibclk和qbclk也可以连续地切变。尽管停止信号生成电路121可以基于第一至第四内部时钟信号iclk、qclk、ibclk和qbclk而周期性地使能预备停止信号stop_pre,但检测节点sn的电压电平可以不改变为可能低于反相器224的阈值的低逻辑电平,并且停止信号stop可以保持禁止。当停止信号stop处于禁止状态中时,数据时钟生成电路130可以生成根据第一至第四内部时钟信号iclk、qclk、ibclk和qbclk的逻辑电平周期性地切变的成对的数据时钟信号dqst和dqsc。成对的数据时钟信号dqst和dqsc可以具有同步于成对的系统时钟信号clkt和clkc的相位,并且可以具有与成对的系统时钟信号clkt和clkc相同的周期和/或频率。

[0050]

为了测量半导体装置100的操作电阻值,成对的系统时钟信号clkt和clkc可以被固定为特定逻辑电平。如图6中所示,系统时钟信号clkt可以被固定为高逻辑电平,并且互补系统时钟信号clkc可以被固定为低逻辑电平。当系统时钟信号clkt被固定为高逻辑电平时,参考时钟信号rclk可以同步于系统时钟信号clkt的最后上升沿被固定为高逻辑电平,并且第一至第四内部时钟信号iclk、qclk、ibclk和qbclk可以依次改变为高逻辑电平。当第一至第四内部时钟信号iclk、qclk、ibclk和qbclk依次改变为高逻辑电平时,预备停止信号

生成器210可以将第一边沿信号iedge和第二边沿信号qedge固定为低逻辑电平,可以将第三边沿信号ibedge和第四边沿信号qbedge固定为高逻辑电平,并且可以保持预备停止信号stop_pre被使能。当预备停止信号stop_pre保持使能时,检测节点sn的电压电平可以下降到足够低于反相器224的阈值的电平,并且停止信号stop可以变得被使能为高逻辑电平。当停止信号stop被使能为高逻辑电平时,选通电路122可以提供系统时钟信号clkt作为时钟电平信号clk_lv,并且该时钟电平信号clk_lv可以具有高逻辑电平。基于时钟电平信号clk_lv,数据时钟生成电路130可以将数据时钟驱动信号dqsten和数据时钟信号dqst固定为高逻辑电平,并且可以将互补数据时钟驱动信号dqscen和互补数据时钟信号dqsc固定为低逻辑电平。可以基于电阻设置信号ron《1:n》来确定数据时钟发送器132的上拉驱动力和/或强度以及下拉驱动力和/或强度。因此,被固定为高逻辑电平的数据时钟信号dqst可以是能够通过其来测量半导体装置100的上拉电阻值的信号,并且被固定为低逻辑电平的互补数据时钟信号dqsc可以是能够通过其来测量半导体装置100的下拉电阻值的信号。

[0051]

如与图6的图示相反的图7中所示,系统时钟信号clkt可以被固定为低逻辑电平,并且互补系统时钟信号clkc可以被固定为高逻辑电平。当系统时钟信号clkt被固定为低逻辑电平时,参考时钟信号rclk可以同步于系统时钟信号clkt的最后上升沿被固定为高逻辑电平,并且第一至第四内部时钟信号iclk、qclk、ibclk和qbclk可以依次改变为高逻辑电平。当第一至第四内部时钟信号iclk、qclk、ibclk和qbclk依次改变为高逻辑电平时,预备停止信号生成器210可以将第一边沿信号iedge和第二边沿信号qedge固定为低逻辑电平,可以将第三边沿信号ibedge和第四边沿信号qbedge固定为高逻辑电平,并且可以保持预备停止信号stop_pre被使能。当预备停止信号stop_pre保持使能时,检测节点sn的电压电平可以下降到足够低于反相器224的阈值的电平,并且停止信号stop可以变得被使能为高逻辑电平。当停止信号stop被使能为高逻辑电平时,选通电路122可以提供系统时钟信号clkt作为时钟电平信号clk_lv,并且该时钟电平信号clk_lv可以具有低逻辑电平。基于时钟电平信号clk_lv,数据时钟生成电路130可以将数据时钟驱动信号dqsten和数据时钟信号dqst固定为低逻辑电平,并且可以将互补数据时钟驱动信号dqscen和互补数据时钟信号dqsc固定为高逻辑电平。可以基于电阻设置信号ron《1:n》来确定数据时钟发送器132的上拉驱动力和/或强度以及下拉驱动力和/或强度。因此,被固定为低逻辑电平的数据时钟信号dqst可以是能够通过其来测量半导体装置100的下拉电阻值的信号,并且被固定为高逻辑电平的互补数据时钟信号dqsc可以是能够通过其来测量半导体装置100的上拉电阻值的信号。

[0052]

图8是示出根据实施例的半导体装置800的配置的图。参考图8,半导体装置800可以包括内部时钟生成电路810、停止控制电路820和数据时钟生成电路830。内部时钟生成电路810可以包括分频电路813、延迟锁定环电路811和多相时钟生成电路812。数据时钟生成电路830可以包括触发电路831和数据时钟发送器832。半导体装置800还可以包括时钟接收器840和时钟分配网络850。半导体装置800可以包括与图1所示的半导体装置100相同的或相似的元件,并且将省略关于相同元件的重复描述。停止控制电路820可以接收多个内部时钟信号iclk、qclk、ibclk和qbclk以及参考时钟信号rclk,并且可以生成多个输出时钟信号iclko、qclko、ibclko和qbclko。停止控制电路820可以基于多个内部时钟信号iclk、qclk、ibclk和qbclk来生成停止信号stop。停止控制电路820可以检测多个内部时钟信号iclk、

qclk、ibclk和qbclk的逻辑电平以生成停止信号stop。基于参考时钟信号rclk和停止信号stop,停止控制电路820可以生成时钟电平信号clk_lv。当停止信号stop变为使能时,停止控制电路820可以提供参考时钟信号rclk作为时钟电平信号clk_lv。基于多个内部时钟信号iclk、qclk、ibclk和qbclk、停止信号stop以及时钟电平信号clk_lv,停止控制电路820可以生成多个输出时钟信号iclko、qclko、ibclko和qbclko。多个输出时钟信号iclko、qclko、ibclko和qbclko可以包括第一输出时钟信号iclko、第二输出时钟信号qclko、第三输出时钟信号ibclko和第四输出时钟信号qbclko。

[0053]

停止控制电路820可以包括停止信号生成电路821、选通电路822和输出时钟生成电路823。停止信号生成电路821可以接收多个内部时钟信号iclk、qclk、ibclk和qbclk。停止信号生成电路821可以检测多个内部时钟信号iclk、qclk、ibclk和qbclk的逻辑电平以生成停止信号stop。当多个内部时钟信号iclk、qclk、ibclk和qbclk全部具有相同的逻辑电平时,停止信号生成电路821可以使能停止信号stop。例如,当多个内部时钟信号iclk、qclk、ibclk和qbclk全部具有高逻辑电平时,停止信号生成电路821可以使能停止信号stop。当成对的系统时钟信号clkt和clkc的逻辑电平被固定时,从内部时钟生成电路810输出的第一至第四内部时钟信号iclk、qclk、ibclk和qbclk全部可以被固定为高逻辑电平。当第一至第四内部时钟信号iclk、qclk、ibclk和qbclk全部具有高逻辑电平时,停止信号生成电路821可以检测出成对的系统时钟信号clkt和clkc停止,并且可以使能停止信号stop。

[0054]

选通电路822可以接收参考时钟信号rclk和停止信号stop。选通电路822可以基于停止信号stop来对参考时钟信号rclk进行选通。当停止信号stop处于禁止状态中时,选通电路822可以阻止参考时钟信号rclk而不将参考时钟信号rclk提供为时钟电平信号clk_lv。当停止信号stop变为使能时,选通电路822可以提供参考时钟信号rclk作为时钟电平信号clk_lv。选通电路822可以包括与门。该与门可以接收参考时钟信号rclk和停止信号stop,并且可以对参考时钟信号rclk和停止信号stop执行与运算以输出时钟电平信号clk_lv。

[0055]

输出时钟生成电路823可以接收停止信号stop、时钟电平信号clk_lv以及多个内部时钟信号iclk、qclk、ibclk和qbclk。当停止信号stop处于禁止状态中时,输出时钟生成电路823可以提供多个内部时钟信号iclk、qclk、ibclk和qbclk作为多个输出时钟信号iclko、qclko、ibclko和qbclko。例如,输出时钟生成电路823可以提供第一内部时钟信号iclk作为第一输出时钟信号iclko,可以提供第二内部时钟信号qclk作为第二输出时钟信号qclko,可以提供第三内部时钟信号ibclk作为第三输出时钟信号ibclko,并且可以提供第四内部时钟信号qbclk作为第四输出时钟信号qbclko。当停止信号stop变为使能时,输出时钟生成电路823可以基于时钟电平信号clk_lv将多个输出时钟信号iclko、qclko、ibclko和qbclko固定为特定逻辑电平。例如,输出时钟生成电路823可以将第一内部时钟信号iclk和第三内部时钟信号ibclk固定为对应于时钟电平信号clk_lv的逻辑电平,并且可以将第二内部时钟信号qclk和第四内部时钟信号qbclk固定为与时钟电平信号clk_lv相反的逻辑电平。当时钟电平信号clk_lv具有高逻辑电平时,输出时钟生成电路823可以将第一输出时钟信号iclko和第三输出时钟信号ibclko固定为高逻辑电平,并且可以将第二输出时钟信号qclko和第四输出时钟信号qbclko固定为低逻辑电平。当时钟电平信号clk_lv具有低逻辑电平时,输出时钟生成电路823可以将第一输出时钟信号iclko和第三输出时钟信号

ibclko固定为低逻辑电平,并且可以将第二输出时钟信号qclko和第四输出时钟信号qbclko固定为高逻辑电平。

[0056]

时钟分配网络850可以耦接到输出时钟生成电路823,并且可以接收多个输出时钟信号iclko、qclko、ibclko和qbclko。时钟分配网络850可以驱动多个输出时钟信号iclko、qclko、ibclko和qbclko以向数据时钟生成电路830提供上述多个输出时钟信号iclko、qclko、ibclko和qbclko。基于多个输出时钟信号iclko、qclko、ibclko和qbclko,数据时钟生成电路830可以生成数据时钟信号dqst和互补数据时钟信号dqsc。

[0057]

图9是示出图8所示的输出时钟生成电路823的配置的图。参考图9,输出时钟生成电路823可以包括电平信号生成器910和输出时钟驱动器920。电平信号生成器910可以接收停止信号stop和时钟电平信号clk_lv,并且可以基于停止信号stop和时钟电平信号clk_lv来生成第一电平信号lvh和第二电平信号lvl。当停止信号stop变得禁止时,电平信号生成器910可以将第一电平信号lvh和第二电平信号lvl固定为相同的逻辑电平。例如,电平信号生成器910可以将第一电平信号lvh和第二电平信号lvl固定为高逻辑电平。当停止信号stop变得使能时,电平信号生成器910可以根据时钟电平信号clk_lv将第一电平信号lvh和第二电平信号lvl固定为彼此不同的逻辑电平。当时钟电平信号clk_lv具有高逻辑电平时,电平信号生成器910可以将第一电平信号lvh固定为高逻辑电平,并且可以将第二电平信号lvl固定为低逻辑电平。当时钟电平信号clk_lv具有低逻辑电平时,电平信号生成器910可以将第一电平信号lvh固定为低逻辑电平,并且可以将第二电平信号lvl固定为高逻辑电平。

[0058]

电平信号生成器910可以包括第一多路复用器911、反相器912和第二多路复用器913。第一多路复用器911可以接收第一电源电压vdd、时钟电平信号clk_lv和停止信号stop。基于停止信号stop,第一多路复用器911可以输出第一电源电压vdd和时钟电平信号clk_lv之一作为第一电平信号lvh。当停止信号stop变为禁止时,第一多路复用器911可以输出第一电源电压vdd作为第一电平信号lvh。当停止信号stop变为使能时,第一多路复用器911可以输出时钟电平信号clk_lv作为第一电平信号lvh。反相器912可以接收时钟电平信号clk_lv,并且可以使时钟电平信号clk_lv反相以输出互补时钟电平信号clk_lvb。第二多路复用器913可以接收第一电源电压vdd、反相器912的输出和停止信号stop。基于停止信号stop,第二多路复用器913可以输出第一电源电压vdd和互补时钟电平信号clk_lvb之一作为第二电平信号lvl。当停止信号stop变为禁止时,第二多路复用器913可以输出第一电源电压vdd作为第二电平信号lvl。当停止信号stop变为使能时,第二多路复用器913可以输出互补时钟电平信号clk_lvb作为第二电平信号lvl。

[0059]

输出时钟驱动器920可以接收多个内部时钟信号iclk、qclk、ibclk和qbclk、第一电平信号lvh和第二电平信号lvl。输出时钟驱动器920可以基于多个内部时钟信号iclk、qclk、ibclk和qbclk、第一电平信号lvh和第二电平信号lvl来生成多个输出时钟信号iclko、qclko、ibclko和qbclko。输出时钟驱动器920可以基于第一内部时钟信号iclk、第一电平信号lvh和第二电平信号lvl来生成第一输出时钟信号iclko。当第一电平信号lvh和第二电平信号lvl被固定为相同的逻辑电平时,输出时钟驱动器920可以提供第一内部时钟信号iclk作为第一输出时钟信号iclko。当第一电平信号lvh和第二电平信号lvl具有彼此不同的逻辑电平时,输出时钟驱动器920可以将第一输出时钟信号iclko固定为高逻辑电平和

低逻辑电平之一。输出时钟驱动器920可以基于第二内部时钟信号qclk、第一电平信号lvh和第二电平信号lvl来生成第二输出时钟信号qclko。当第一电平信号lvh和第二电平信号lvl被固定为相同的逻辑电平时,输出时钟驱动器920可以提供第二内部时钟信号qclk作为第二输出时钟信号qclko。当第一电平信号lvh和第二电平信号lvl具有彼此不同的逻辑电平时,输出时钟驱动器920可以将第二输出时钟信号qclko固定为高逻辑电平和低逻辑电平之一。输出时钟驱动器920可以基于第三内部时钟信号ibclk、第一电平信号lvh和第二电平信号lvl来生成第三输出时钟信号ibclko。当第一电平信号lvh和第二电平信号lvl被固定为相同的逻辑电平时,输出时钟驱动器920可以提供第三内部时钟信号ibclk作为第三输出时钟信号ibclko。当第一电平信号lvh和第二电平信号lvl具有彼此不同的逻辑电平时,输出时钟驱动器920可以将第三输出时钟信号ibclko固定为高逻辑电平和低逻辑电平之一。输出时钟驱动器920可以基于第四内部时钟信号qbclk、第一电平信号lvh和第二电平信号lvl来生成第四输出时钟信号qbclko。当第一电平信号lvh和第二电平信号lvl相同的逻辑电平时,输出时钟驱动器920可以提供第四内部时钟信号qbclk作为第四输出时钟信号qbclko。当第一电平信号lvh和第二电平信号lvl具有彼此不同的逻辑电平时,输出时钟驱动器920可以将第四输出时钟信号qbclko固定为高逻辑电平和低逻辑电平之一。

[0060]

输出时钟驱动器920可以包括第一与非门921、第二与非门922、第三与非门923、第四与非门924、第五与非门925、第六与非门926、第七与非门927以及第八与非门928。第一与非门921可以接收第一电平信号lvh和第一内部时钟信号iclk。第二与非门922可以接收第二电平信号lvl和第一与非门921的输出以输出第一输出时钟信号iclko。第三与非门923可以接收第二电平信号lvl和第二内部时钟信号qclk。第四与非门924可以接收第一电平信号lvh和第三与非门923的输出以输出第二输出时钟信号qclko。第五与非门925可以接收第一电平信号lvh和第三内部时钟信号ibclk。第六与非门926可以接收第二电平信号lvl和第五与非门925的输出以输出第三输出时钟信号ibclko。第七与非门927可以接收第二电平信号lvl和第四内部时钟信号qbclk。第八与非门928可以接收第一电平信号lvh和第七与非门927的输出以输出第四输出时钟信号qbclko。

[0061]

图10是示出图8所示的触发电路831的配置的图。参考图10,触发电路831可以包括第一触发电路1010和第二触发电路1050。第一触发电路1010可以接收多个输出时钟信号iclko、qclko、ibclko和qbclko,并且可以基于多个输出时钟信号iclko、qclko、ibclko和qbclko来生成数据时钟驱动信号dqsten。第二触发电路1050可以接收多个输出时钟信号iclko、qclko、ibclko和qbclko,并且可以基于多个输出时钟信号iclko、qclko、ibclko和qbclko来生成互补数据时钟驱动信号dqscen。第一触发电路1010和第二触发电路1050可以接收从输出时钟生成电路823生成的多个输出时钟信号iclko、qclko、ibclko和qbclko,并且因此不需要接收停止信号stop和时钟电平信号clk_lv。

[0062]

第一触发电路1010可以包括第一与非门1011、第二与非门1012、第三与非门1013、第四与非门1014、第一反相器1021、第二反相器1022、第三反相器1023、第四反相器1024、第五反相器1025、第六反相器1026、第七反相器1027、第八反相器1028、第五与非门1031、第六与非门1032、第七与非门1033、第八与非门1034、第九与非门1041、第十与非门1042、第九反相器1043、第十反相器1044以及与门1045。第一与非门1011可以接收第二电源电压vss和第一输出时钟信号iclko。第二与非门1012可以接收第二电源电压vss和第三输出时钟信号

ibclko。第三与非门1013可以接收第一电源电压vdd和第二输出时钟信号qclko。第四与非门1014可以接收第一电源电压vdd和第四输出时钟信号qbclko。第一反相器1021可以接收第一与非门1011的输出并且可以使第一与非门1011的输出反相。第二反相器1022可以接收第二输出时钟信号qclko并且可以使第二输出时钟信号qclko反相。第三反相器1023可以接收第二与非门1012的输出并且可以使第二与非门1012的输出反相。第四反相器1024可以接收第四输出时钟信号qbclko并且可以使第四输出时钟信号qbclko反相。第五反相器1025可以接收第三与非门1013的输出并且可以使第三与非门1013的输出反相。第六反相器1026可以接收第三输出时钟信号ibclko并且可以使第三输出时钟信号ibclko反相。第七反相器1027可以接收第四与非门1014的输出并且可以使第四与非门1014的输出反相。第八反相器1028可以接收第一输出时钟信号iclko并且可以使第一输出时钟信号iclko反相。

[0063]

第五与非门1031可以接收第一反相器1021的输出和第二反相器1022的输出。第六与非门1032可以接收第三反相器1023的输出和第四反相器1024的输出。第七与非门1033可以接收第五反相器1025的输出和第六反相器1026的输出。第八与非门1034可以接收第七反相器1027的输出和第八反相器1028的输出。第九与非门1041可以接收第五与非门1031的输出和第六与非门1032的输出。第十与非门1042可以接收第七与非门1033的输出和第八与非门1034的输出。第九反相器1043可以接收第九与非门1041的输出并且可以使第九与非门1041的输出反相。第十反相器1044可以接收第十与非门1042的输出并且可以使第十与非门1042的输出反相。与门1045可以接收第九反相器1043的输出和第十反相器1044的输出,并且可以生成数据时钟驱动信号dqsten。

[0064]

第二触发电路1050可以包括第一与非门1051、第二与非门1052、第三与非门1053、第四与非门1054、第一反相器1061、第二反相器1062、第三反相器1063、第四反相器1064、第五反相器1065、第六反相器1066、第七反相器1067、第八反相器1068、第五与非门1071、第六与非门1072、第七与非门1073、第八与非门1074、第九与非门1081、第十与非门1082、第九反相器1083、第十反相器1084以及与门1085。第一与非门1051可以接收第一电源电压vdd和第一输出时钟信号iclko。第二与非门1052可以接收第一电源电压vdd和第三输出时钟信号ibclko。第三与非门1053可以接收第二电源电压vss和第二输出时钟信号qclko。第四与非门1054可以接收第二电源电压vss和第四输出时钟信号qbclko。第一反相器1061可以接收第一与非门1051的输出并且可以使第一与非门1051的输出反相。第二反相器1062可以接收第二输出时钟信号qclko并且可以使第二输出时钟信号qclko反相。第三反相器1063可以接收第二与非门1052的输出并且可以使第二与非门1052的输出反相。第四反相器1064可以接收第四输出时钟信号qbclko并且可以使第四输出时钟信号qbclko反相。第五反相器1065可以接收第三与非门1053的输出并且可以使第三与非门1053的输出反相。第六反相器1066可以接收第三输出时钟信号ibclko并且可以使第三输出时钟信号ibclko反相。第七反相器1067可以接收第四与非门1054的输出并且可以使第四与非门1054的输出反相。第八反相器1068可以接收第一输出时钟信号iclko并且可以使第一输出时钟信号iclko反相。

[0065]

第五与非门1071可以接收第一反相器1061的输出和第二反相器1062的输出。第六与非门1072可以接收第三反相器1063的输出和第四反相器1064的输出。第七与非门1073可以接收第五反相器1065的输出和第六反相器1066的输出。第八与非门1074可以接收第七反相器1067的输出和第八反相器1068的输出。第九与非门1081可以接收第五与非门1071的输

出和第六与非门1072的输出。第十与非门1082可以接收第七与非门1073的输出和第八与非门1074的输出。第九反相器1083可以接收第九与非门1081的输出并且可以使第九与非门1081的输出反相。第十反相器1084可以接收第十与非门1082的输出并且可以使第十与非门1082的输出反相。与门1085可以接收第九反相器1083的输出和第十反相器1084的输出,并且可以生成互补数据时钟驱动信号dqscen。

[0066]

当第一输出时钟信号iclko和第二输出时钟信号qclko具有低逻辑电平并且第三输出时钟信号ibclko和第四输出时钟信号qbclko具有高逻辑电平时,第一触发电路1010可以将数据时钟驱动信号dqsten禁止为低逻辑电平,并且第二触发电路1050可以将互补数据时钟驱动信号dqscen使能为高逻辑电平。当第一输出时钟信号iclko和第四输出时钟信号qbclko具有高逻辑电平并且第二输出时钟信号qclko和第三输出时钟信号ibclko具有低逻辑电平时,第一触发电路1010可以将数据时钟驱动信号dqsten使能为高逻辑电平,并且第二触发电路1050可以将互补数据时钟驱动信号dqscen禁止为低逻辑电平。当第一输出时钟信号iclko和第二输出时钟信号qclko具有高逻辑电平并且第三输出时钟信号ibclko和第四输出时钟信号qbclko具有低逻辑电平时,第一触发电路1010可以将数据时钟驱动信号dqsten禁止为低逻辑电平,并且第二触发电路1050可以将互补数据时钟驱动信号dqscen使能为高逻辑电平。当第一输出时钟信号iclko和第四输出时钟信号qbclko具有低逻辑电平,并且第二输出时钟信号qclko和第三输出时钟信号ibclko具有高逻辑电平时,第一触发电路1010可以将数据时钟驱动信号dqsten使能为高逻辑电平,并且第二触发电路1050可以将互补数据时钟驱动信号dqscen禁止为低逻辑电平。当第一输出时钟信号iclko和第三输出时钟信号ibclko具有高逻辑电平并且第二输出时钟信号qclko和第四输出时钟信号qbclko具有低逻辑电平时,第一触发电路1010可以将数据时钟驱动信号dqsten使能为高逻辑电平,并且第二触发电路1050可以将互补数据时钟驱动信号dqscen禁止为低逻辑电平。当第一输出时钟信号iclko和第三输出时钟信号ibclko具有低逻辑电平并且第二输出时钟信号qclko和第四输出时钟信号qbclko具有高逻辑电平时,第一触发电路1010可以将数据时钟驱动信号dqsten禁止为逻辑低电平,并且第二触发电路1050可以将互补数据时钟驱动信号dqscen使能为高逻辑电平。

[0067]

图11是示出根据实施例的半导体装置1100的配置的图。参考图11,半导体装置1100可以包括时钟接收器(rx)1140、分频电路1113、延迟锁定环电路1111、时钟分配网络1150、多相时钟生成电路1112、停止信号生成电路1121、选通电路1122、触发电路1131和数据时钟发送器(tx)1132。除了一些元件的连接关系之外,半导体装置1100可以具有与图1所示的半导体装置100相同的配置。在半导体装置1100内部,时钟分配网络1150可以耦接在延迟锁定环电路1111和多相时钟生成电路1112之间。时钟分配网络1150可以接收从延迟锁定环电路1111生成的延迟锁定时钟信号clkdll。如由图中的

‘

a’表示的,时钟分配网络1150可以驱动延迟锁定时钟信号clkdll以向多相时钟生成电路1112提供延迟锁定时钟信号clkdll。多相时钟生成电路1112可以接收延迟锁定时钟信号clkdll,并且可以基于延迟锁定时钟信号clkdll来生成多个内部时钟信号iclk、qclk、ibclk和qbclk。触发电路1131可以从多相时钟生成电路1112接收多个内部时钟信号iclk、qcvlk、ibclk和qbclk。

[0068]

图12是示出根据实施例的半导体装置1200的配置的图。参考图12,半导体装置1200可以包括时钟接收器(rx)1240、分频电路1213、延迟锁定环电路1211、时钟分配网络

1250、多相时钟生成电路1212、停止信号生成电路1221、选通电路1222、输出时钟生成电路1223、触发电路1231和数据时钟发送器(tx)1232。除了一些元件的连接关系之外,半导体装置1200可以具有与图8所示的半导体装置800相同的配置。在半导体装置1200内部,时钟分配网络1250可以耦接在延迟锁定环电路1211和多相时钟生成电路1212之间。时钟分配网络1250可以接收从延迟锁定环电路1211生成的延迟锁定时钟信号clkdll。如由图中的

‘

b’表示的,时钟分配网络1250可以驱动延迟锁定时钟信号clkdll以向多相时钟生成电路1212提供延迟锁定时钟信号clkdll。多相时钟生成电路1212可以接收延迟锁定时钟信号clkdll,并且可以基于延迟锁定时钟信号clkdll来生成多个内部时钟信号iclk、qclk、ibclk和qbclk。

[0069]

图13是示出根据实施例的半导体系统1300的配置的图。参考图13,半导体系统1300可以包括第一半导体装置1310和第二半导体装置1320。第一半导体装置1310可以提供第二半导体装置1320进行操作所需要的各个控制信号。第一半导体装置1310可以包括各种类型的主机器件。例如,第一半导体装置1310可以包括中央处理单元(cpu)、图形处理单元(gpu)、多媒体处理器(mmp)、数字信号处理器、应用处理器(ap)和存储控制器中的至少一个。例如,第二半导体装置1320可以是存储器件,并且存储器件可以包括易失性存储器和非易失性存储器。易失性存储器可以包括静态随机存取存储器(静态ram:sram)、动态ram(dram)和同步dram(sdram)。非易失性存储器可以包括只读存储器(rom)、可编程rom(prom)、电可擦除可编程只读存储器(eeprom)、电可编程rom(eprom)、闪速存储器、相变ram(pram)、磁性ram(mram)、电阻式ram(rram)和铁电ram(fram)等。

[0070]

第二半导体装置1320可以通过多个总线耦接到第一半导体装置1310。多个总线可以是用于传递信号的信号传输路径、链路或通道。多个总线可以包括系统时钟总线1301、命令总线1302和数据时钟总线1303。系统时钟总线1301和命令总线1302中的每一个可以是单向总线,并且数据时钟总线1303可以是双向总线。第二半导体装置1320可以通过系统时钟总线1301耦接到第一半导体装置1310,并且可以通过系统时钟总线1301从第一半导体装置1310接收系统时钟信号clkt。系统时钟信号clkt可以与互补系统时钟信号clkc一起被传送。第二半导体装置1320可以通过命令总线1302耦接到第一半导体装置1310,并且可以通过命令总线1302从第一半导体装置1310接收命令信号cmd。第二半导体装置1320可以与系统时钟信号clkt同步来接收命令信号cmd。第二半导体装置1320可以通过数据时钟总线1303耦接到第一半导体装置1310。第二半导体装置1320可以从第一半导体装置1310接收成对的数据时钟信号dqst和dqsc,或者可以通过数据时钟总线1303向第一半导体装置1310传送成对的数据时钟信号dqst和dqsc。

[0071]

第一半导体装置1310可以包括系统时钟生成电路1311、命令生成电路1312和监测电路1313。系统时钟生成电路1311可以生成成对的系统时钟信号clkt和clkc。系统时钟生成电路1311可以包括周期信号生成电路,并且可以生成以预定周期切变的成对的系统时钟信号clkt和clkc。系统时钟生成电路1311可以利用诸如振荡电路和锁相环电路等的时钟生成电路来实施。通过系统时钟总线1301,系统时钟生成电路1311可以向第二半导体装置1320提供成对的系统时钟信号clkt和clkc。命令生成电路1312可以生成用于使第二半导体装置1320执行各种操作的各种命令信号。上述各种命令信号可以包括激活命令信号、读命令信号、写命令信号和刷新命令信号等。为了设置第二半导体装置1320的操作参数,命令生

成电路1312可以生成包括关于操作参数的信息的命令信号cmd。通过命令总线1302,命令生成电路1312可以向第二半导体装置1320提供命令信号cmd。监测电路1313可以耦接到数据时钟总线1303,并且可以通过数据时钟总线1303接收从第二半导体装置1320提供的成对的数据时钟信号dqst和dqsc。监测电路1313可以监测上述成对的数据时钟信号dqst和dqsc的电压电平,并且可以向命令生成电路1312提供监测的结果mnt。当接收被固定为不同逻辑电平的成对的数据时钟信号dqst和dqsc时,监测电路1313可以检测成对的数据时钟信号dqst和dqsc的电压电平。命令生成电路1312可以从监测电路1313接收监测的结果mnt,并且可以生成用于设置第二半导体装置1320的操作参数的命令信号cmd。

[0072]

第二半导体装置1320可以包括时钟接收器(rx)1321、内部时钟生成电路1322、时钟分配网络1323、数据时钟生成电路1324、停止控制电路1325、命令解码器1326和模式设置电路1327。时钟接收器1321可以耦接到系统时钟总线1301,并且可以通过系统时钟总线1301接收成对的系统时钟信号clkt和clkc。时钟接收器1321可以缓冲成对的系统时钟信号clkt和clkc以生成参考时钟信号rclk。内部时钟生成电路1322可以接收参考时钟信号rclk,并且可以基于参考时钟信号rclk来生成具有不同相位的多个内部时钟信号inclk。时钟分配网络1323可以接收从内部时钟生成电路1322生成的多个内部时钟信号inclk。时钟分配网络1323可以驱动多个内部时钟信号inclk并且可以向数据时钟生成电路1324提供被驱动的时钟信号。

[0073]

数据时钟生成电路1324可以接收从时钟分配网络1323提供的时钟信号,并且可以基于所接收的时钟信号来生成成对的数据时钟信号dqst和dqsc。数据时钟生成电路1324可以包括触发电路1324-1和数据时钟发送器(tx)1324-2。触发电路1324-1可以基于来自时钟分配网络1323的时钟信号来生成数据时钟驱动信号dqsten和互补数据时钟驱动信号dqscen。数据时钟发送器1324-2可以基于数据时钟驱动信号dqsten来生成数据时钟信号dqst,并且可以基于互补数据时钟驱动信号dqscen来生成互补数据时钟信号dqsc。数据时钟发送器1324-2可以接收电阻设置信号ron《1:n》,并且可以基于电阻设置信号ron《1:n》来设置用于驱动数据时钟信号dqst和互补数据时钟信号dqsc的驱动力和/或强度。

[0074]

当成对的系统时钟信号clkt和clkc停止时,停止控制电路1325可以将成对的数据时钟信号dqst和dqsc固定为不同的逻辑电平。停止控制电路1325可以耦接在内部时钟生成电路1322和时钟分配网络1323之间。图1、8、11和12所示的半导体装置100、800、1100和1200内的元件之间的连接关系中的任何一种可以被应用为内部时钟生成电路1322、停止控制电路1325、时钟分配网络1323和数据时钟生成电路1324之间的连接关系。第二半导体装置1320还可以包括多个数据时钟生成电路。时钟分配网络1323可以向包括数据时钟生成电路1324的所有数据时钟生成电路分配时钟信号。

[0075]

命令解码器1326可以通过命令总线1302接收从第一半导体装置1310提供的命令信号cmd。命令解码器1326可以解码命令信号cmd以生成各种内部命令信号。模式设置电路1327可以在其中存储第二半导体装置1320的各种操作参数。上述各种操作参数可以包括第二半导体装置1320的操作电阻值。模式设置电路1327可以向数据时钟生成电路1324的数据时钟发送器1324-2提供用于确定第二半导体装置1320的操作电阻值的电阻设置信号ron《1:n》。当第二半导体装置1320从第一半导体装置1310接收关于电阻设置的命令信号cmd时,模式设置电路1327可以基于内部命令信号来改变电阻设置信号ron《1:n》的值。

[0076]

第一半导体装置1310可以停止系统时钟信号以测量数据时钟发送器1324-2的操作电阻值。第一半导体装置1310可以将成对的系统时钟信号clkt和clkc固定为不同的逻辑电平以停止成对的系统时钟信号clkt和clkc。通过停止控制电路1325,第二半导体装置1320可以将成对的数据时钟信号dqst和dqsc固定为不同的逻辑电平。监测电路1313可以监测被固定为不同逻辑电平的成对的数据时钟信号dqst和dqsc以生成监测的结果mnt。命令生成电路1312可以生成关于电阻设置的命令信号cmd。基于命令信号cmd,第二半导体装置1320可以调整电阻设置信号ron《1:n》的值。基于电阻设置信号ron《1:n》,数据时钟发送器1324-2可以调整用于驱动成对的数据时钟信号dqst和dqsc的驱动力和/或强度。

[0077]

尽管已经在上面描述了某些实施例,但本领域的技术人员将理解,所描述的实施例仅仅作为示例。因此,不应当基于描述的实施例来限制包括时钟路径的半导体装置。相反,在本文描述的包括时钟路径的半导体装置应当结合以上描述和附图仅根据所附权利要求来限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1