存储芯片上的控制电路和动态随机存储器的制作方法

本公开实施例涉及半导体,尤其涉及一种存储芯片上的控制电路和动态随机存储器。

背景技术:

1、在半导体技术领域中,存储芯片(die)可以堆叠放置,以降低半导体产品的高度,节约空间。例如,可以将每两个存储芯片以电路侧相对的方式堆叠,称为面对面堆叠。半导体产品中可以包括一组或多组面对面堆叠的存储芯片。

2、现有技术中,在上述面对面堆叠的方案中,每一存储芯片中的功能电路按照堆叠顺序运行。例如,在奇数位置的存储芯片中,信号流向是存储芯片的第一连接件经由功能电路到达存储芯片的第二连接件,在偶数位置的存储芯片中,信号流向是存储芯片的第二连接件经由功能电路到达存储芯片的第一连接件。

3、然而,上述方案导致存储芯片设计成本、生产成本和生产复杂度均较高。

技术实现思路

1、本公开实施例提供一种存储芯片上的控制电路和动态随机存储器,可以降低设计成本、生产成本和生产复杂度。

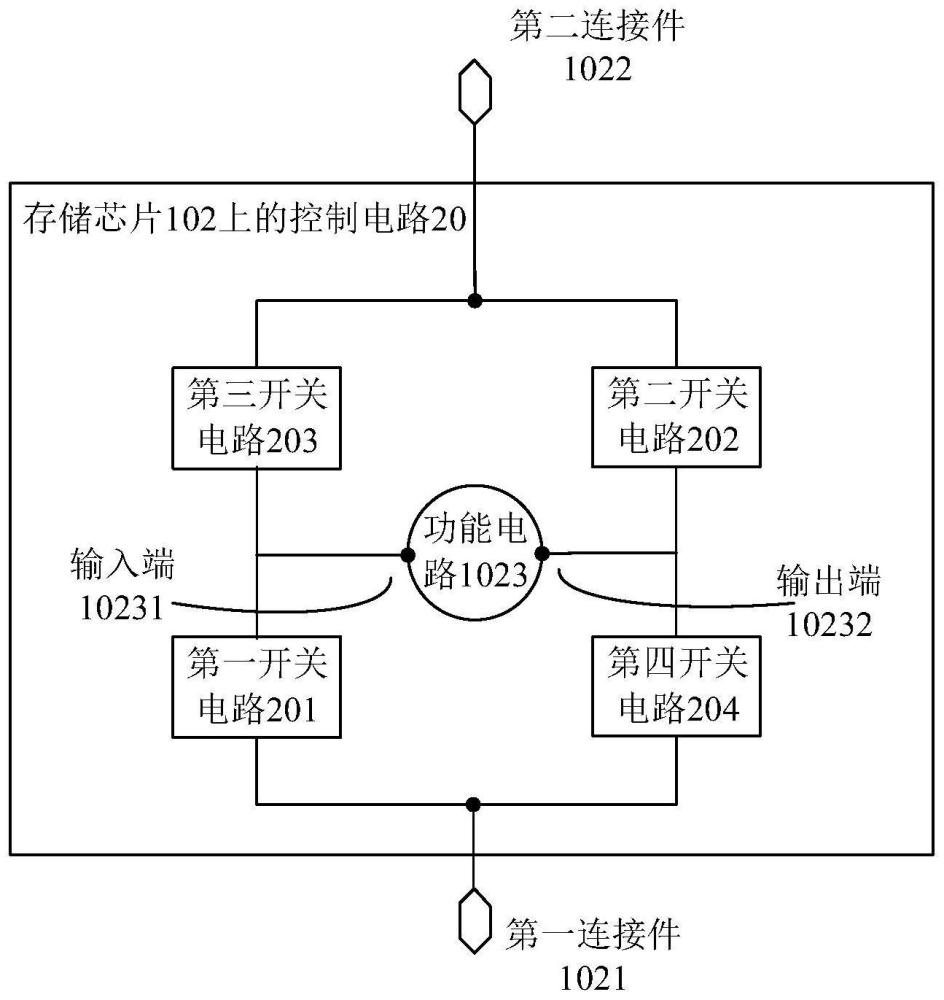

2、第一方面,本公开实施例提供一种控制电路,包括:开关电路以及功能电路,所述开关电路包括第一开关电路至第四开关电路;

3、其中,所述存储芯片的第一连接件经由所述第一开关电路与所述功能电路的输入端连接,以及,所述功能电路的输出端经由第二开关电路与所述存储芯片的第二连接件连接,所述第一开关电路和所述第二开关电路对应相同的第一开关状态;

4、所述第二连接件经由所述第三开关电路与同一所述功能电路的输入端连接,以及,同一所述功能电路的输出端经由第四开关电路与所述第一连接件连接,所述第三开关电路和所述第四开关电路对应相同的第二开关状态,所述第一开关状态与所述第二开关状态相反;

5、所述开关电路用于基于所在的所述存储芯片的位置奇偶信号控制所述第一开关状态或所述第二开关状态为导通状态,所述位置奇偶信号具有唯一对应的所述第一连接件、所述功能电路和所述第二连接件的连接顺序。

6、在一些实施方式中,所述第一开关电路和所述第二开关电路对应相同的第一导通条件,所述第三开关电路和所述第四开关电路对应相同的第二导通条件,所述第一导通条件和所述第二导通条件相反,所述第一开关电路至所述第四开关电路的控制端均接入所述位置奇偶信号,所述位置奇偶信号满足所述第一导通条件或所述第二导通条件。

7、在一些实施方式中,所述第一开关电路至所述第四开关电路均对应相同的导通条件,所述第一开关电路的控制端和所述第二开关电路的控制端均接入相同的第一控制信号;所述第三开关电路的控制端和所述第四开关电路的控制端均接入相同的第二控制信号;所述位置奇偶信号用于指示所述第一控制信号或所述第二控制信号满足所述导通条件。

8、在一些实施方式中,所述控制电路还包括控制信号生成电路,所述控制信号生成电路的输入端接入所述位置奇偶信号,用于根据所述位置奇偶信号生成所述第一控制信号和所述第二控制信号,并通过第一输出端和第二输出端分别输出所述第一控制信号和所述第二控制信号;

9、所述第一开关电路的控制端和所述第二开关电路的控制端均与所述第一输出端连接;

10、所述第三开关电路的控制端和所述第四开关电路的控制端均与所述第二输出端连接。

11、在一些实施方式中,所述第一开关电路至所述第四开关电路均为单向导通的电路,所述第一开关电路的导通方向和所述第二开关电路的导通方向均与所述第一连接件至所述第二连接件的方向一致,所述第三开关电路的导通方向和所述第四开关电路的导通方向均与所述第二连接件至所述第一连接件的方向一致。

12、在一些实施方式中,所述第一开关电路至所述第四开关电路均包括驱动电路。

13、在一些实施方式中,所述功能电路包括以下至少一种:数据递增电路、上电电路、数据传输电路,所述数据递增电路用于对所述存储芯片接收到的第一数据进行递增得到所述存储芯片使用的第二数据,所述上电电路用于按照所述存储芯片之间的顺序对所述存储芯片进行上电,所述数据传输电路用于按照所述存储芯片之间的顺序进行数据传输。

14、在一些实施方式中,所述数据递增电路包括n个递增子电路,第m个所述递增子电路用于根据所述第一数据中的第1位至第m位数据,生成所述第二数据的第m位数据,n是大于或等于2的正整数,m是大于或等于1且小于或等于所述n的正整数;

15、每个所述递增子电路对应一个所述开关电路,所述存储芯片的第一连接件经由所述开关电路中的所述第一开关电路与所述开关电路对应的所述递增子电路的输入端连接,以及,所述递增子电路的输出端经由对应的所述开关电路中的所述第二开关电路与所述存储芯片的第二连接件连接;

16、所述第二连接件经由所述开关电路中的所述第三开关电路与对应的所述递增子电路的输入端连接,以及,所述递增子电路的输出端经由对应的所述开关电路中的所述第四开关电路与所述第一连接件连接,所述存储芯片中不同所述递增子电路对应相同的所述位置奇偶信号。

17、在一些实施方式中,第1个所述递增子电路包括非门,所述非门的输入是所述第一数据中的第1位数据,所述非门用于根据所述第一数据中的第1位数据,生成所述第二数据中的第1位数据;

18、第2个所述递增子电路包括异或门,第2个所述递增子电路的所述异或门用于根据所述第一数据的第1位数据和第2位数据生成所述第二数据的第2位数据;

19、当所述n是大于或等于3的正整数时,第m个所述递增子电路包括与门和异或门,m是大于或等于3且小于或等于所述n的正整数,第m个所述递增子电路包括的与门用于确定所述第一数据的第1至第m-1位数据的与结果,所述第m个所述递增子电路的所述异或门用于根据所述与结果和所述第一数据中的第m位数据生成所述第二数据的第m位数据。

20、在一些实施例中,所述第一连接件包括硅通孔,所述第二连接件包括混合键合。

21、第二方面,本公开实施例提供了一种动态随机存储器,包括面对面堆叠的多个存储芯片,所述存储芯片上设置有第一方面所述的存储芯片上的控制电路。

22、在一些实施方式中,所述存储芯片上设置有至少两个传输通道,所述存储芯片的所述传输通道与相邻存储芯片的传输通道错位连接,用于与所述相邻存储芯片基于相同位置的传输通道获取不同的所述位置信息,且多个所述存储芯片的所述传输通道的错位方向相同,所述存储芯片的其中一个所述传输通道获取的所述位置信息作为所述存储芯片的位置奇偶信号,所述位置信息指示所述存储芯片在所述动态随机存储器中的位置为奇数位置或偶数位置。

23、在一些实施方式中,每个所述存储芯片上的所述传输通道为偶数个,与逻辑芯片连接的最底层存储芯片中的相邻传输通道对应不同的位置信息,所述最底层存储芯片上间隔的所述传输通道对应同一位置信息。

24、在一些实施方式中,还包括:数据读取电路,用于读取任意一个所述传输通道输出的所述位置信息,不同所述存储芯片的所述数据读取电路读取的所述传输通道在对应存储芯片上的位置相同。

25、本公开实施例提供的存储芯片上的控制电路和动态随机存储器,可以为不同存储芯片设置相同的控制电路,但通过开关电路实现不同存储芯片的电路连接关系不同。这样,只需要一套存储芯片的掩膜版即可,可以降低掩膜版的设计成本和生产成本,降低生产复杂度。

- 还没有人留言评论。精彩留言会获得点赞!