模拟缓存器及其操作方法、信号处理装置

本公开的实施例涉及一种模拟缓存器及其操作方法、信号处理装置。

背景技术:

1、随着信息技术的高速发展,运行速度的提升和能耗的降低成为了传统冯诺依曼计算架构发展的瓶颈。存算一体系统由于具有存算融合的功能,可在存储的数据上原位实现计算操作,能够消除传统冯诺依曼架构中计算单元和内存单元之间的数据移动,从而实现了高效的信息处理。但是,在存算一体系统的外围电路中,模数转换器、数模转换器和片上数字缓存器等电路给整个系统带来了很大的面积与功耗开销,同时造成了严重的时间延迟。

技术实现思路

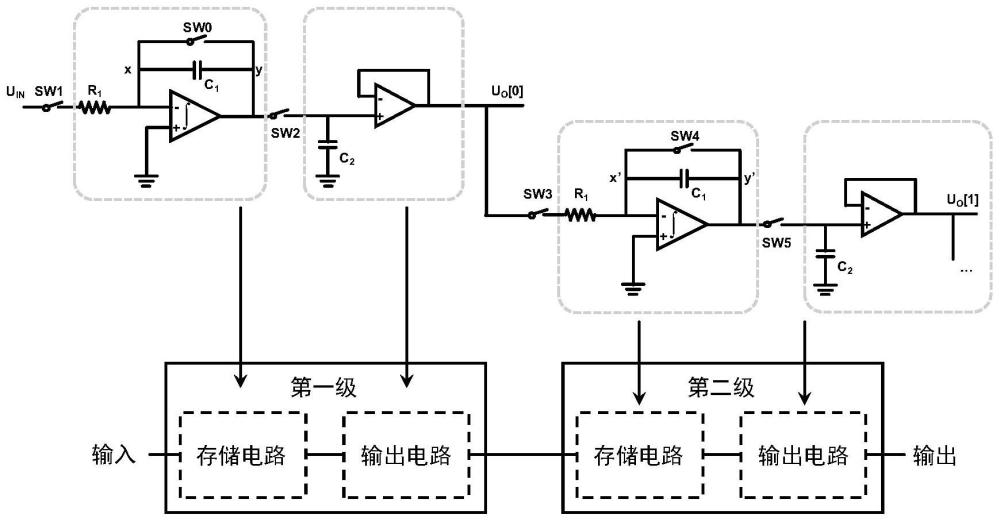

1、本公开至少一实施例提供一种模拟缓存器,该模拟缓存器包括级联的多个模拟缓存单元,其中,所述多个模拟缓存单元中每个包括输入电路、存储电路、隔离电路和输出电路,所述输入电路配置为根据输入控制信号导通或截止以开始接收或者停止接收输入信号;所述存储电路配置为从所述输入电路接收所述输入信号,并将采集到的输入信号以模拟数据的形式缓存在所述存储电路中;所述隔离电路配置为根据隔离控制信号控制所述存储电路和所述输出电路电连接或断开;所述输出电路配置为在与所述存储电路电连接时接收并缓存所述存储电路中缓存的所述模拟数据,并将所述模拟数据输出,其中,所述多个模拟缓存单元中的第一级模拟缓存单元的所述输入电路与输入信号源连接,除了所述第一级模拟缓存单元之外的任一当前级模拟缓存单元的所述输入电路与前一级模拟缓存单元的所述输出电路连接。

2、例如,本公开至少一实施例提供的模拟缓存器,还包括复位电路,其中,所述复位电路配置为对所述存储电路进行复位和/或对所述输出电路进行复位。

3、例如,在本公开至少一实施例提供的模拟缓存器中,其中,所述存储电路包括积分电路,所述积分电路配置为对所述输入信号进行积分处理,并将所述积分处理的对应于所述输入信号的处理结果以所述模拟数据缓存。

4、例如,在本公开至少一实施例提供的模拟缓存器中,所述积分电路包括电连接的第一电阻、第一电容和第一运算放大器,所述第一运算放大器的第一输入端与所述第一电阻和所述第一电容连接,所述第一运算放大器的第二输入端与第一地端连接,所述第一运算放大器的输出端与所述隔离电路的输入端连接,所述第一电容配置为将所述积分处理的对应于所述输入信号的处理结果以所述模拟数据缓存。

5、例如,在本公开至少一实施例提供的模拟缓存器中,其中,所述输出电路包括电连接的复制单元和缓冲器,所述复制单元配置为复制并缓存所述存储电路中缓存的所述模拟数据;所述缓冲器配置为将所述复制单元中缓存的模拟数据输出。

6、例如,在本公开至少一实施例提供的模拟缓存器中,所述复制单元包括第二电容,所述缓冲器包括第二运算放大器,所述第二电容的第一极连接在所述隔离电路和所述第二运算放大器的第一输入端之间,所述第二电容的第二极与第二地端连接,所述第二运算放大器的第二输入端与所述第二运算放大器的输出端连接。

7、例如,在本公开至少一实施例提供的模拟缓存器中,其中,所述输入电路包括第一开关,所述第一开关的第一极和第二极分别连接所述输入信号源和所述存储电路,所述第一开关的控制极接收所述输入控制信号。

8、例如,在本公开至少一实施例提供的模拟缓存器中,其中,所述隔离电路包括第二开关,所述第二开关的第一极和第二极分别连接所述存储电路和所述输出电路,所述第二开关的控制极接收所述隔离控制信号。

9、本公开至少一实施例还提供一种根据本公开任一实施例所述的模拟缓存器的操作方法,该操作方法包括:通过所述输入电路根据所述输入控制信号导通或截止以开始接收或者停止接收所述输入信号;通过所述存储电路将采集到的输入信号以模拟数据的形式缓存在所述存储电路中;通过所述隔离电路根据所述隔离控制信号控制所述存储电路和所述输出电路电连接或断开;通过所述输出电路接收并缓存所述存储电路中缓存的所述模拟数据,并将所述模拟数据输出;其中,所述第一级模拟缓存单元从所述输入信号源接收第一级输入信号,除了所述第一级模拟缓存单元以外的任一当前级模拟缓存单元,接收前一级模拟缓存单元的输出作为当前级输入信号。

10、例如,本公开至少一实施例提供的操作方法,还包括:复位以清除所述存储电路中缓存的所述模拟数据和/或清除所述输出电路中的所述模拟数据。

11、本公开至少一实施例还提供一种根据本公开任一实施例所述的模拟缓存器的操作方法,该操作方法包括:通过所述级联的多个模拟缓存单元,将第一级模拟缓存单元从所述输入信号源依序接收的多个输入信号在所述级联的多个模拟缓存单元中逐级移位缓存。

12、例如,在本公开至少一实施例提供的操作方法中,其中,所述将第一级模拟缓存单元从所述输入信号源依序接收的多个输入信号在所述级联的多个模拟缓存单元中逐级移位缓存,包括:

13、对于所述多个模拟缓存单元中的任一模拟缓存单元:

14、在第一操作时间段内,所述隔离电路将所述存储电路和所述输出电路断开后,所述输入电路根据所述输入控制信号导通以开始接收所述输入信号,并且所述存储电路将采集到的所述输入信号以所述模拟数据的形式缓存在所述存储电路中;

15、在第二操作时间段内,所述输入电路根据所述输入控制信号截止以停止接收所述输入信号,所述隔离电路将所述存储电路和所述输出电路电连接后,所述输出电路接收并缓存所述存储电路中缓存的所述模拟数据;

16、在第三操作时间段内,所述隔离电路将所述存储电路和所述输出电路断开后,所述输出电路输出所述模拟数据。

17、例如,在本公开至少一实施例提供的操作方法中,其中,所述将第一级模拟缓存单元从所述输入信号源依序接收的多个输入信号在所述级联的多个模拟缓存单元中逐级移位缓存,还包括:在所述第一操作时间段之前,复位以清除所述存储电路中缓存的所述模拟数据和/或清除所述输出电路中的所述模拟数据。

18、本公开至少一实施例还提供一种信号处理装置,包括根据本公开任一实施例所述的模拟缓存器。

19、例如,本公开至少一实施例提供的信号处理装置还包括处理单元,其中,所述处理单元包括多个输入端口,所述多个输入端口分别与所述多个模拟缓存单元的所述输出电路连接。

20、例如,在本公开至少一实施例提供的信号处理装置中,其中,所述处理单元包括存算一体阵列,所述存算一体阵列包括多行和多列,所述多行对应所述多个输入端口。

技术特征:

1.一种模拟缓存器,包括级联的多个模拟缓存单元,

2.根据权利要求1所述的模拟缓存器,还包括复位电路,其中,所述复位电路配置为对所述存储电路进行复位和/或对所述输出电路进行复位。

3.根据权利要求1所述的模拟缓存器,其中,所述存储电路包括积分电路,所述积分电路配置为对所述输入信号进行积分处理,并将所述积分处理的对应于所述输入信号的处理结果以所述模拟数据缓存。

4.根据权利要求3所述的模拟缓存器,其中,所述积分电路包括电连接的第一电阻、第一电容和第一运算放大器,

5.根据权利要求1所述的模拟缓存器,其中,所述输出电路包括电连接的复制单元和缓冲器,

6.根据权利要求5所述的模拟缓存器,其中,所述复制单元包括第二电容,所述缓冲器包括第二运算放大器,

7.根据权利要求1所述的模拟缓存器,其中,所述输入电路包括第一开关,所述第一开关的第一极和第二极分别连接所述输入信号源和所述存储电路,所述第一开关的控制极接收所述输入控制信号。

8.根据权利要求1所述的模拟缓存器,其中,所述隔离电路包括第二开关,所述第二开关的第一极和第二极分别连接所述存储电路和所述输出电路,所述第二开关的控制极接收所述隔离控制信号。

9.一种根据权利要求1所述的模拟缓存器的操作方法,包括:

10.根据权利要求9所述的操作方法,还包括:

11.一种根据权利要求1所述的模拟缓存器的操作方法,包括:通过所述级联的多个模拟缓存单元,将所述第一级模拟缓存单元从所述输入信号源依序接收的多个输入信号在所述级联的多个模拟缓存单元中逐级移位缓存。

12.根据权利要求11所述的操作方法,其中,所述将所述第一级模拟缓存单元从所述输入信号源依序接收的多个输入信号在所述级联的多个模拟缓存单元中逐级移位缓存,包括:

13.根据权利要求11所述的操作方法,其中,所述将所述第一级模拟缓存单元从所述输入信号源依序接收的多个输入信号在所述级联的多个模拟缓存单元中逐级移位缓存,还包括:

14.一种信号处理装置,包括根据权利要求1所述的模拟缓存器。

15.根据权利要求14所述的信号处理装置,还包括处理单元,

16.根据权利要求15所述的信号处理装置,其中,所述处理单元包括存算一体阵列,

技术总结

一种模拟缓存器及其操作方法、信号处理装置。该模拟缓存器包括级联的多个模拟缓存单元,每个模拟缓存单元包括输入电路、存储电路、隔离电路和输出电路,输入电路根据输入控制信号导通或截止以开始接收或者停止接收输入信号;存储电路从输入电路接收输入信号,并将采集到的输入信号以模拟数据的形式缓存在存储电路中;隔离电路根据隔离控制信号控制存储电路和输出电路电连接或断开;输出电路在与存储电路电连接时接收并缓存存储电路中缓存的模拟数据,并将模拟数据输出;除了第一级模拟缓存单元之外的任一当前级模拟缓存单元的输入电路与前一级模拟缓存单元的输出电路连接。该模拟缓存器可接收和缓存多个模拟信号,实现数据的高速并行移位和输出。

技术研发人员:吴华强,赵涵,刘正午,伍冬,唐建石,高滨,钱鹤

受保护的技术使用者:清华大学

技术研发日:

技术公布日:2024/3/11

- 还没有人留言评论。精彩留言会获得点赞!