基于EEPROM的数据处理电路的制作方法

本发明涉及集成电路,尤其涉及一种基于eeprom的数据处理电路。

背景技术:

1、随着半导体技术的发展,存储器的容量、速度和成本得到了显著提升。带电可擦可编程只读存储器(electrically erasable programmable read only memory,eeprom)的出现是只读存储器(read-only memory,rom)和flash存储器技术的进一步发展和改进。与rom相比,eeprom可以被电擦写,避免了物理更改存储器的需求。与flash存储器相比,eeprom的擦写速度更快,对单个字节的编程更方便。

2、但是,eeprom通常会出现写入数据错误、数据不一致等问题,数据处理的准确性低。

技术实现思路

1、本发明提供一种基于eeprom的数据处理电路,用以解决现有技术中eeprom通常会出现写入数据错误、数据不一致等问题,数据处理的准确性低的问题。

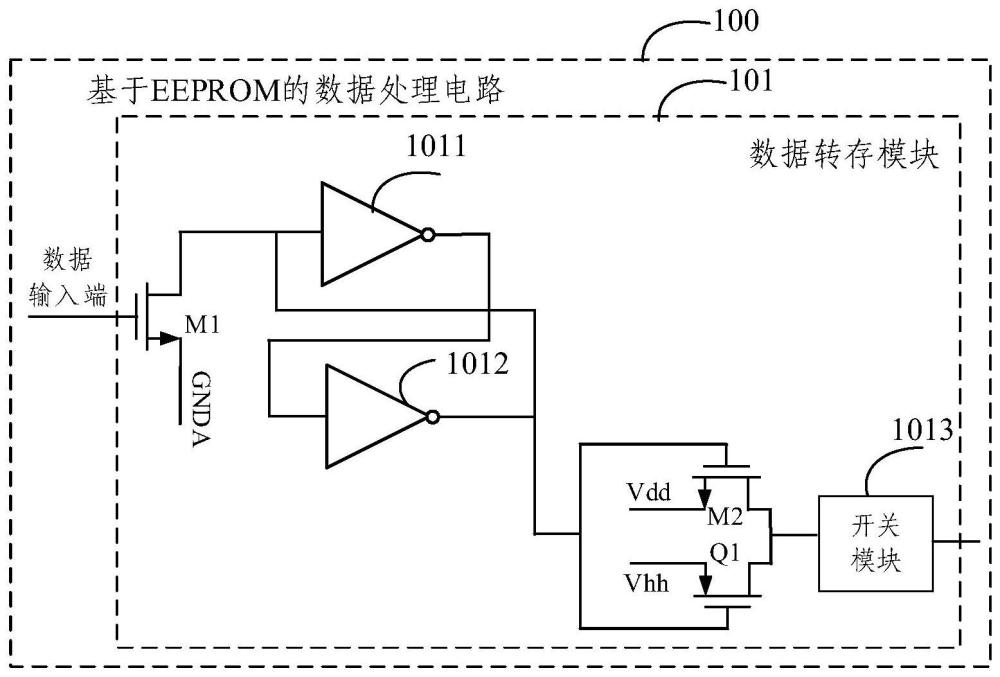

2、本发明提供一种基于eeprom的数据处理电路,包括数据转存模块;所述数据转存模块包括:第一反相器、第二反相器、第一nmos管、第二nmos管、第一pmos管和开关模块;

3、所述第一nmos管的栅极作为所述数据转存模块的数据输入端,所述第一nmos管的源极接地,所述第一nmos管的漏极连接于所述第一反相器的输入端,所述第一反相器的输出端连接于所述第二反相器的输入端,所述第二反相器的输出端分别连接于所述第一反相器的输入端、所述第二nmos管的栅极和第一pmos管的栅极,所述第二nmos管的源极接第一电平vdd,所述第一pmos管的源极接第二电平vhh,所述第一电平vdd小于所述第二电平vhh,所述第二nmos管的漏极分别连接于所述第一pmos管的漏极和所述开关模块的输入端,所述开关模块的输出端作为所述数据转存模块的输出端,所述开关模块的控制端用于接收第一控制信号,所述第一控制信号用于控制所述开关模块导通或断开。

4、根据本发明提供的一种基于eeprom的数据处理电路,所述数据转存模块还包括第三nmos管;

5、所述第三nmos管的漏极连接于所述第一反相器的输出端,所述第三nmos管的源极接地,所述第三nmos管的栅极作为所述数据转存模块的缓存数据复位端。

6、根据本发明提供的一种基于eeprom的数据处理电路,所述数据处理电路还包括控制模块;所述控制模块的输出端连接于所述数据转存模块的缓存数据复位端;

7、所述控制模块用于:在通过所述数据转存模块的输出端输出转存数据的情况下,向所述缓存数据复位端发送缓存数据复位信号,所述缓存数据复位信号用于对所述数据转存模块中缓存的数据进行复位。

8、根据本发明提供的一种基于eeprom的数据处理电路,所述开关模块包括第四nmos管和第二pmos管;

9、所述第四nmos管的源极作为所述开关模块的输入端,所述第四nmos管的源极连接于所述第二pmos管的源极,所述第四nmos管的漏极连接于所述第二pmos管的漏极,所述第四nmos管的漏极作为所述开关模块的输出端,所述第四nmos管的栅极作为所述开关模块的控制端,所述第二pmos管的栅极用于接收所述第一控制信号的反信号。

10、根据本发明提供的一种基于eeprom的数据处理电路,所述数据转存模块还包括第五nmos管;

11、所述第五nmos管的漏极连接于所述开关模块的输出端,所述第五nmos管的源极接地,所述第五nmos管的栅极作为所述数据转存模块的输出复位端。

12、根据本发明提供的一种基于eeprom的数据处理电路,所述数据转存模块包括写数据转存模块和擦数据转存模块;

13、在所述数据转存模块包括所述写数据转存模块的情况下,所述第一控制信号为写数据控制信号;

14、在所述数据转存模块包括所述擦数据转存模块的情况下,所述第一控制信号为擦数据控制信号。

15、根据本发明提供的一种基于eeprom的数据处理电路,所述数据处理电路还包括读数据模块,所述读数据模块包括:与门、第六nmos管、第七nmos管、第八nmos管、第一开关管和第二开关管;

16、所述与门的第一输入端作为所述读数据模块的读数据使能端,所述与门的第二输入端作为所述读数据模块的比特位控制端,所述与门的输出端分别连接于所述第六nmos管的栅极和所述第七nmos管的栅极,所述第七nmos管的源极作为所述读数据模块的数据输出端,所述第七nmos管的漏极连接于所述第六nmos管的源极,所述第六nmos管的漏极分别连接于所述第八nmos管的源极和所述第一开关管的第一端,所述第八nmos管的栅极和所述第八nmos管的漏极接所述第一电平vdd,所述第一开关管的第二端用于接收读数据检测电平vread,所述第一开关管的第三端连接于所述第二开关管的第一端,所述第二开关管的第三端接地,所述第二开关管的第二端作为所述读数据模块的读数据控制端。

17、根据本发明提供的一种基于eeprom的数据处理电路,所述第一开关管用于:在所述第一开关管存储有存储数据的情况下,提高所述第一开关管的导通阈值至第三电平,所述第三电平大于所述读数据检测电平vread;在所述第一开关管未存储有存储数据的情况下,降低所述第一开关管的导通阈值至第四电平,所述第四电平小于或等于所述读数据检测电平vread;在所述读数据检测电平vread大于或等于所述导通阈值的情况下,导通所述第一开关管的第一端和所述第一开关管的第三端;

18、所述第二开关管用于:在通过所述第二开关管的第二端接收到高电平的情况下,降低所述第二开关管的电阻值至小于第一阈值;在通过所述第二开关管的第二端接收到低电平的情况下,提高所述第二开关管的电阻值至第二阈值,所述第二阈值大于所述第一阈值,所述第二开关管的电阻值为所述第二开关管的第一端与所述第二开关管的第三端之间的等效电阻值。

19、根据本发明提供的一种基于eeprom的数据处理电路,所述数据处理电路还包括或非门;

20、所述或非门的第一输入端用于接收写数据控制信号,所述或非门的第二输入端用于接收擦数据控制信号,所述或非门的输出端连接于所述读数据模块的读数据控制端;

21、所述或非门用于:在接收到所述写数据控制信号或所述擦数据控制信号的情况下,输出低电平;在未接收到所述写数据控制信号和所述擦数据控制信号的情况下,输出高电平。

22、根据本发明提供的一种基于eeprom的数据处理电路,所述数据处理电路还包括读模式输出缓存模块,所述读模式输出缓存模块的输入端连接于所述读数据模块的数据输出端,所述读模式输出缓存模块包括:第三pmos管、第四pmos管、第五pmos管、第六pmos管、第七pmos管、第九nmos管、第十nmos管、第十一nmos管、第十二nmos管和第三反相器;

23、所述第三pmos管的漏极分别连接于所述第五pmos管的栅极和所述第九nmos管的栅极,所述第三pmos管的漏极作为所述读模式输出缓存模块的输入端,所述第三pmos管的栅极接地,所述第三pmos管的源极连接于所述第四pmos管的漏极,所述第四pmos管的源极和所述第五pmos管的源极接所述第一电平vdd,所述第五pmos管的漏极连接于所述第九nmos管的漏极,所述第九nmos管的源极连接于所述第十nmos管的漏极,所述第十nmos管的源极接地,所述第十nmos管的栅极用于接收第二控制信号,所述第四pmos管的栅极用于接收所述第二控制信号的反信号,所述第九nmos管的漏极还连接于所述第三反相器的输入端,所述第三反相器的输出端连接于所述第六pmos管的源极,所述第六pmos管的漏极连接于所述第七pmos管的源极,所述第七pmos管的漏极分别连接于所述第三反相器的输入端和所述第十一nmos管的漏极,所述第十一nmos管的源极连接于所述第十二nmos管的漏极,所述第十二nmos管的源极接地,所述第六pmos管的栅极用于接收第三控制信号,所述第十二nmos管的栅极用于接收所述第三控制信号的反信号,所述第七pmos管的栅极分别连接于所述第十一nmos管的栅极和所述第三反相器的输出端,所述第三反相器的输出端作为所述读模式输出缓存模块的输出端。

24、本发明提供的基于eeprom的数据处理电路,利用头尾相接的第一反相器和第二反相器,可以对输入数据起锁存作用,在对数据进行锁存之后可以控制第二nmos管或第一pmos管择一导通,进而将锁存的数据从数据转存模块的输出端输出,需要说明的是,第二nmos管或第一pmos管与数据转存模块的输出端之间还设置有开关模块,通过第一控制信号控制其导通或断开,进而控制是否将转存的数据输出。相较于相关技术中eeprom出现写入数据错误、数据不一致等问题,本发明实施例利用头尾相接的第一反相器和第二反相器,可以对输入数据起锁存作用,有效减少了输入数据中的小尖刺等,即排除了输入干扰的噪声影响,保证存储数据不失真,可以有效提高输入数据处理的准确性;另外,通过第一控制信号的时序控制是否将转存的数据输出,可以有效提高转存地址的准确性。

- 还没有人留言评论。精彩留言会获得点赞!