包含具有减小的栅极诱发漏极泄漏的存储器子字驱动器电路的设备及用于所述电路的方法与流程

1.本技术大体上涉及存储器装置,且更具体地说,涉及包含具有减小的栅极诱发漏极泄漏的存储器子字驱动器电路的设备及用于所述存储器子字驱动器电路的方法。

背景技术:

2.例如动态随机存取存储器(dram)的半导体存储器装置包含存储器单元阵列,所述存储器单元阵列具有安置在子字线与位线之间的相交点处的存储器单元。半导体存储器装置可包含阶层结构化的字线(wl)和子字线。字线由相应字驱动器驱动并定位在上部阶层处,且由行地址的第一部分选择。子字线由相应子字驱动器驱动并定位在下部阶层处,且基于对应字线和由行地址的第二部分选择的fx驱动器线(fx)来选择。

3.由于在半导体制造中阵列存取装置按比例缩小,与半导体衬底上制造的亚微米级装置相关的泄漏电流(例如,栅极诱发漏极泄漏(gidl))越来越受到关注。最近,由于存储器测试器的有限电流容量,需要减少半导体存储器装置中的gidl电流,尤其在压力测试时间期间。例如,减小半导体存储器装置的子字驱动器中的gidl在减小存储器测试器的最大电流容量方面已成为期望的,从而减小存储器测试器和存储器测试的成本。

技术实现要素:

4.本公开的一方面提供一种设备,其包括:第一子字线;以及第二子字线,其通过第一共同晶体管耦合到所述第一子字线;其中,响应于测试模式信号,将所述第一和第二子字线中的每一者的电压从第三电压升高到第一电压,且将所述第一共同晶体管的栅极电压升高到所述第一与第三电压之间的第二电压。

5.本公开的另一方面提供一种方法,其包括:响应于测试信号而进入测试模式;将第一和第二子字线中的每一者的电压从第三电压升高到第一电压;以及将耦合在所述第一与第二子字线之间的第一共同晶体管的栅极的电压升高到所述第一与第三电压之间的第二电压。

6.本公开的另一方面提供一种半导体存储器装置,其包括:测试模式开关,其被配置成使所述半导体存储器装置响应于测试模式信号而激活压力测试;以及共同晶体管,其被配置成在所述共同晶体管的栅极的第一电压高于所述共同晶体管的阈值电压时共享第一子字线和第二子字线的电压;其中在所述压力测试期间,所述第一电压高于接地电平电压,并且所述第一和第二子字线的第二电压高于所述阈值电压。

7.本公开的另一方面提供一种设备,其包括:第一子字线,其耦合到第一n型晶体管的漏极和第一p型晶体管的漏极;第二子字线,其耦合到第二n型晶体管的漏极和第二p型晶体管的漏极;第一共同晶体管,其被配置成将所述第一子字线提供到断开状态字线电压;以及第二共同晶体管,其被配置成将所述第二子字线提供到所述断开状态字线电压,其中所述第一和第二子字线安置在存储器片块的边缘区域中,其中,在激活和预充电阶段中,将所

述第一和第二n型晶体管以及所述第一和第二p型晶体管中的每一者的栅极电压降低到接地电平电压,将所述第一和第二p型晶体管的所述源极的电压升高到第二电压,并且将所述第一和第二共同晶体管的栅极电压从第一电压降低到所述接地电平电压。

附图说明

8.图1是根据本公开中的实施例的设备的框图。

9.图2是根据本公开中的实施例的半导体存储器装置的存储器组的配置的图。

10.图3是根据本公开中的实施例的存储器组的一部分的示意图。

11.图4是根据本公开中的实施例的存储器配置的框图。

12.图5是根据本公开中的实施例的fx驱动器块的示意图。

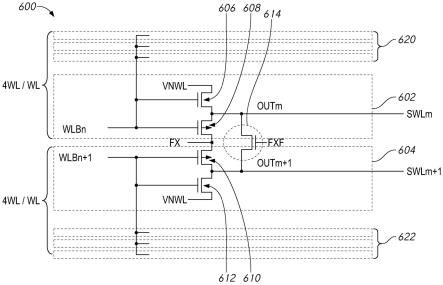

13.图6a是根据本公开中的实施例的子字驱动器的示意图。

14.图6b是根据本公开中的实施例的子字驱动器的示意图。

15.图7a是根据本公开中的实施例的子字驱动器的存储器存取操作中的各种信号的定时图。

16.图7b是根据本公开中的实施例的在压力测试期间存储器片块中的各种信号的定时图。

具体实施方式

17.下文阐述某些细节以提供对本公开的各种实施例的实例的充分理解。然而,应了解,本文中所描述的实例可在没有这些特定细节的情况下实践。此外,本文中所描述的本公开的特定实例不应解释为将本公开的范围限于这些特定实例。在其它情况下,尚未详细展示众所周知的电路、控制信号、定时协议和软件操作,以便避免不必要地混淆本公开的实施例。另外,例如“耦合(couples和coupled)”的术语意指两个组件可直接或间接电耦合。间接耦合可暗指两个组件通过一或多个中间组件耦合。由图式展示的各种半导体结构的形状和尺寸未按比例绘制。例如,示意图仅作为实例提供,并且可以针对实际半导体存储器装置修改尺寸。

18.图1是根据本公开的实施例的设备100的框图。半导体存储器装置10可以是设备100的实例。在本公开的一些实施例中,半导体存储器装置10可以是动态随机存取存储器(dram)。半导体存储器装置10包含存储器单元阵列11。存储器单元阵列11包含彼此相交的多个子字线swl和多个数据线dl,其中存储器单元(mc)安置在相交点处。swl可由相应子字驱动器swd 42驱动。为了清楚起见,图1中展示了仅一个swl、swd、dl和mc。多个字线wl和fx驱动器线fx可提供到存储器单元阵列11中的相应swd。例如,字线wl和fx驱动器线fx的选择由行解码器电路12实行,并且数据线dl的选择由列解码器电路13实行。在一些实例中,fx驱动器线fx可由相应fx驱动器电路fxd 46驱动。字线wl可由相应字驱动器wd 44驱动。例如,半导体存储器装置可具有128个字线和提供相应字线的128个字驱动器。

19.在一些实例中,半导体存储器装置10可包含以多个存储器组布置的多个存储器单元阵列11。半导体存储器装置10还可包含各自耦合到相应存储器单元阵列11的多个行解码器电路12和多个列解码器电路。

20.提供到命令和地址端子21的命令地址(ca)信号中包含的命令经由命令/地址输入

电路31输入到命令解码器电路34。命令解码器电路34对命令进行解码以提供各种内部命令信号。例如,内部命令可包含用于选择字线的行命令信号、用于选择数据线的列命令信号(例如,读取命令或写入命令),以及用于允许半导体存储器装置进入测试模式的测试模式信号。

21.当发出激活命令且行地址及时地供应有激活命令时,且列地址及时地供应有读取命令时,从存储器单元阵列11中的由这些行地址和列地址指定的存储器单元mc读取读取数据。更具体地,行解码器电路12选择由行地址ra指示的字线wl、fx驱动器线fx和子字线swl,使得相关联存储器单元mc随后连接到数据线dl。此外,当存储器单元mc被行地址选择且相关联行由激活命令激活时,字线wl可以是活动的且fx驱动器线fx可以是活动的。这使得子字线swl为活动的。相反地,当存储器单元mc未被选择时,例如,在预充电操作中,fx驱动器线fx可以是非活动的,且字线wl也可以是非活动的。这将子字线swl驱动到非活动电势,例如,断开状态字线电压vnwl。进一步参考图1,读取数据dq经由读取/写入放大器15和输入/输出电路17从数据端子24输出到外部。

22.类似地,当发出激活命令且行地址及时地供应有激活命令,且列地址及时地供应有写入命令时,输入/输出电路17可在数据端子24处接收写入数据dq。写入数据dq经由输入/输出电路17和读取/写入放大器15供应到存储器单元阵列11且写入由行地址和列地址指定的存储器单元mc中。

23.在一些实例中,当激活测试模式时,可执行压力测试,例如,全行高(arh)压力测试。在arh压力测试期间,半导体存储器装置中的晶体管的断开状态电流可增加到相当大电平。例如,在arh压力测试中,将半导体中的所有子字线升高到高电压电平(vccp,例如,3.1v)。因此,由耦合子字线的晶体管导致的栅极诱发漏极泄漏(gidl)电流可能极大地促增在arh压力测试期间需要由存储器测试器供应的总电流。这可能暗中损害存储器测试器的最大电流供应容量。由于由高性能cmos(hpc)工艺制造的晶体管的ioff电流增加,确切地说,在高温下增加,因此在半导体存储器装置中gidl电流变得更明显。

24.电源端子25供应有电源电压vdd1、vdd2和vss。这些电源电压vdd1、vdd2和vss供应到内部电压发生器电路39。内部电压发生器电路39提供各种内部电压,例如vpp、vary、vperi、veq、vdrv、vccp和vnwl。

25.内部电势vccp vnwl为主要在行解码器电路12、字驱动器wd 44和fx驱动器fxd 46中使用的电势。例如,当基于地址信号add选择时,fx驱动器fxd可被配置成将fx驱动器线fx上的电势驱动到对应于高电势(例如3.1v)的vccp电平。当行处于预充电状态时,响应于字线(wl)上的非活动信号和fx驱动器线(例如,fx、fxf)上的非活动控制信号,相关联子字驱动器可被配置成将子字线(swl)下拉到内部电压vnwl(例如,非活动电势,其可以是负电压)。

26.内部电势vary和veq为将由感测放大器18、传送门19和/或读取/写入放大器15使用的电势。当激活感测放大器18时,通过将成对数据线中的一者驱动到vary电平且另一者驱动到vss电平来放大所读出的读取数据。对于大多数外围电路,例如命令/地址输入电路31,内部电势vperi、vdrv用作电源电势。通过使用具有比外部电势vdd(如这些外围电路的电源电势)低的电势的内部电势vperi,可有可能减少半导体存储器装置10的电力消耗。

27.电源端子26供应有电源电压vddq和vssq。这些电源电压vddq和vssq供应到输入/

输出电路17。电源电压vddq和vssq可分别为与供应到电源端子25的电源电压vdd2和vss相同的电压。然而,专用电源电压vddq和vssq可用于输入/输出电路17,使得由输入/输出电路17生成的电源噪声不会传播到装置10的其它电路块。

28.图2是根据本公开中所描述的一些实例的半导体存储器装置的存储器组的实例配置的图。例如,在本公开的一些实施例中,装置10(图1)的存储器单元阵列11中的每一者可包含图2的组200的配置。

29.在一些实例中,存储器组200可包含多个存储器片块区,例如mat0-3。在图2中展示的实例中,组200具有四个存储器片块区,但在其它实例中,组200可包含更多或更少的存储器片块区。如由存储器片块区mat1中的虚线所指示,每个存储器片块区可划分成多个子区,例如submat1-0-3。虽然图2中展示的实例包含四个子区,但在其它实例中,存储器片块区mat0-3可包含更多或更少的子区。每个子区submat1-0-3可包含在y方向上对准的多个存储器片块(例如,64个)。为了清楚起见,图2中未展示个别存储器片块。子字驱动器swd块(图2中未展示)可安置在每个存储器片块的两侧上,例如,在x方向上。感测放大器sa块可安置在每个存储器片块的两侧上,例如,在y方向上。在一些实施例中,可将每个子区submat1-0-3的存储器片块提供到对应io(例如,dq衬垫)。

30.子字驱动器操作可由行解码器电路(例如,图1的行解码器电路12)控制。当接收到行地址ra时,行解码器通过激活由行地址ra指示的适当字驱动器(wd)和适当fx驱动器(fxd)来选择子字线swl。在图2中展示的实例中,针对字驱动器wd展示一个块,然而,字驱动器wd块可包含多个字驱动器wd。类似地,针对fx驱动器fxd展示两个块,但每个fx驱动器fxd块可包含多个fx驱动器fxd。例如,如果每个存储器片块区mat包含四个子区且每个子区包含64个存储器片块,则字驱动器wd块可包含128个wd,其各自被配置成激活对应字线(wl)。继续此实例,每个fx驱动器fxd块可包含八个fx驱动器fxd,其各自被配置成激活对应fx驱动器线(fx)。

31.图3是根据本公开中的实施例的存储器组300的一部分的示意图。在本公开的一些实施例中,图3中展示的组300的一部分可包含于图2的组200和/或图1的存储器单元阵列11中。

32.存储器部分300可包含多个子字线310,其各自由相应子字驱动器swdj 316驱动。例如,子字线314可由对应子字驱动器swd5驱动,所述对应子字驱动器与由字线wd1驱动的字线相关联且还与fx驱动器线302(例如,fx5)相关联,所述fx驱动器线与fx驱动器308相关联。换句话说,对于每个fx驱动器,提供对应字线wl和fx驱动器线fx以及非活动电势(例如,断开状态字线电压vnwl)。字线wl上的信号和fx驱动器线fx上的控制信号可分别由字驱动器wd0-n和fx驱动器fxd块304基于行地址提供。

33.字线wl可在相应存储器片块的阵列区上方延伸,以将字信号提供到存储器片块的子字驱动器行swd0-7,以激活那些子字驱动器swd0-7。也就是说,当激活字驱动器wd时,其可将活动字信号提供到片块的所有子字驱动器swd0-7。如下文将描述,fx驱动器线可包含fx和fxf。在一些实例中,当fx驱动器线fx为活动的时,fx驱动器线fxf为非活动的。相反地,fx驱动器线fxf可为活动的,而fx驱动器线fx为非活动的。fx驱动器fxd块304的每个fx驱动器线302将fx驱动器线fx和fxf提供到每个片块中的至少一个子字驱动器swd。在图3中展示的实例中,fx驱动器fxd块304包含偶数fx驱动器fxd 306和奇数fx驱动器fxd 308。偶数fx

驱动器fxd 306将相应fx驱动器线fx和fxf提供到每个存储器片块的偶数编号的子字驱动器swd0、swd2、swd4和swd6,并且奇数fx驱动器fxd 308将相应fx驱动器线fx和fxf提供到每个存储器片块的奇数编号的子字驱动器swd1、swd3、swd5和swd7。然而,在其它实例中可使用其它布置。在图3中展示的实例中,fx驱动器fxd块304的每个fx驱动器线可耦合到每个存储器片块中的对应子字驱动器swd0-7。例如,fx驱动器线5可耦合到每个存储器片块的子字驱动器swd5。

34.在图3中展示的实例操作中,行地址ra已指示应激活wd1,且应激活与fx驱动器线fx 5相关联的奇数fx驱动器fxd 308。如阴影区312所展示,与非活动字驱动器wd0、wdn相关联的子字线310保持非活动,即使与fx驱动器线fx 5相关联的子字线为活动的也是如此。然而,在与已激活wd1相关联的子字线322之中,激活由与已激活wd1和fx 5相关联的子字驱动器swd5驱动的子字线314。借助于实例,已激活wd可被配置成在相关联字线上提供活动信号,并且已激活fx驱动器fxd可被配置成在fx驱动器线(例如,fx、fxf)上提供活动控制信号。类似地,已激活子字驱动器可被配置成在相关联子字线上提供活动信号。因此,与wd1相关联的选定存储器片块的选定字线wl由对应已激活子字驱动器swd5驱动到活动电势。

35.在一些实例中,选定存储器片块的其它子字驱动器swd将相应未选定子字线swl驱动到非活动电势(例如,vnwl)以保持非活动。未选定存储器片块mat(例如,与wd0和wdn相关联的存储器片块)的子字驱动器swd保持撤销激活,并且未选定存储器片块mat的子字线swl未被提供电压,或替代地,在一些实例中,提供有非活动电势(例如,vnwl)。鉴于子字驱动器swd耦合到fx驱动器fxd和字驱动器wd,为了激活与子字驱动器swd相关联的子字线swl,必须激活相关联fx驱动器fxd和字驱动器wd两者。

36.图4是根据本公开中的实施例的半导体存储器装置中的存储器配置400的框图。存储器配置400可实施于半导体存储器装置10(图1)中。在本公开的一些实施例中,存储器配置400可实施于存储器组200(图2)中。例如,存储器配置400可用于子区中的每一者中包含的存储器片块。存储器配置400可包含多个存储器单元阵列,例如,406。存储器单元阵列406可按行和列布置。每个存储器单元阵列406可包含多个存储器单元。存储器配置400还包含多个子字驱动器(swd)块410和多个感测放大器(sa)块408。存储器单元阵列406、swd块410和sa块408可实施于存储器单元阵列11(图1)内部。在本公开的一些实施例中,每个存储器单元阵列406表示相应存储器片块。

37.swd块410可布置于存储器单元阵列406的侧面上。在非限制性实例中,子字驱动器可放置在存储器单元阵列的一侧上且邻近于存储器单元阵列,以在用于存储器单元阵列的相应子字线上提供信号。在另一非限制性实例中,子字驱动器可放置在存储器单元阵列的两侧上且邻近于存储器单元阵列,以在用于存储器单元阵列的相应子字线上提供信号。例如,用于存储器单元阵列的子字线可划分成偶数编号的和奇数编号的子字线。用于偶数编号的子字线的子字驱动器可布置成邻近于存储器单元阵列的第一侧(例如,左侧),而用于偶数编号的子字线的子字驱动器可布置成邻近于存储器单元阵列的与第一侧相对的第二侧(例如,右侧)。

38.在图4中的实例中,swd块中的每一者可与swd块的任一侧上的邻近存储器单元阵列相关联。swd块中的每一者可与swd块的两侧上的邻近存储器单元阵列相关联。例如,swd块可具有第一部分和第二部分,其中第一部分耦合到邻近于swd块的第一侧(例如,左侧)的

存储器单元阵列的子字线,并且第二部分耦合到邻近于与swd块的第一侧相对的第二侧(例如,右侧)的存储器单元阵列的子字线。

39.图5是根据本公开的实施例的fx驱动器块500的示意图。fx驱动器块500可以是图3的fxd驱动器块304的实例。fx驱动器块500包含解码器逻辑,以及八个fx驱动器fxd 512、514、516、518、522、524、526和528。解码器逻辑被配置成激活对应fxd驱动器。在如图5中所示的非限制性实例中,两个tm开关tmsw 510和520耦合到fx驱动器块500。tm开关中的一者tmsw 510被配置成接收测试模式信号且耦合到fx驱动器块500中的fx驱动器中的四者fxd 512、514、516和518。另一tm开关tmsw 520被配置成接收测试模式信号且耦合到fx驱动器块500中的fx驱动器中的其它四者fxd 522、524、526和528。

40.如上文相对于图3所论述,每个fx驱动器fxd被配置成驱动对应fx驱动器线fx和fxf。在图5中,fx驱动器fxd 512驱动fx驱动器线fx 531和fxf 532。在图3中,子字驱动器swd0耦合到fx驱动器fxd 306和字驱动器wd 0,如先前所描述。为了激活与子字驱动器swd相关联的子字线swl,必须激活相关联fx驱动器fxd和字驱动器wd两者。除如上文所描述在存储器存取操作中激活fx驱动器线fx和fxf之外,fx驱动器fxd还在测试模式期间激活对应fx驱动器线fx和fxf。在测试模式中,tm开关tmsw 510和520耦合到fx驱动器fxd 512、514、516、518、522、524、526和528,并且fx驱动器fxd 512、514、516、518、522、524、526和528继而将fx驱动器线fxf 532、534、536、538、542、544、546和548驱动到vdrv(例如,2.0v),且将fx驱动器线fx 531、533、535、537、541、543、545和547驱动到vccp(例如,3.1v)。

41.图6a是根据本公开的实施例的子字驱动器600的示意图。在本公开的一些实施例中,子字驱动器600可包含于图1的子字驱动器swd 42、图3的子字驱动器swd 316和/或图4的子字驱动器块410中。

42.子字驱动器600包含多个子字驱动器620、通过共同晶体管614耦合到子字驱动器604的子字驱动器602,以及多个子字驱动器622。子字驱动器602包含串联耦合的晶体管606和608。晶体管606和608的栅极和漏极分别耦合到字线wlbn和子字线swlm。晶体管606的源极耦合到提供断开状态字线电压vnwl的电压源,并且晶体管608的源极耦合到fx驱动器线fx。类似地,子字驱动器604包含串联耦合的晶体管610和612。晶体管610和612的栅极和漏极分别耦合到字线wlbn+1和子字线swlm+1。晶体管610的源极耦合到fx驱动器线fx,并且晶体管612的源极耦合到提供断开状态字线电压vnwl的电压源。子字线中的每一者耦合到存储器阵列中的其相应存储器单元。

43.图6a展示两个子字驱动器602和604,此外,多个子字驱动器620和622中的每一者可以与子字驱动器602或604类似的方式配置。例如,多个子字驱动器620中的每一者还可耦合到字线wlbn,子字驱动器602耦合到所述字线wlbn。类似地,多个子字驱动器622中的每一者还可耦合到字线wlbn+1,子字驱动器604耦合到所述字线wlbn+1。在图6a中展示的实例中,一个字线wl驱动四个子字驱动器以在四个子字线上提供信号(仅展示四个子字线中的一者)。除子字线swlm和swlm+1之外,来自多个子字驱动器620的四个子字线中的一者可通过类似于共同晶体管614的共同晶体管耦合到来自多个子字驱动器622的四个子字线中的一者。在本公开的一些实施例中,来自邻近多个子字驱动器的四个子字线中的一者可通过类似于共同晶体管614的共同晶体管耦合到来自另外多个子字驱动器的四个子字线中的一者。然而,通过共同晶体管耦合两个子字线的其它配置有可能符合存储器单元阵列的布局

要求。此外,通过共同晶体管耦合两个子字线可节省布局面积,且可通过通过fx驱动器线fxf控制共同晶体管的栅极电压来减小共同晶体管的gidl,如下文详细论述。

44.如图4的非限制性实例中所示的子字驱动器块swd 410中的每一者可包含以与图6a中展示的配置类似的方式通过共同晶体管耦合的一对子字线。在图6a中,子字驱动器602、620与字线wlbn相关联。子字驱动器604、622与不同字线wlbn+1相关联。在如图6a中所示的实例中,分别来自两个子字驱动器602、604的两个子字线通过共同晶体管614耦合。以类似方式,来自子字驱动器620的多个子字线中的每一者可通过共同晶体管耦合到来自子字驱动器622的多个子字线中的相应一者。因此,两个子字驱动器可形成一对,其中两个子字驱动器的输出耦合到通过共同晶体管彼此耦合的相应子字线。

45.在图6a中,子字线swlm通过共同晶体管614耦合到子字线swlm+1。在一些实例中,共同晶体管614可以是n沟道型晶体管。由于共同晶体管由两个子字线共享,因此在半导体存储器装置中,共同晶体管的数目可与子字线的数目的一半一样多。

46.在半导体存储器装置的存储器存取操作中,可选择子字线swlm以通过将其电平升高到vccp而从连接到子字线swlm的多个存储器单元存取特定存储器单元。还在感测和放大阶段中选择与存储器单元相关联的相应位线以存取存储器单元。

47.在存储器存取操作的感测和放大阶段中,耦合到共同晶体管614的栅极的fx驱动器线fxf降低到接地电平(例如,0v),使得子字线swlm可保持在vccp电平。当感测和放大阶段完成时,共同晶体管614的栅极处的fxf升高到较高电平,例如升高到vccp,以允许子字线swlm将其电压电平降低到vnwl(例如,断开状态字线电平),所述vnwl可低于接地电平。例如,子字线swlm可通过已激活共同晶体管614放电到处于vnwl的子字线swlm+1。

48.当例如由半导体测试器在半导体存储器装置中激活测试模式时,可执行压力测试,例如全行高(arh)压力测试。在此类压力测试期间,作为压力的方式,将存储器阵列中的所有子字线升高到vccp电平。在压力测试期间,连接到子字线的晶体管,例如,图6a中的共同晶体管614,可能经受栅极诱发漏极泄漏(gidl)电流。例如,这可能在耦合到fx驱动器fxf的共同晶体管614的栅极降低到接地电平(0v)且耦合到子字线的源极和漏极升高到vccp电平时发生。在此情形下,共同晶体管614的栅极与漏极之间的电压可达到vccp电平。当考虑到存在与共同晶体管614一样多的具有类似的配置的晶体管时,此电压可足以使共同晶体管614的gidl为相当大的,在半导体存储器装置中,所述共同晶体管的数目可与子字线的数目的一半一样多。所有晶体管的gidl可增加到使得压力测试期间的总装置电流可超过半导体测试器的最大电流容量的此电平。这可能暗中损害半导体测试器的操作。此外,最近,由于由高性能cmos(hpc)工艺制造的晶体管的ioff电流增加,确切地说,在高温下增加,因此在半导体存储器装置中gidl变得更明显。

49.为了减少归因于半导体存储器装置的存储器阵列中的所有共同晶体管的此gidl,通过将fx驱动器线fxf升高到vdrv,在压力测试期间,共同晶体管的栅极可例如从接地电平升高到vdrv。在半导体存储器装置的存储器存取操作的感测和放大阶段期间,耦合到共同晶体管的栅极的fx驱动器线fxf处于接地电平(例如,0v)。这是为了保持耦合两个子字线的共同晶体管不导电。如果选择两个子字线中的一者来存取存储器单元,则选定子字线处于vccp电平且另一子字线处于vnwl电平。在存储器存取操作中,仅选择有限数目的子字线用于存取存储器单元。此外,在非感测和放大阶段期间,未选定子字线处于vnwl电平。因此,共

同晶体管的gidl可能不是问题。

50.在图6a的非限制性实例中,然而,在压力测试期间,所有子字线swl升高到vccp,且所有fx驱动器线fx升高到vccp。耦合子字线swlm和swlm+1以及共同晶体管的栅极的共同晶体管614耦合到fx驱动器线fxf。因此,在所有子字线swl处于vccp电平的情形下,即使fx驱动器线fxf升高例如到vdrv电平,共同晶体管614和子字线swl也不会造成不利影响,因为不存在其它电流路径。由于可通过将耦合到fx驱动器线fxf的栅极的电压升高到例如vdrv电平来减小共同晶体管614的栅极与漏极之间的电压,因此可减小gidl。fx驱动器线fxf电平不需要限于vdrv电平。例如,在本公开的一些实施例中,fx驱动器线fxf电平可与共同晶体管614的栅极可承受的电平一样高,以便减小gidl。如上文所论述,在半导体存储器装置内,具有类似配置的共同晶体管的子字线的数目的差不多一半与共同晶体管614的数目一样多。因此,减小共同晶体管中的每一者的gidl可有效地减小在测试模式中的压力测试期间半导体存储器装置的总装置电流。响应于测试模式信号,fx驱动器fxd将fx驱动器线fxf升高到高于接地电平,例如升高到vdrv,所述vdrv可用于减小共同晶体管的gidl。

51.如上文所描述,在存储器存取操作中,耦合两个子字驱动器502、504的输出的共同晶体管514可允许电流双向流动,这取决于激活哪个子字驱动器。如果激活子字驱动器602(例如,响应于活动字线)且撤销激活子字驱动器604,则共同晶体管614中的电流可从已激活子字驱动器602流动到已撤销激活子字驱动器604,以在预充电期间使已激活字线wlm(耦合到子字驱动器602的输出outm)的字线电势被下拉到非活动电势vnwl(例如,断开状态字线电压)。相反,如果激活子字驱动器604且撤销激活子字驱动器602,则共同晶体管中的电流可从已激活子字驱动器604流动到已撤销激活子字驱动器602,以在预充电期间使已激活字线wlm+1(耦合到子字驱动器604的输出outm+1)的字线电势被下拉到非活动电势vnwl。

52.相比而言,在测试模式期间,耦合两个子字线swlm和swlm+1的共同晶体管614可允许电流双向流动,这取决于哪个子字线具有较高电压。子字线swlm和swlm+1两者都处于高电压电平(例如,响应于测试模式信号)。共同晶体管614中的电流可在压力测试期间从子字线中的一者(如果其碰巧具有较高电压)流到子字线中的另一者以使子字线的电压相等(例如,处于vccp),以使得将有效压力施加到半导体存储器装置的存储器片块。

53.图6b是根据本公开的实施例的子字驱动器650的示意图。子字驱动器650可以是图6a中的子字驱动器600中的一者的实例。子字驱动器650包含串联耦合的晶体管660和662。晶体管660和662的栅极耦合到字线wlb。晶体管662的源极耦合到vnwl,并且晶体管660的源极耦合到fx驱动器线fx。晶体管660和662的漏极耦合到子字线swlm,所述子字线swlm又耦合到其在存储器阵列中的相应存储器单元。子字线swlm还通过共同晶体管664耦合到子字线swlm+1。共同晶体管664的栅极耦合到fx驱动器线fxf。

54.在半导体存储器装置的存储器存取操作中,当选择耦合到子字线swlm的存储器单元来读取时,共同晶体管664的栅极的电压处于接地电平。因为栅极的电压处于接地电平,所以共同晶体管664并不导电,子字线swlm可在其被选择时将其电压维持在vccp。当不再选择存储器单元时,共同晶体管664的栅极电压可由fxd驱动器线fxf升高到例如vdrv。因为共同晶体管664现在接通,所以子字线swlm的电压将通过共同晶体管664和子字线swlm+1降低到vnwl,所述子字线swlm+1以与图6a的子字驱动器604类似的方式通过n型晶体管耦合到vnwl。

55.相比而言,在压力测试期间,共同晶体管664的栅极可处于高于接地电平但低于vccp的电压,例如,处于vdrv(例如,2.0v)。因此,耦合两个子字线swlm和swlm+1的共同晶体管664可接通,且允许电流双向流动,这取决于哪个子字线具有较高电压。在压力测试期间,子字线swlm和swlm+1两者都处于高电压电平(例如,响应于测试模式信号),例如,处于vccp。共同晶体管664中的电流可在压力测试期间从子字线中的一者(如果其碰巧具有较高电压)流到子字线中的另一者以使子字线的电压相等,例如,处于vccp。以此方式,子字线swlm和swlm+1与共同晶体管664的栅极之间的电压减小到例如vccp-vdrv,而非处于vccp-接地。因此,在压力测试期间,有效压力仍通过使所有子字线处于vccp而施加到半导体存储器装置的存储器片块,同时因为共同晶体管664的栅极与漏极之间的电压减小而减小gidl。

56.返回参考图6a,当半导体存储器装置处于活动存储器存取操作时,选定子字线(例如,图6a中的swlm)可处于具有高电势电压vccp的活动高状态以存取存储器单元。在存取存储器单元之后,具有vccp的选定子字线swlm可通过将一对子字线swlm和swlm+1耦合到vnwl电压电平的共同晶体管614而放电。耦合到子字线swlm+1的共同晶体管进一步通过晶体管612耦合到vnwl,如图6a中所示。类似地,子字线swlm+1可被选择为处于具有vccp电压的活动高状态。在存取存储器单元之后,具有vccp的选定子字线swlm+1可通过将所述一对子字线swlm和swlm+1耦合到vnwl电压电平的共同晶体管614而放电。耦合到子字线swlm的共同晶体管进一步通过晶体管606耦合到vnwl。

57.图7a是根据本公开的实施例的子字驱动器的存储器存取操作中的各种信号的定时图700。在图7a的非限制性实例中,定时图700展示存储器存取操作(例如,激活)期间子字驱动器的操作。图6a的子字驱动器602、604可根据定时图700的实例操作来操作。然而,图7a的实例不限于图6a中的子字驱动器的特定配置。

58.定时图700展示字线wlb、fx驱动器线fx0、fxf0以及子字线swl0的状态。字线wlb上的状态可为活动低的,且字线wlb可由相应字驱动器(例如,图1-3中的wd)驱动。fx驱动器线fx和fxf可由fx驱动器fxd驱动,例如图1-3中所示的fx驱动器。在一些实例中,作为说明,将参考图6a的子字驱动器602描述定时图700。例如,定时图700中的wlb可对应于图6a中的字线wlbn;fx0、fxf0可分别对应于图6a中的fx、fxf。swl0可对应于子字线swlm且由图6a中的子字驱动器602提供。fx1、fxf1和swl1可对应于与wlbn相关联的另一子字驱动器(例如,额外子字驱动器620中的一者)的驱动器线/字线。

59.在t0之前的一些时间,可由行解码器电路(例如,图1中的12)接收激活信号act。可通过act信号将地址信号提供到半导体存储器装置以选择字驱动器和子字驱动器来进行激活。例如,字线wlb可过渡到活动状态(例如,在图7a中展示的实例中为0vvss),fx驱动器线fx0上的状态可变为活动高,且fx驱动器线fxf0可变为活动低。在时间t0时或附近,参考图6a,选定子字线swlm可响应于wlbn、fx0和fxf0的激活而被驱动到活动状态(例如,高电势vccp)。例如,子字驱动器602中的晶体管608可为活动的,且子字驱动器602中的晶体管606和614可为非活动的,以驱动选定子字线swlm(在图7a中展示为swl0)。子字线swlm可经由晶体管608耦合到fx驱动器线fx0的vccp。在此类时间期间,可存取子字线swl0所选择的存储器单元(未展示)。

60.在时间t1时或附近,可由半导体存储器装置接收预充电命令。作为响应,内部预充电信号pre(图7a中未展示)可过渡到活动状态。至少部分地响应预充电信号pre,可撤销激

活与fx0相关联的fx驱动器,且可将fx驱动器线fx0从vccp解耦。当fx0线上的电势减小时,字线wlb的状态仍较低。子字线swl由p沟道型晶体管608下拉到较低电压,因此swl线上的电势减小。

61.在时间t2时或附近,fx驱动器线fxf0可为非活动的且变为高。这使n沟道型晶体管614在时间t3时或附近接通并更快地将子字线swl上的电势朝向非活动电势vnwl下拉。这是可能的,因为共同晶体管614耦合到与不同字线wlbn+1相关联的子字驱动器604。此时,耦合到子字驱动器602的字线wlbn仍为活动的(例如,处于逻辑低),而其它字线(例如,wlbn+1)未被选择(例如,处于逻辑高)。因此,子字驱动器604中的n沟道型晶体管612接通以将非活动电势vnwl耦合到共同晶体管614的漏极/源极。

62.在时间t4时或附近,字线wlb变为非活动的,且wlb上的电势增加。这使p沟道型晶体管608断开且n沟道型晶体管606接通,这进一步有助于将子字驱动器602的输出outm处的电势下拉到非活动电势vnwl。

63.应注意,子字线swl0在时间t1之后变为撤销激活,且子字线swl0上的电势在有限预充电时间期间在中间电压(例如,t3时的中点)下以较快的速率减小。这由共同晶体管614促进。通过在中间点处在预充电期间减小fx0来减小子字线swl0的电压的操作减轻在半导体存储器装置中可能发生的行锤击问题。此外,此操作减小n沟道型晶体管606的跨源极/漏极的电压差(vds)。这可防止晶体管因热载流子而劣化,因此改进子字驱动器的可靠性。

64.当存取耦合到子字线swlm+1的存储器单元时,定时图700将对于图6a的子字驱动器604相同。在此情况下,定时图700中的wlb可对应于图6a中的字线wlbn+1;fx0、fxf0可分别对应于图6a中的fx、fxf。swl0可对应于子字线swlm+1,且可由图6a中的子字驱动器604驱动。fx1、fxf1和swl1可对应于与wlbn+1相关联的另一子字驱动器(图6a中未展示)的fx驱动器线和子字线。子字驱动器604的操作与子字驱动器602的操作相同且将不重复,不同之处在于,子字驱动器604由不同字线wlbn+1驱动。此外,在子字线swl0(例如,子字线swlm+1)被驱动到中间电压的时间t3时,共同晶体管614将接通以更快地将子字线swl0朝向非活动电势vnwl驱动。这由子字驱动器602的n沟道型晶体管606促进,所述n沟道型晶体管(通过非活动字线wlbn)接通以将vnwl耦合到共同晶体管614的漏极/源极。

65.图7b是根据本公开中的实施例的在压力测试期间半导体存储器装置中的各种信号的定时图。定时图750展示当半导体存储器装置分别在t0和t1时进入和退出压力测试时字线wlb、fx驱动器线fx、fxf以及子字线swl的状态。

66.在t0之前的一些时间,半导体存储器装置过渡到激活-预充电阶段,当字线wlb操作为活动低时,字线wlb从vccp降低到接地电平。耦合到共同晶体管(例如,图6a中的晶体管614)的栅极的fx驱动器线fxf也从vdrv降低到接地电平。当共同晶体管停止导电时,耦合到共同晶体管的两个子字线(例如,图6a中的swlm和swlm+1)的行为现在彼此独立。当激活-预充电阶段开始时,fx驱动器线fx从接地电平升高到vccp,且子字线swl开始从vnwl朝向vccp升高。

67.在时间t0时或附近,可由半导体存储器装置接收测试模式信号。如果测试模式信号用于压力测试,则tm开关tmsw(例如,图5的tmsw 510和520)过渡到压力测试模式。至少部分地响应于tmsw的输出,当fx和swl继续朝向vccp升高时,fx驱动器使fxf升高到vdrv。以此方式,将压力施加到子字线swl且以类似方式施加到存储器片块中的子字线中的每一者直

到压力测试在t1附近结束为止。在此压力测试中,子字线中的每一者保持在vccp,而相应共同晶体管的栅极保持在vdrv,因此,在压力测试期间减小半导体存储器装置的总gidl。由于图7a和7b中的波形是压力测试期间的波形的非限制性实例,可存在至少基于存储器测试环境使半导体存储器装置经受压力的若干变化。

68.与半导体存储器装置的操作激活模式相比,在半导体存储器装置的测试模式中的压力测试期间,所有子字线可由所有子字驱动器驱动到活动电平(例如,vccp)以将压力施加到存储器阵列。此外,所有fx驱动器fxd可将所有fx驱动器线fxf驱动到比接地电平电压高的电压,例如驱动到vdrv电平,以使得共同晶体管614的栅极之间的电压在vccp与接地电平(例如,vdrv)之间以减小共同晶体管614的gidl。在某些情形下,位于存储器区域的边缘区域中的共同晶体管、在边缘区域中的共同晶体管的栅极电压可在测试模式期间保持在接地电平。

69.图1-7提供在测试模式中的压力测试期间减小半导体存储器装置的gidl的各种优点。例如,邻近子字驱动器中的共同晶体管放置在邻近子字驱动器的输出之间。共同晶体管中的每一者的栅极耦合到驱动器线,所述驱动器线将其电压升高到比接地电平高的电平。此配置减小共同晶体管中的每一者的栅极与漏极之间的电压,从而减小共同晶体管中的每一者的gidl。半导体存储器装置中的共同晶体管中的每一者中的gidl的这种减小又使得在压力测试期间减小半导体存储器装置的总电流,使得将不会超过半导体存储器测试器的最大电流极限。

70.从前文应了解,尽管本文中已出于说明的目的描述了本公开的特定实施例,但是可以在不脱离本公开的精神和范围的情况下进行各种修改。因此,本公开的范围不应受到本文中描述的特定实施例中的任何一者限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1