一种存储器的操作方法、读取方法、存储器及存储系统与流程

1.本技术涉及存储器技术领域,尤其涉及一种存储器的操作方法、读取方法、存储器及存储系统。

背景技术:

2.最近,随着存储器的发展,存储器可以是易失性的或非易失性的。非易失性存储器即使在未通电的情况下也能够保持数据,因此已经广泛用于蜂窝电话、数码相机、个人数字助理、移动计算设备、非移动计算设备和其它设备中,比如一种示例,3d电荷捕捉闪存(ctf,charge trapping flash)存储器的应用很广泛。3d电荷捕捉闪存存储器通过在其包含的存储单元的栅介质层中的陷阱(trap)捕获和存储电荷来实现数据存储的功能。存储单元的栅介质层中的电荷捕获和丢失引起的随机电报噪声(rtn,random telegraph noise)会影响对存储单元存储的数据的读取的正确性。

技术实现要素:

3.有鉴于此,本技术提供一种存储器的操作方法、读取方法、存储器及存储系统,调整存储单元对应的rtn的幅度,从而降低因rtn引起的读干扰。

4.为达到上述目的,本技术的技术方案是这样实现的:

5.第一方面,本技术实施例提供一种存储器的操作方法,包括:

6.确定所述存储器中的存储单元在单层单元slc擦除状态时的阈值电压的第一变化量;

7.比较所述第一变化量和参考阈值;

8.在比较结果为所述第一变化量与所述参考阈值之间不满足设定关系时,将所述存储单元在所述slc擦除状态时的阈值电压调整至具有第二变化量,使所述第二变化量与所述参考阈值之间满足所述设定关系。

9.第二方面,本技术实施例还提供一种存储器的读取方法,包括:

10.在对所述存储器的存储单元执行读取操作时,对于所述存储单元耦接的选中字线提供读取电压;

11.对与所述存储单元属于同一存储单元串中其他存储单元耦接的未选中字线提供通过电压;

12.其中,所述通过电压基于记录的总偏移量和默认通过电压确定。

13.第三方面,本技术实施例还提供一种存储器,包括:存储阵列,所述存储阵列包括存储单元;

14.及与所述存储阵列耦接且被配置为控制所述存储阵列的外围电路;

15.所述外围电路,被配置为:前述任一项所述的操作方法。

16.第四方面,本技术实施例还提供一种存储系统,包括:一个或多个前述所述的存储器;以及耦接在所述存储器的存储器控制器;所述存储器控制器,用于:向所述存储器发送

各种操作命令。

17.本技术实施例提供一种存储器的操作方法、读取方法、存储器及存储系统。其中,所述存储器的操作方法包括:确定所述存储器中的存储单元在单层单元slc擦除状态时的阈值电压的第一变化量;比较所述第一变化量和参考阈值;在比较结果为所述第一变化量与所述参考阈值之间不满足设定关系时,将所述存储单元在所述slc擦除状态时的阈值电压调整至具有第二变化量,使所述第二变化量与所述参考阈值之间满足所述设定关系。本技术实施例提供的存储器的操作方法,将存储单元的rtn与参考阈值进行比较,并且在比较结果不满足设定关系时,将其与参考阈值的比较结果调整至满足设定关系,以此降低因rtn引起的读干扰。通俗来讲,本技术实施例提供的操作方法是将存储单元的rtn的幅度(存储单元的slc擦除状态时的阈值电压的变化量表征rtn的幅度)调整至已知的最小幅度(参考阈值,比如,这个最小rtn的幅度可以为与位线相邻的存储单元对应的rtn的幅度),以使因rtn引起的读取干扰降低,以便于能够正确读取存储单元存储的数据。

附图说明

18.当结合附图阅读时,从以下具体实施例方式中可以最好地理解本技术的方面。注意,根据工业汇总的标准实践,各种特征没有按照比例绘制。事实上,为了讨论的清楚,各特征的尺寸可以任意地增加或减小。

19.图1示出相关技术中具有存储器的示例性系统的块图;

20.图2示出具有存储器的示例性存储卡的示意图;

21.图3示出具有存储器的示例性固态硬盘(ssd)的示意图;

22.图4示出包含外围电路的示例性存储器的示意图;

23.图5示出了根据本技术的一些方面的包含存储单元串的示例性存储阵列的截面的侧视图;

24.图6示出包含存储阵列和外围电路的示例性存储器的块图;

25.图7示出mlc类型的存储单元的阈值电压分布的示意图;

26.图8示出tlc类型的存储单元的阈值电压分布的示意图;

27.图9示出qlc类型的存储单元的阈值电压分布的示意图;

28.图10示出三种对存储单元的rwm产生影响的因素示意图;

29.图11示出本技术实施例提供的一种存储器的操作方法的流程示意图;

30.图12示出本技术实施例提供的确定随机电报噪声的第一变化量的流程示意图一;

31.图13示出第一读取条件中的读取电压的示意图;

32.图14示出本技术实施例提供的确定随机电报噪声的第一变化量的流程示意图二;

33.图15示出本技术实施例提供的确定随机电报噪声的第一变化量的流程示意图三;

34.图16示出本技术实施例提供的在字线wl0、wl31、wl63耦接的存储单元在slc擦除状态时的阈值电压的变化量分布的示意图;

35.图17示出本技术实施例提供的在各字线耦接的存储单元在slc擦除状态时的阈值电压的变化量分布的3σ大小的分布示意图;

36.图18示出本技术实施例提供的存储单元在slc擦除状态的变化量的调整的流程示意图;

37.图19示出本技术实施例提供的确定存储单元在slc擦除状态的变化量的调整时机的流程示意图;

38.图20示出本技术实施例提供的读取方法的流程示意图;

39.图21示出本技术实施例提供的包含64层字线的ctf利用图18的流程确定与未选定存储单元耦接的未选中字线施加的通过电压相对于默认通过电压的总偏移量的流程示意图;

40.图22示出本技术实施例提供的判断当前编程/擦除次数是否需要进行rtn调整的流程示意图;

41.图23示出本技术实施例提供的在当前的编程/擦除次数达到预设次数时对于未选中存储单元的rtn的幅度进行调整的流程示意图。

具体实施方式

42.以下公开提供了用于实施所提供的主题的不同特征的许多不同实施例或示例。下面描述部件和布置的具体示例以简化本技术。当然,这些仅仅是示例,而不是限制性的。例如,在以下描述中,第一特征形成在第二特征之上或上可以包括其中第一特征和第二特征直接接触形成的实施例,并且还可以包括附加特征可以形成在第一特征与第二特征之间使得第一特征和第二特征可以不直接接触的实施例。另外,本技术可能在各种示例中重复参考数据和/或字母。这样重复是为了简单和清楚的目的,并且其本身不指示所讨论的各种实施例和/或构造之间的关系。

43.此外,诸如“在

……

之下”、“在

……

下方”、“下部”、“在

……

上方”、“上部”等空间相对术语在本中为了便于描述可以用于描述一个元件或特征与(一个或多个)另一元件或特征的如图中所示的关系。空间相对术语旨在涵盖除了图中描绘的取向之外的在器件使用或操作中的不同取向。装置可以以其他方式定向(旋转90度或在其他取向下),并且本文所用的空间相对描述词也可以被相应的解释。

44.下面结合附图进行详细的说明本技术的技术方案。

45.图1示出相关技术中具有存储器的示例性系统的块图。在图1中,系统100可以是移动电话、台式计算机、膝上型计算机、平板计算机、车辆计算机、游戏控制台、打印机、定位设备、可穿戴电子设备、智能传感器、虚拟现实(vr,virtual reality)设备、增强现实(ar,argument reality)设备或者其中具有储存器的任何其他合适的电子设备。如图1所示,系统100可以包括主机108和存储系统102,其中,存储系统102具有一个或多个存储器104和存储器控制器106;主机108可以是电子设备的处理器,如中央处理单元(cpu,central processing unit)或者片上系统(soc,system of chip),其中,片上系统例如可以为应用处理器(ap,application processor)。主机108可以被配置为将数据发送到存储器104或从存储器104接收数据。具体的,存储器104可以是本技术中公开的任何存储器。比如,相变随机存取存储器(pcram,phase change random access memory)、三维nand闪存等等。

46.根据一些实施方式,存储器控制器106耦合到存储器104和主机108。并且被配置为控制存储器104。存储器控制器106可以管理存储在存储器104中的数据,并与主机108通信。在一些实施例中,存储器控制器106被设计为用于在低占空比环境中操作,比如在安全数字(sd,secure digital)卡、紧凑型闪存(cf,compact flash)卡、通用串行总线(usb,

universal serial bus)闪存驱动器、或用于在诸如个人计算器、数字相机、移动电话等低占空比环境的电子设备中使用的其他介质。在一些实施例中,存储器控制器106被设计为用于在高占空比环境中操作,比如固态驱动器(ssd,solid state drive)或嵌入式多媒体卡(emmc,embedded muti media card),其中ssd或emmc用作诸如智能电话、平板计算机、膝上型计算机等高占空比环境的移动设备的数据储存器以及企业存储阵列。存储器控制器106可以被配置为控制存储器104的操作,例如读取、擦除和编程操作。存储器控制器106还可以被配置为管理关于存储在或要存储在存储器104中的数据的各种功能,包括但不限于坏块管理、垃圾收集、逻辑到物理地址转换、损耗均衡等。在一些实施方式中,存储器控制器106还被配置为处理关于从存储器104读取的或者被写入到存储器104的数据的纠错码(ecc,error correction code)。存储器控制器106还可以执行任何其他合适的功能,例如,格式化存储器104。存储器控制器106可以根据特定通信协议与外部设备(例如,主机108)通信。例如,存储器控制器106可以通过各种接口协议中的至少一种与外部设备通信,接口协议例如usb协议、mmc协议、外围部件互连(pci,peripheral component interconnection)协议、pci高速(pci-e,pci express)协议、高级技术附件(ata,advanced technology attachmnet)协议、串行ata协议、并行ata协议、小型计算机小型接口(scsi,small computer small interface)协议、增强型小型磁盘接口(esdi,enhanced small disk interface)协议、集成驱动电子设备(ide,integrated drive electronics)协议、firewire协议等。

47.存储器控制器106和一个或多个存储器104可以集成到各种类型的存储设备中,例如,包括在相同封装(例如,通用闪存存储(ufs)封装或emmc封装)中。也就是说,存储系统102可以实施并且封装到不同类型的终端电子产品中。在如图2所示的一个示例中,存储器控制器106和单个存储器104可以集成到存储器卡202中。存储器卡可以包括pc卡(pcmcia,个人计算机存储器卡国际协会)、cf卡、智能媒体(sm)卡、存储器棒、多媒体卡(mmc、rs-mmc、mmcmicro)、sd卡(sd、minisd、microsd、sdhc)、ufs等。存储器卡还可以包括将存储器卡与主机(例如,图1中的主机108)耦合的存储器卡连接器204。在如图3所示的另一示例中,存储器控制器106和多个存储器104可以集成到ssd 302中。ssd还可以包括将ssd与主机(例如,图1中的主机108)耦合的ssd连接器304。在一些实施方式中,ssd的存储容量和/或操作速度大于存储器卡的存储容量和/或操作速度。此外,存储器控制器106还可以被配置为控制存储器104的擦除、读取、写入操作。

48.图4示出包含外围电路的示例性存储器的示意图。在图4所示,存储器104可以包括存储阵列401和耦合在所述存储阵列401的外围电路402,其中,存储阵列401可以是nand闪存存储阵列,其中,存储单元406以nand存储器串408的阵列的形式提供,每个nand存储器串408在衬底(未示出)上方垂直地延伸。在一些实施例中,每个nand存储器串408包括串联耦合并且垂直地堆叠的多个存储单元406。每一个存储单元406可以保持连续模拟值,例如,电压或电荷,其取决于在存储单元406的存储区域内捕获的电子的数量。每一个存储单元406可以是包括浮栅晶体管的浮栅类型的存储单元,或者是包括电荷捕获晶体管的电荷捕获类型的存储单元。

49.在一些实施例中,每个存储单元406是具有两种可能的数据状态并且因此可以存储一位数据的单级单元(slc,single level cell),例如,第一数据状态“0”可以对应第一

电压范围,并且第二数据状态“1”可以对应于第二电压范围。在一些实施例中,所述第一电压范围和第二电压范围可以称之为存储单元的阈值电压阈值电压分布。在一些实施例中,每个存储单元406是能够力在多个四个数据状态中存储对于单个位的数据的多级单元(mlc,multi level cell),例如,mlc可以每单元存储两位,每单元存储三位(又被称为三级单元(tlc,trinary level cell),或者每单元存储四位(又被称为四级单元(qlc,quadruple level cell)。其中,不论申请类型的存储单元的数据状态均包括擦除态和编程态,在对存储单元执行编程操作时,是处于擦除态的存储单元编程至某一编程态,一般来说,存储单元的编程态对应的电压范围中的电压值比较大。

50.如图4所示,每个nand存储器串408可以包括在其源极端处的源极选择栅极(ssg)410和在其漏极端处的漏极选择栅极(dsg)412。ssg 410和dsg412可以被配置为在读取和编程(或写入)操作期间激活选中的nand存储器串408(阵列的列)。在一些实施例中,同一块404中的nand存储器串408的源极通过同一源极线(sl)414(比如,公共sl)耦合。换句话说,根据一些实施方式,同一块404中的所有nand存储器串408具有阵列公共源极(acs)。根据一些实施方式,每个nand存储器串408的dsg412耦合到相应的位线416,可以经由输出总线(未示出)从位线416读取和写入数据。在一些实施例中,每个nand存储器串408被配置为通过经由一个或多个dsg线413将选择电压(比如,高于具有dsg412晶体管的阈值电压)或取消选择电压(比如,0伏特(v))施加到相应的dsg412和/或经由一个或多个ssg线415将选择电压(比如,高于具有ssg410的晶体管的阈值电压)或取消选择电压(比如,0v)施加到相应的ssg410而被选择或被取消选择。

51.如图4所示,nand存储器串408可以被组织为多个块404,多个块404的每一个可以具有公共源极线414(比如,耦合到地)。在一些实施例中,每个块404是具有擦除操作的基本数据单位,即,同一块404上的所有存储单元406同时被擦除。为了擦除选定块404中的存储单元406,可以用擦除电压(vers)(比如,高正电压20v或更高)偏置耦合到选定块404以及与选定块404同一面(plane)中的未选定块404的源极线414。应该理解,在一些示例中,可以在半块级、在四分之一块级耦或者具有任何合适数量的块或块的任何合适的分数的级执行擦除操作。相邻nand存储器串408的存储单元406可以通过字线418耦合,字线418选择存储单元406的哪一行接收读取和编程操作。在一些实施例方式中,耦合在同一字线418的存储单元406称之为页420。页420是用于编程操作或读取操作的基本数据单位,以位为单元的一页420的大小可以与一个块404中由字线418耦合的nand存储器串408的数量相关。每个字线418可以包括在相应页420中的每一个存储单元406处的多个控制栅极(栅极电极)以及耦合控制栅极的栅极线。

52.图5示出了根据本技术的一些方面的包括nand存储单元串408的示例性存储阵列401的截面的侧视图。如图5中所示,nand存储单元串408可以在衬底501上方垂直地延伸穿过存储器堆叠层502。衬底501可以包括硅(例如,单晶硅)、硅锗(sige)、砷化镓(gaas)、锗(ge)、绝缘体上硅(soi)、绝缘体上锗(goi)或者任何其他合适的材料。

53.存储器堆叠层502可以包括交替的栅极导电层503和栅极到栅极电介质层504。存储器堆叠层502中的栅极导电层503和栅极到栅极电介质层504的对的数量可以确定存储阵列401中的存储单元406的数量。栅极导电层503可以包括导电材料,导电材料包括但不限于钨(w)、钴(co)、铜(cu)、铝(al)、多晶硅、掺杂硅、硅化物或其任何组合。在一些实施方式中,

每个栅极导电层503包括金属层,例如,钨层。在一些实施方式中,每个栅极导电层503包括掺杂多晶硅层。每个栅极导电层503可以包括围绕存储单元406的控制栅极,并且可以在存储器堆叠层502的顶部处横向地延伸作为dsg线413、在存储器堆叠层502的底部处横向地延伸作为ssg线415、或者在dsg线413与ssg线415之间横向地延伸作为字线418。

54.如图5中所示,nand存储单元串408包括垂直地延伸穿过存储器堆叠层502的沟道结构505。在一些实施方式中,沟道结构505包括填充有(一种或多种)半导体材料和(一种或多种)电介质材料的沟道孔。在一些实施方式中,半导体沟道包括硅,例如,多晶硅。在一些实施方式中,存储器膜是包括隧穿层、存储层(又称为“电荷捕获/存储层”)和阻挡层的复合电介质层。沟道结构505可以具有圆柱形状(例如,柱形状)。根据一些实施方式,半导体沟道、隧穿层、存储层和阻挡层以此顺序从柱的中心朝向柱的外表面径向布置。隧穿层可以包括氧化硅、氮氧化硅或其任何组合。存储层可以包括氮化硅、氮氧化硅或其任何组合。阻挡层可以包括氧化硅、氮氧化硅、高介电常数(高k)电介质或其任何组合。在一个示例中,存储器膜可以包括氧化硅/氮氧化硅/氧化硅(ono)的复合层。

55.返回参考图4,外围电路402可以通过位线416、字线418、源极线414、ssg线415和dsg线413耦合到存储阵列401。外围电路402可以包括任何合适的模拟、数字以及混合信号电路,以用于通过经由位线416、字线418、源极线414、ssg线415和dsg线413将电压信号和/或电流信号施加到每个目标存储单元406以及从每个目标存储单元406感测电压信号和/或电流信号来促进存储阵列401的操作。外围电路402可以包括使用金属-氧化物-半导体(mos)技术形成的各种类型的外围电路。例如,图6示出了一些示例性外围电路,外围电路402包括页缓冲器/感测放大器604、列解码器/位线驱动器606、行解码器/字线驱动器608、电压发生器610、控制逻辑单元612、寄存器614、接口616和数据总线618。应当理解,在一些示例中,还可以包括图6中未示出的附加外围电路。

56.页缓冲器/感测放大器604可以被配置为根据来自控制逻辑单元612的控制信号从存储阵列401读取数据以及向存储阵列401编程(写入)数据。在一个示例中,页缓冲器/感测放大器604可以存储要被编程到存储阵列401的一个页420中的一页编程数据(写入数据)。在另一示例中,页缓冲器/感测放大器604可以执行编程验证操作,以确保数据已经被正确地编程到耦合到选定字线418的存储单元406中。在又一示例中,页缓冲器/感测放大器604还可以感测来自位线416的表示存储在存储单元406中的数据位的低功率信号,并且在读取操作中将小电压摆幅放大到可识别的逻辑电平。列解码器/位线驱动器606可以被配置为由控制逻辑单元612控制,并且通过施加从电压发生器610生成的位线电压来选择一个或多个nand存储器串408。

57.行解码器/字线驱动器608可以被配置为由控制逻辑单元612控制,并且选择/取消选择存储阵列401的块404并且选择/取消选择块404的字线418。行解码器/字线驱动器608还可以被配置为使用从电压发生器610生成的字线电压来驱动字线418。在一些实施方式中,行解码器/字线驱动器608还可以选择/取消选择并且驱动ssg线415和dsg线413。如下文详细描述的,行解码器/字线驱动器608被配置为对耦合到(一个或多个)选定字线418的存储单元406执行擦除操作。电压发生器610可以被配置为由控制逻辑单元612控制,并且生成要被供应到存储阵列401的字线电压(例如,读取电压、编程电压、通过电压、局部电压、验证电压等)、位线电压和源极线电压。

58.控制逻辑单元612可以耦合到上文描述的每个外围电路,并且被配置为控制每个外围电路的操作。寄存器614可以耦合到控制逻辑单元612,并且包括状态寄存器、命令寄存器和地址寄存器,以用于存储用于控制每个外围电路的操作的状态信息、命令操作码(op码)和命令地址。接口616可以耦合到控制逻辑单元612,并且充当控制缓冲器,以缓冲从主机(未示出)接收的控制命令并且并将其中继到控制逻辑单元612,以及缓冲从控制逻辑单元612接收的状态信息并且将其中继到主机。接口616还可以经由数据总线618耦合到列解码器/位线驱动器606,并且充当数据i/o接口和数据缓冲器,以缓冲数据并且将其中继到存储阵列401或从存储阵列401中继或缓冲数据。

59.对于上述描述的存储系统及存储器来说,读取窗口裕度(rwm,read window margin)是其正确读取存储单元数据的重要参数。对于rwm的定义可以分为两种:第一种,rwm为存储单元相邻两个数据态对应的阈值电压分布之间的间隔之和,比如,如图7所示的mlc类型的存储单元的阈值电压分布进行说明。如图7所示,mlc类型的存储单元的第一个rwm可以为擦除态s1与编程态s2之间的电压区间。第二种,rwm可以被定义为存储单元的编程态的编程验证电压与用于区分该编程态与其相邻数据态的读取电压之间的电压区间,比如图7中包含的rwm为:v

rd1

到v

fy1

之间的电压区间、v

rd2

到v

fy2

之间的电压区间以及v

rd3

到v

fy3

之间的电压区间,其中,v

rd1

、v

rd2

、v

rd3

为区分擦除态s1与编程态s2的读取电压、区分擦除态s2与编程态s3的读取电压、区分擦除态s3与编程态s4的读取电压;v

fy1

、v

fy2

、v

fy3

分别为编程态s2的编程验证电压、编程态s3的编程验证电压、编程态s4的编程验证电压。随着单个存储单元能够存储数据密度的进一步增加,rwm的宽度减小了,比如,图8所示的tlc类型的存储单元的阈值电压分布和图9所示的qlc类型的存储单元的阈值电压分布,二者所展示的rwm比图7所示的mlc类型的存储单元对应的rwm较窄。在对存储器执行读取操作时,若想要正确读取存储单元的数据需要足够宽度的rwm。而对于rwm的影响的因素众多,如图10所示,其示出三种主要的影响存储单元的rwm的因素。在众多因素中,编程精度以及字线间的耦合对于rwm的影响的研究较多,但对于rtn对rwm的影响以及如何降低因rtn引起的读干扰的研究比较少。

60.经研究,因存储单元的电子捕获和电子丢失引起的rtn是平面nand闪存在读取操作期间存储单元的阈值电压波动的主要因素之一。而存储单元的阈值电压波动是引起rwm变化的原因,也就是说,存储单元的rtn会影响rwm,进而影响存储单元存储的数据的正确读取。其中,rtn是一种电子器件中固有噪声中非高斯分布的噪声,其为电子器件存在的缺陷或陷阱俘获和释放电荷所造成的电荷迁移扰动,宏观上即为引起电流波动。因此,对于包含材料为多晶硅的沟道结构505的存储器而言,比如,3d nand闪存,再比如,3d电荷捕获型闪存(ctf,charge trap flash),沟道结构505包含多晶硅,是存在缺陷或陷阱的,再结合前述描述的存储单元存储数据的原理的介绍,存储单元的电荷捕获层需要捕获和释放电荷,从而进行数据的存储与擦除,那么,在存储单元对应的沟道中存在rtn,其会使存储单元的阈值电压波动,从而对存储器的rwm产生影响,进而影响存储单元的正确读取。

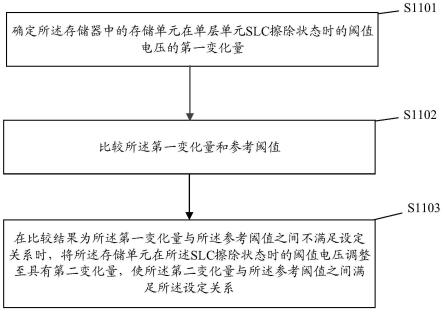

61.为了解决上述的技术问题,参看图11,本技术实施例提供一种存储器的操作方法。具体地,所述操作方法包括:

62.s1101:确定所述存储器中的存储单元在单层单元slc擦除状态时的阈值电压的第一变化量。

63.需要说明的是,这里描述的所述存储器的结构可以包含前述图1至7所述描述的结构,也可以包括其他已知的结构。基本的,所述存储器包括存储单元串,所述存储单元串包括依次电连接的位线、多个存储单元以及源极线,其中,多个存储单元中的每一层耦接在同一字线上,可以形成一个物理存储页(page)。关于存储单元串的结构的其他描述可以参见前述图1至图6,这里不再赘述。

64.由于对存储单元的rwm的影响的因素众多,为了排除其他因素的影响,仅单独解决rtn对rwm影响带来读干扰的问题,经研究,存储器包含的存储单元对应的rtn的幅度可以采用存储单元在slc擦除状态时的阈值电压的变化量进行衡量,且rtn的幅度与存储单元在slc擦除状态时的阈值电压的变化量呈正相关,存储单元在slc擦除状态时的阈值电压的变化量越大,存储单元对应的rtn的幅度也就越大。另外,存储单元对应的rtn对存储单元的rwm的影响与rtn的幅度也呈正相关;也就是说,rtn的幅度越大,对存储单元的阈值电压分布的影响也就越大,进而使得对存储单元对应的rwm影响也就越大(rwm变窄),从而在执行读取操作时,存储单元对应的干扰也就越大。也即是:所述存储单元在单层单元slc擦除状态时的阈值电压的变化量用于衡量所述存储单元对应的rtn的幅度。

65.在一些实施例中,对于步骤s1101,一种可选的实现方式可以参见图12,具体流程可以包括:

66.s1201:对所述存储单元所在存储块进行擦除操作,使所述存储块包含的存储单元均被擦除至所述slc擦除状态;

67.s1202:基于第一读取条件对所述存储单元执行多次读取操作;

68.s1203:获得每次读出的所述存储单元的阈值电压的电压值;

69.s1204:基于每一个电压值确定所述第一变化量。

70.需要说明的是,前述已经说明存储单元对应的rtn的幅度是依据存储单元在slc擦除状态的阈值电压的变化量来衡量的,因此,需要对存储单元所在存储块执行擦除操作,使得存储单元处于slc擦除状态。因此,获得存储单元在slc擦除状态的阈值电压的第一变化量的第一步也就是对所述存储单元所在存储块进行擦除操作,使所述存储块包含的存储单元均被擦除至所述slc擦除状态。

71.之后,按照第一读取条件对所述存储单元连续执行多次读取操作。其中,读取次数可以根据具体情况进行设计,在此不作限定。在一种示例,可以按照第一读取条件对存储单元连续读取10次。

72.这里,所述第一读取条件可以包括:

73.对与所述存储单元耦接的选中字线施加一组读取电压;

74.对与所述存储单元属于同一存储单元串中的其他存储单元耦接的未选中字线施加相应的默认通过电压;

75.其中,所述一组读取电压包括位于所述slc擦除状态对应的阈值电压分布的最小电压值到最大电压值之间的一组电压值。

76.这里,所说的一组读取电压包括位于所述slc擦除状态对应的阈值电压分布的最小电压值到最大电压值之间的一组电压值。如图13所示,其示出本发明实施例提供slc类型的存储单元的阈值电压分布示意图。其中,l0态对应的阈值电压分布即为slc擦除状态对应的阈值电压分布。存储单元在连续执行多次读取操作时被擦除至l0态。所说的一组读取电

压的一种示例也即图13所说的v1至v7。

77.所说的基于第一读取条件对所述存储单元执行多次读取操作可以是指连续的对所述存储单元按照第一读取条件执行多轮读取操作。在每一轮读取操作时,对存储单元耦接的选中字线施加的读取电压从所述一组读取电压中最小值扫描最大值依次施加,对与所述存储单元属于同一存储单元串中的其他存储单元耦接的未选中字线施加相应的默认通过电压vpass0,然后这一轮读取操作的多个存储单元的阈值电压的电压值。依次进行多轮读取操作,获得每轮读取操作的多个电压值。然后依据每一个电压值确定所述第一变化量。

78.举例来说,假设所说的一组读取电压的一种示例也即图13所说的v1至v7,那么,对存储单元执行某一轮读取操作,也就是,将读取电压从v1至v7依次施加到所述存储单元耦接的选中字线,这一轮中,每一次读取操作时,其余同一存储单元串中的未选中字线上均施加默认通过电压vpass0,基于外围电路包含的感测放大电路测量存储单元每次读取的阈值电压的电压值。

79.需要说明的是,在对存储器执行一次读取操作时,某一存储单元串中要读取的存储单元为选中存储单元,与该存储单元耦接的字线为选中字线;在该次读取操作时,同一存储单元串中不需要读取的其他存储单元为未选中存储单元,与该未存储单元耦接的字线为未选中字线。

80.所说的默认通过电压vpass0可以是指在对存储器执行读取操作时,对未选中存储单元耦接的未选中字线提供的电压值,其可以为经验值或出厂默认值

81.在对所述存储单元执行多次读取操作后,在一些实施例中,对于步骤s1203,可以包括:

82.基于每一个所述电压值获取所述存储单元的阈值电压的平均电压值;

83.基于所述每一个所述电压值中的任一电压值与所述平均电压值确定所述第一变化量。

84.具体地,第一变化量的计算可以采用如下公式:

85.δv

th0

=v

th,i-v

th,avg

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(1)

86.其中,δv

th0

为所述存储单元在slc擦除状态时的阈值电压的第一变化量;v

th,i

为多轮读取操作中第i轮读取操作时测量出的所述存储单元的阈值电压的电压值,其中,i为多轮读取操作中的任意一轮;v

th,avg

为所述多次读取操作测量出的所述存储单元的阈值电压的电压值的平均值,也即平均电压值。

87.上述计算公式表示的也就是基于所述每一个所述电压值中的任一电压值与所述平均电压值确定所述第一变化量。

88.在另一些实施例中,对于步骤1102,参见图14,其示出另一种可选的实现方式。具体流程可以包括:

89.s1401:对所述存储单元所在存储块进行擦除操作,使所述存储块包含的存储单元均被擦除至所述slc擦除状态;

90.s1402:基于第一读取条件对与选中字线耦接的各存储单元执行多次读取操作,获得所述各存储单元的阈值电压的变化量分布;所述选中字线为所述存储块中与所述存储单元耦接的字线;

91.s1403:确定所述变化量分布的3σ作为所述第一变化量。

92.需要说明的是,步骤s1401与前述步骤s1201是一样的,在此不再赘述。在实际读取过程中,所述第一变化量也可以是存储单元在slc擦除状态的阈值单元分布的变化量的3σ。其中,获取3σ的方式可以包括但不限于如下两种方式:一种方式为,对与所述存储单元在同一选中字的所有存储单元中的每一个存储单元执行前述图12的步骤,获得每一个存储单元在slc擦除状态的阈值电压对应的变化量,以形成在slc擦除状态的变化量分布,再根据这个变化分布确定其对应的3σ;另一种方式为,对与所述存储单元在同一存储块的所有存储单元中的每一个存储单元执行前述图12的步骤,获得每一个存储单元在slc擦除状态的阈值电压对应的变化量,以形成在slc擦除状态的变化量分布,再根据这个变化分布确定其对应的3σ。

93.在一些实施例中,所述方法还包括:在对所述存储块执行擦除操作后,等待第一预设时长。

94.需要说明的是,上述擦除操作及等待是为了避免背景模式依赖(bpd,background pattern dependency)响应的影响以及刚擦除时,存储块包含的存储单元的电荷不稳定的影响。其中,第一预设时长可以根据实际情况进行设置。举例来说,所述第一预设时长可以为30分钟。

95.基于前述描述,对所述存储单元的rtn的幅度的评估的一种具体的可实现的流程,如图15所示,可以包括:

96.s1501:对所述存储单元所在存储块进行擦除操作,使所述存储块包含的存储单元均被擦除至所述slc擦除状态;

97.s1502:在擦除操作之后,等待30分钟;

98.s1503:按照所述第一读取条件连续读取所述存储块或者所述存储单元10次;

99.s1504:计算所述存储块包含的存储单元的阈值电压的变化量分布或所述存储单元的阈值电压的变化量;

100.s1505:将所述变化量作为第一变化量;或获得所述变化量分布的3σ,将所述3σ为所述第一变化量。

101.需要说明的是,这里仅以一种示例形式展示所述存储单元对应的rtn的幅度的评估方式。对于步骤s1504中的所述存储单元的阈值电压的变化量;或者变化量分布的3σ的计算前述已经详细说明如何计算,在此不再赘述。

102.s1102:比较所述第一变化量和参考阈值。

103.这里,所述参考阈值可以为所述存储器中因rtn引起的读取干扰最小的存储单元对应的rtn的幅度的评估值。经研究,如图16和图17所示,在同一存储单元串中的存储单元,从靠近源极线的存储单元到靠近位线的存储单元,对应的rtn的幅度依次减小,也就是说,与位线相邻的存储单元对应的rtn的幅度最小,对存储单元的rwm产生的影响是最小的。因此,将所述存储单元的阈值电压的第一变化量与参考阈值进行比较,在比较结果为第一变化量与参考阈值之间不满足设定关系时,将二者关系调整至满足设定关系,以使所述存储单元对应的rtn的幅度降低,以此,降低因rtn引起的读取干扰。需要说明的是,图16中的纵坐标为概率值,可以是指一个字线中耦接的所有存储单元处于某一阈值电压的变化量的的概率值,其可以通过获得处于某一阈值电压的变化量的存储单元的个数与一个字线中耦接的所有存储单元的总个数进行比值获得。图16中的横坐标为在所述第一读取条件下存储单

元在slc擦除状态的阈值电压的变化量。图16描绘了字线wl0、wl31、wl63上的存储单元在slc擦除状态的阈值电压的变化量分布,其中,字线wl0、wl31、wl63在存储单元串的位置依次从下到上(或者,在存储单元串中从靠近源极线到靠近位线依次部署)。图17中的横坐标为字线;纵坐标为3σ的大小。

104.因此,在一些实施例中,所述参考阈值为所述存储单元串中与位线相邻的存储单元在所述slc擦除状态时的阈值电压的变化量。

105.s1103:在比较结果为所述第一变化量与所述参考阈值之间不满足设定关系时,将所述存储单元在所述slc擦除状态时的阈值电压调整至具有第二变化量,使所述第二变化量与所述参考阈值之间满足所述设定关系。

106.在一些实施例中,所述在比较结果为所述第一变化量与所述参考阈值之间不满足设定关系时,将所述存储单元在单层单元slc擦除状态时的阈值电压调整至具有第二变化量,可以包括:

107.使所述存储单元擦除至所述slc擦除状态;

108.逐步调整第一读取条件,基于每一次调整后的第一读取条件对所述存储单元执行多次读取操作,直到将所述存储单元在所述slc擦除状态时的阈值电压调整至具有第二变化量。

109.需要说明的是,在每次确定存储单元的rtn的幅度时,需要将存储单元擦除到slc擦除状态,以消除其他因素对rwm产生的影响。这里,使所述存储单元擦除至所述slc擦除状态的方式也就是前述的步骤s1201和步骤s1401所述的方式,在此不再赘述。

110.这里,所述设定关系可以包括所述存储单元的阈值电压的变化量与所述参考阈值之间的差值的绝对值小于或等于预设阈值。所说的预设阈值可以根据实际情况进行设置,其可以是经验值。比如,所述预设阈值可以为参考阈值与设定百分比的乘积,其中,设定百分比越小,读取正确的概率越大。其中,所述设定百分比可以设置但不限制为10%。

111.基于前述描述,上面描述的过程也就是,在所述比较结果为所述第一变化量与所述参考阈值不满足所述设定关系时,则需要调整所述存储单元在slc擦除状态的阈值电压的变化量,使得调整后的阈值电压的变化量参考阈值之间满足设定关系,从而使所述存储单元对应的rtn的幅度调整至最低,对存储单元的rwm产生的影响降至最低,进而提高对存储单元存储数据的读取正确率。

112.需要说明的是,调整后的存储单元的第二变化量与所述参考阈值之间满足设定关系的另一种说法可以认为所述第二变化量与所述参考阈值大约相等,也就是说,在所述第二变化量与所述参考阈值之间的差值的绝对值小于或等于所述预设阈值时,可以认为所述第二变化量与所述参考阈值相等。

113.在一些实施例中,所述逐步调整第一读取条件,可以包括:

114.对与所述存储单元耦接的选中字线施加的一组读取电压保持不变;

115.对与所述存储单元属于同一存储单元串中的其他存储单元耦接的未选中字线施加的通过电压在默认通过电压的基础上按照设定偏移量逐步增加。

116.需要说明的是,经研究,所述存储单元对应的rtn的幅度随着同一存储单元串中的未选中字线上的通过电压的增加而减小,因此,在所述第一变化量与所述参考阈值不满足设定关系时,逐步调整第一读取条件,按照调整的第一读取条件获得存储单元的阈值电压

的变化量,直到获得的第二变化量与参考阈值之间满足设定关系,其中,逐步调整第一读取条件的方式:对选中字线施加的读取电压保持不变,对同一存储单元串中未选中字线施加的通过电压在默认通过电压的基础上按照设定偏移量逐步增加。该设定偏移量可以是系统可提供的默认偏移量。

117.举例说明,假设总共需要3次调整,使得存储单元在slc擦除态的阈值电压达到第二变化量;设定偏移量为p;读取电压为前述的v1至v7。基于此,逐步调整第一读取条件也就是:第一次调整第一读取条件,获得的读取条件为:读取电压为前述的v1至v7,通过电压为vpass0+p;第二次调整第一读取条件,获得的读取条件为:读取电压为前述的v1至v7,通过电压为vpass0+2p;第三次调整第一读取条件,获得的读取条件为:读取电压为前述的v1至v7,通过电压为vpass0+3p。

118.需要说明的是,在同一存储单元串中处于不同位置的未选中字线所需要的vpass0的值的大小是不一样,也就是,在申请中,同一存储单元串中处于不同位置的未选中字线施加的默认通过电压vpass0的大小可以是不同的。对应的,不同位置字线对应的设定偏移量可能也是不一样的。

119.举例来说,假设存储器的存储单元串的字线依次从下到上为:wl0、wl1、

……

、wln、

……

;在对存储单元串中与字线wln耦接的存储单元读取时,其余字线施加的默认通过电压vpass0如表1所示,分别为:不同的电压值vpass0-1、vpass0-2、vpass0-3。基于此,在不同位置的未选中字线上施加的是默认通过电压vpass0的电压值是不同的,不同位置的未选中字线对应的设定偏移量可以相同,也可能不同,根据存储器内部的外围电路中的电压发生器所运行的系统能够提供的而定,比如,在均不同时,vpass0-1对应的设定偏移量可能是50毫伏(mv);vpass0-2对应的设定偏移量可能是20mv;vpass0-3对应的设定偏移量可能是10mv。再比如,均相同时,vpass0-1、vpass0-2、vpass0-3对应设定偏移量可能是任何系统能够提供的电压增量步长,如,50mv、20mv、10mv任一种。不同位置的未选中字线对应的设定偏移量也可以部分相同、部分不同,可以以可能的任意组合,在此不再一一赘述。

120.表1

121.字线wl默认通过电压vpass0的电压值wln&abovevpass0-2wln+3vpass0-2wln+2vpass0-2wln+1vpass0-1wlnvreadwln-1vpass0-1wln-2vpass0-3wln-3vpass0-3wln-4&wl16vpass0-3wl2-wl15vpass0-3wl0-wl1vpass0-3

122.上述调整过程也就是,在对所述默认通过电压的基础上,逐步增加对与所述存储单元属于同一存储单元串的未选中存储单元提供的通过电压(也就是:增加施加在与所述

未选中存储单元耦接的未选中字线上的通过电压),并确定在每次增加后的通过电压后所述存储单元对应的rtn的幅度(也即存储单元在slc擦除状态的阈值电压的变化量),直到在某一次增加后的通过电压下,所述存储单元在slc擦除状态的阈值电压的变化量与所述参考阈值之间满足设定关系为止,此时所述选存储单元在slc擦除状态的阈值电压的变化量为前述第二变化量,至此完成所述存储单元对应的rtn的幅度的调整。需要说明的是,每次增加未选中字线上的通过电压后,仍然按照第一读取条件中的读取电压,读取所述存储单元多次或者读取与所述存储单元属于同一字线的所有存储单元多次或者读取与所述存储单元属于同一存储块的所有存储单元多次,以获得所述存储单元在slc擦除状态的阈值电压的第二变化量。

123.在一些实施例中,所述方法还包括:

124.在所述存储单元在所述slc擦除状态时的阈值电压调整至具有第二变化量时,记录对所述未选中字线施加的通过电压相对于默认通过电压的总偏移量。

125.这里,所述总偏移量为之前获得的所述存储单元在slc擦除状态时的阈值电压的变化量与所述参考阈值满足所述设定关系时,与所述存储单元属于同一存储单元串中的其他存储单元耦接的未选中字线施加的通过电压相对于默认通过电压的偏移量。换句话说,根据本技术实施例提供的操作方法可以得到使存储单元对应的rtn的幅度最小时对应的通过电压相对于默认通过电压的总偏移量,在后续执行读取操作时,利用该电总偏移量加上默认通过电压得到对所述存储单元提供的通过电压,在该通过电压下,读取干扰最小。

126.在一些实施例中,在比较结果为所述第一变化量与所述参考阈值之间满足所述设定关系时,反馈指示信息或等待第二预设时长,以结束对所述存储单元在所述slc擦除状态时的阈值电压的调整。

127.需要说明的是,第二预设时间可以人为定制,在本技术中不作限制。

128.为了理解上述rtn的幅度的调整过程,参见如图18所示。所述存储单元的rtn的幅度调整方式具体包括:

129.s1801:基于第一读取条件确定与所述存储单元属于同一存储单元串的与位线相邻的存储单元在slc擦除状态时的阈值电压的变化量,获得参考阈值;

130.s1802:基于所述第一读取条件确定所述存储器中的存储单元在slc擦除状态时的阈值电压的第一变化量;

131.s1803:比较所述第一变化量与所述参考阈值;

132.s1804:在比较结果为所述第一变化量与所述参考阈值满足所述设定关系时,反馈指示信息或等待第二预设时长,以结束对所述存储单元在所述slc擦除状态时的阈值电压的调整,结束流程;

133.s1805:在比较结果为所述第一变化量与所述参考阈值不满足所述设定关系时,使所述存储单元擦除至所述slc擦除状态;逐步调整第一读取条件,基于每一次调整后的第一读取条件对所述存储单元执行多次读取操作,直到将所述存储单元在所述slc擦除状态时的阈值电压调整至具有第二变化量,所述第二变化量与所述参考阈值之间满足设定关系,结束流程。

134.需要说明的是,在步骤s1805中逐步调整第一读取条件,重新执行步骤1802至1803,直到所述存储单元的第二变化量与所述参考阈值之间满足设定关系为止,结束流程。

这里所说的结束流程是对存储单元串上的某一存储单元的rtn进行调整完成时的结束流程。对于同一存储单元串中的任一存储单元的rtn的幅度的调整均可按照步骤1801至步骤s1805进行调整。

135.需要说明的是,该流程中参考阈值、第一变化量以及第二变化量的前述已经详细说明在此不再赘述。

136.在实际应用过程中,所述存储单元对应的rtn的幅度是随着所述存储器的擦除/编程次数的增加而增加,因此,对于所述存储单元的rtn的幅度的调整需要在所述存储单元的擦除/编程寿命内,进行多次调整,以降低后续读取的干扰。

137.因此,在一些实施例中,所述方法还可以包括:

138.确定对所述存储单元所在存储块已经执行的编程/擦除次数;

139.判断所述编程/擦除次数是否达到预设次数;

140.在所述编程/擦除次数达到所述预设次数时,重新确定所述存储单元在所述slc擦除状态时的阈值电压的第三变化量;并在所述第三变化量与所述参考阈值不满足所述设定关系时,调整所述存储单元在所述slc擦除状态时的阈值电压的变化量,使所述变化量与所述参考阈值满足所述设定关系。

141.需要说明的是,这里描述的是,在编程/擦除次数达到预设次数时,就进行上述描述所述存储单元的rtn的幅度进行调整,以得到后续读取操作时对所述未选中存储单元提供的通过电压进行补偿的总偏移量,从而降低因rtn引起的读干扰。

142.在一些实施例中,所述预设次数基于所述存储单元的最大编程/擦除次数和设定评估周期确定;其中,所述设定评估周期用于反映相邻两次调整所述存储单元在所述slc擦除状态时的阈值电压的变化量的时间间隔。

143.需要说明的是,所说的最大编程/擦除次数可以是指在所述存储单元的擦除/编程寿命内,能够进行编程/擦除的最大次数。所说的设定评估周期也就是人为设计的,用于反映相邻两次调整所述存储单元在所述slc擦除状态时的阈值电压的变化量的时间间隔,换句话说,也就是,在所述最大编程/擦除次数内,编程/擦除多少次进行一次所述存储单元的rtn的幅度的调整。所述预设次数的确定可以包括:首先通过所述最大编程/擦除次数除以设定评估周期得到在所述最大编程/擦除次数内需要调整rtn的次数,然后,将0至需要调整rtn的次数之间的所有整数依次乘以设定评估周期以获得所述预设次数。

144.举例来说,假设所述最大编程/擦除次数为1000,设定评估周期为100,那么,需要调整rtn的次数为10次,此时,所述预设次数为0、100、200、300、400、500、600、700、800、900、1000。

145.对于上述判断何时进行存储单元对应的rtn的幅度的调整,具体流程可以如图19所示,所述流程包括:

146.s1901:确定所述存储单元的最大编程/擦除次数为m;

147.s1902:确定当前对所述存储单元的编程/擦除次数为z;

148.s1903:判断所述编程/擦除次数是否达到预设次数;

149.需要说明的是,对于s1903中如何判断所述编程/擦除次数是否达到预设次数,可以采用以下公式进行判断:z是否等于n*m/n,其中,n为最大编程/擦除次数m与设定评估周期的商,比如,n=10;n为0至10任一个整数。

150.s1904:在所述编程/擦除次数达到预设次数时,重新确定所述存储单元在所述slc擦除状态时的阈值电压的第三变化量;并在所述第三变化量与所述参考阈值不满足所述设定关系时,调整所述存储单元在所述slc擦除状态时的阈值电压的变化量,使所述变化量与所述参考阈值满足所述设定关系;

151.s1905:在所述编程/擦除次数未达到预设次数时,不对所述存储单元在slc擦除状态的阈值电压的变化量进行调整,结束流程。

152.在一些实施例中,所述方法还包括:在当前的所述编程/擦除次数为零时,基于第一读取条件直接确定所述存储单元在slc擦除状态时的阈值电压的第三变化量。

153.在一些实施例中,所述方法还可以包括:

154.在当前的所述编程/擦除次数不为零且达到所述预设次数时,获取已记录的总偏移量;所述总偏移量为之前获得的所述存储单元在slc擦除状态时的阈值电压的变化量与所述参考阈值满足所述设定关系时,与所述存储单元属于同一存储单元串中的其他存储单元耦接的未选中字线施加的通过电压相对于默认通过电压的偏移量;

155.基于所述总偏移量和第一读取条件获得第二读取条件;

156.基于所述第二读取条件确定所述存储单元在所述slc擦除状态时的阈值电压的第三变化量。

157.需要说明的是,这里描述的是,在预设次数为0时,对所述存储单元对应的rtn进行调整是第一次,前面没有记录的通过电压的总偏移量。因此,获取所述存储单元在slc擦除状态时的阈值电压的第三变化量的读取条件为第一读取条件。在预设次数不为0时,已经有记录的总偏移量,因此,获取获取所述存储单元在slc擦除状态时的阈值电压的第三变化量的读取条件为为第二读取条件。该第二读取条件为已记录的总偏移量和第一读取条件确定的,也就是,第一读取条件中的默认通过电压加上总偏移量。

158.基于前述的操作方法,如图20所示,本技术实施例还提供一种读取方法,可以包括:

159.s2001:在对所述存储器的存储单元执行读取操作时,对于所述存储单元耦接的选中字线提供读取电压;

160.s2002:对与所述存储单元属于同一存储单元串中其他存储单元耦接的未选中字线提供通过电压;其中,所述通过电压基于记录的总偏移量和默认通过电压确定。

161.需要说明的是,上面描述的是,在对存储器执行读取操作时,对于同一存储单元串上,未选中存储单元需要的通过电压,可采用上述描述的操作方式确定。具体如何获得前述已经描述清楚,在此不再一一赘述。

162.本技术实施例提供的存储器的操作方法,将存储单元的rtn与参考阈值进行比较,并且在比较结果不满足设定关系时,将其与参考阈值的比较结果调整至满足设定关系,以此降低因rtn引起的读干扰。通俗来讲,本技术实施例提供的操作方法是将存储单元的rtn的幅度(存储单元的slc擦除状态时的阈值电压的变化量表征rtn的幅度)调整至已知的最小幅度(参考阈值,比如,这个最小幅度可以为与位线相邻的存储单元对应的rtn的幅度),以使因rtn引起的读取干扰降低,以便于能够正确读取存储单元存储的数据。

163.为了理解本技术实施例提供的操作方法以及读取方法,下面以包含64层字线的3d ctf为例进行说明。具体参见如图21至23所示。

164.图21示出本技术实施例提供的包含64层字线的ctf利用rtn获得每一层字线对应的未存储单元的通过电压相对于默认通过电压的总偏移量的流程示意图。具体的,在步骤s2101中,使与字线wl63耦接的存储单元处于slc擦除状态,基于第一读取条件对3d ctf的某一存储块连续读取多次;其中,所述第一读取条件包括:对同一存储单元串中未选中字线提供的通过电压vusel为默认通过电压vpass0,对同一存储单元串中选中字线提供的读取电压vsel为vread;在步骤s2102中,对与字线wl63耦接的存储单元在slc擦除状态的阈值电压的变化量进行计算,获得参考阈值;具体包括:使与字线wl63耦接的存储单元处于slc擦除状态;以与字线wl63耦接的存储单元为选中存储单元,其余为未选中存储单元;按照上述第一读取条件读取多次后,获得与字线wl63耦接的存储单元的阈值电压的变化量分布;基于该变化量分布获得与字线wl63耦接的存储单元的阈值电压的变化量分布对应的3σ,记为σ

63

,该σ

63

作为参考阈值;在步骤s2103中,分别获得与字线wl0至字线wl62耦接的存储单元在slc擦除状态的阈值电压的变化量分布对应的3σ,分别记为σ0~σ

62

,其中,每一个均可称之为第一变化量。具体计算流程如步骤s2102中所描述,在此不再赘述。在步骤s2104中,分别将字线wl0至字线wl62对应的3σ与所述参考阈值σ

63

进行比较,若某一个字线耦接的存储单元对应的σi等于所述参考阈值σ

63

(σ

63

近似等于σi,也就是前述描述的二者满足设定关系),则该字线耦接的存储单元对应的rtn的幅度不用调整,此时该字线耦接的存储单元在为选中存储单元时,其它未选中存储单元被提供的通过电压即可以为所述默认通过电压vpass0;若某一字线耦接的存储单元的σi大于所述参考阈值σ

63

,则该字线耦接的存储单元对应的rtn的幅度需要通过增加其它未选中字线的通过电压进行调整,直达σi等于σ63(σ

63

近似等于σi,也就是前述描述的二者满足设定关系)为止。需要说明的是,调整可能不是一次能够完成的,需要多次才能使σi等于σ63。这里,通过步骤s2105和步骤s2106,实现每次的rtn的调整的,其中,步骤s2105是判断通过电压是否增加到最大值(通过电压也不是可以无限增加的,无限增加有可能会引入其他的读干扰问题);步骤s2106中,获得新的读取条件的方式,其中,δv就是每次调整rtn时,通过电压增加的设定偏移量。在步骤s2107中,在σi等于σ63后,通过公式δvpass(i)=vpass(i)-vpass获得该字线施加的通过电压相对于默认通过电压的总偏移量δvpass(i);在步骤s2108中,将δvpass(i)发送到存储器控制器或控制逻辑单元的微控制器中保存,以备后续读取操作使用。

165.需要说明的是,vusel表示的是未选中字线上施加的通过电压;vsel表示的是选中字线上施加的读取电压。对于步骤s2102和s2103中的存储单元对应的rtn的评估,前面描述的方式进行,在此不再赘述。

166.图22示出本技术实施例提供的判断当前编程/擦除次数是否需要进行rtn调整的流程示意图。如图22所示,在步骤s2201中,确定所述存储器的最大编程/擦除次数,记为m;在步骤s2202中,对所述存储器的某一存储块执行编程/擦除;在步骤s2203中,确定所述存储器中所述存储块当前的编程/擦除次数,记为z;在步骤s2204中,采用判断语句if z=n*m/n?判断是否到达预设次数;若到达预设次数,执行步骤s2205,执行图21中的调整流程;若没有到达预设次数,结束流程。

167.在当前的编程/擦除次数达到预设次数时,对于进行rtn的调整还分两种情况,如图23所示。

168.在步骤s2301中,判断当前编程/擦除次数是否为零,在为零时,执行步骤s2302,直

接以图21所示的流程进行各字线耦接的存储单元对应的rtn的幅度进行调整,以获得各字线对应为选中的字线时其它未选中字线的通过电压相对于默认通过电压的总偏移量,以备后续读取使用;在不为零时,执行步骤s2303,获得前一次rtn调整各字线对应的总偏移量;在获得记录的总偏移量δvpass(i)后,执行步骤s2304,获得新的读取条件;之后执行步骤s2305,按照新的读取条件执行图21所示的流程对各字线耦接的存储单元对应的rtn的幅度进行调整,以获得各字线为未选中的字线时的通过电压相对于默认通过电压的新的总偏移量,以备后续读取操作时使用。

169.本技术实施例提供的操作方法,实质上是利用存储单元的rtn的幅度进行调整,以获得后续读取操作对于未选中字线提供的通过电压,以此方式,降低对存储单元执行读取操作时因其对应的rtn引起的读取干扰。该操作方法可以改善不同位置的存储单元的rtn的幅度,从而可以有效的改善由于字线位置差异对rwm一致性的影响。由此带来,有效改善同一存储单元串上字线耦接的存储单元的rtn的一致性;有效地减小字线位置对rtn和读取窗口裕度的影响;可以基于存储器的使用情况进行补偿rtn幅度的校准;不需要额外的工艺改进等优点。

170.本技术实施例还提供一种存储器,包括:用于存储数据的存储阵列;以及与所述存储阵列耦接且用于控制所述存储阵列的外围电路;其中,所述外围电路被配置为:实现前述任一项所述的操作方法。

171.在一些实施例中,所述外围电路包括:寄存器,用于存储记录的总偏移量。

172.要说明的是,该存储器与前述的对存储器的擦作方法属于同一发明构思,该存储器中出现的名词在前述的编程方法中均以详细解释,在此同样适用,不再一一赘述。应该理解的是,这里仅描述的与本技术技术最相关的存储器的结构,其他结构可以如前述图1至图6所示的结构,也可以是其他存储器的结构。

173.基于相同的发明构思,本技术实施例还提供一种存储系统,所述存储系统包括:一个或多个前述所述的存储器;

174.以及耦合在所述存储器的存储器控制器;所述存储器控制器,用于:向所述存储器发送各种操作命令。所说的各种操作命令,比如,读取、编程、擦除等命令。

175.在一些实施例中,所述存储系统是固态硬盘ssd或存储卡。

176.需要说明的是,该存储系统包含前述的存储器,因此,二者具有相同的技术特征,该存储系统中出现的名词在前述的存储器中均以详细解释,在此同样适用,不再一一赘述。应该理解的是,这里仅描述的与本技术技术最相关的存储系统的结构,其他结构可以如前述图1至图6所示的结构,也可以是其他存储系统的结构。

177.以上所述仅为本技术的较佳实施例而已,并非用于限定本技术的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1