包括合并写入驱动器的存储器件的制作方法

实施例涉及一种包括合并写入驱动器的存储器件。

背景技术:

1、半导体存储器件被分类为易失性存储器件(例如,静态随机存取存储器(sram)或动态随机存取存储器(dram))或非易失性存储器件(例如,闪存器件、相变ram(pram)、磁ram(mram)、电阻ram(rram)或铁电ram(fram)),在易失性存储器件中,当电源关闭时,存储的数据消失,在非易失性存储器件中,即使在电源关闭时,也可以保留存储的数据。

技术实现思路

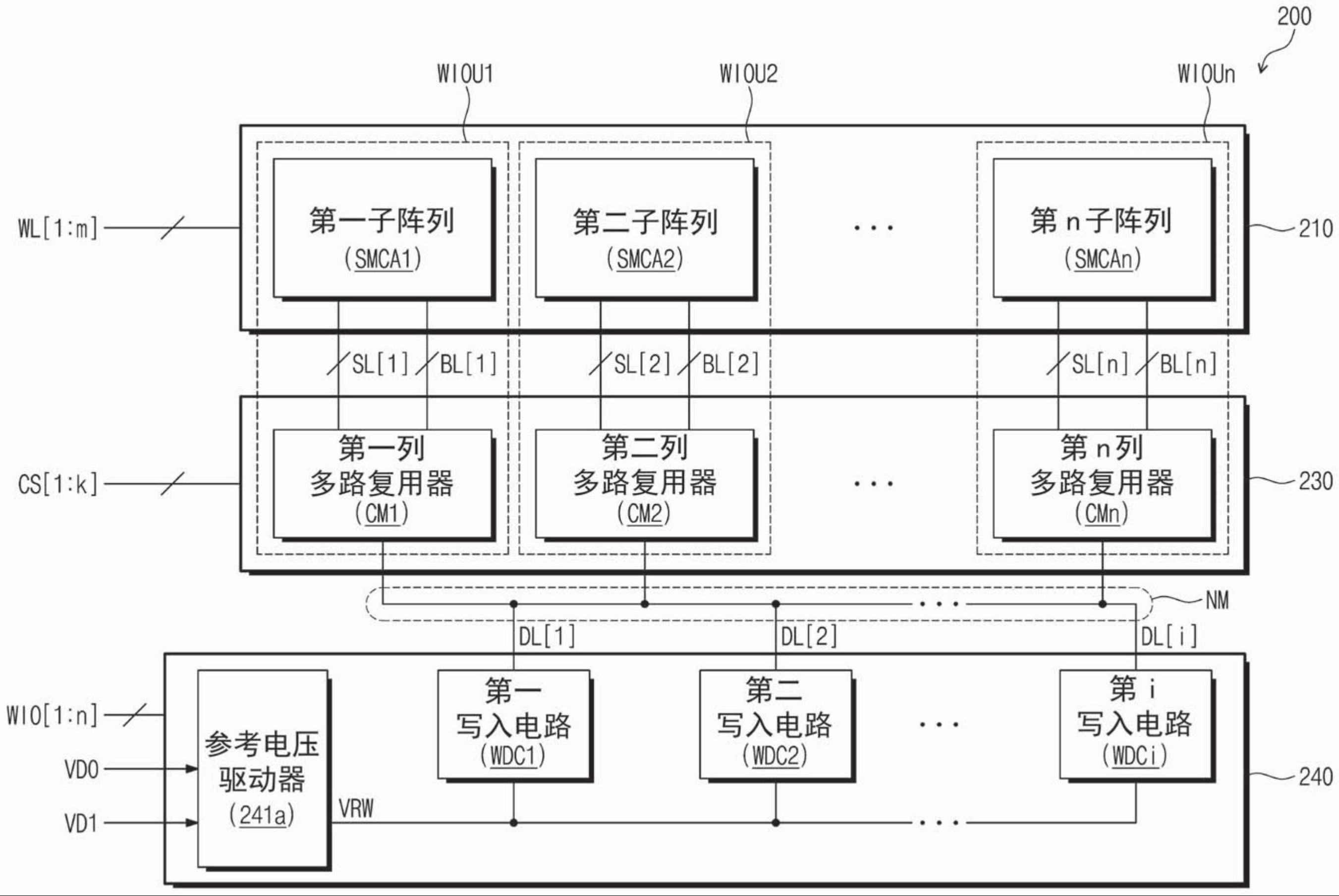

1、根据实施例,一种存储器件可以包括:存储器单元阵列,包括第一子存储器单元阵列和第二子存储器单元阵列,第一子存储器单元阵列包括第一存储器单元,第二子存储器单元阵列包括第二存储器单元;合并写入驱动器,包括第一写入电路,该第一写入电路通过写入输入/输出线接收n比特数据(n是2或更大的自然数)、响应于n比特数据中的第一数据比特将第一写入电压输出到合并节点、以及响应于n比特数据中的第二数据比特将第二写入电压输出到合并节点;以及列解码器,包括第一列多路复用器和第二列多路复用器,第一列多路复用器将合并节点的与第一数据比特相对应的第一电压施加到第一存储器单元,第二列多路复用器将合并节点的与第二数据比特相对应的第二电压施加到第二存储器单元。

2、根据实施例,一种存储器件可以包括:存储器单元阵列,包括第一子存储器单元阵列和第二子存储器单元阵列,第一子存储器单元阵列包括第一存储器单元,第二子存储器单元阵列包括第二存储器单元;列解码器,包括第一列多路复用器和第二列多路复用器,第一列多路复用器将第一合并节点的与第一值相对应的第一电压或第二合并节点的与第二值相对应的第二电压施加到第一存储器单元,第二列多路复用器将第一合并节点的与第一值相对应的第一电压或第二合并节点的与第二值相对应的第二电压施加到第二存储器单元;以及合并写入驱动器,通过写入输入/输出线接收“n个”数据比特(n是2或更大的自然数),并且响应于n比特数据向列解码器提供第一电压或第二电压。合并写入驱动器可以包括:第一写入电路,每个第一写入电路响应于“n个”数据比特中的与第一值相对应的第一数据比特将第一写入电压输出到第一合并节点;以及第二写入电路,每个第二写入电路响应于“n个”数据比特中的与第二值相对应的第二数据比特将第二写入电压输出到第二合并节点。

3、根据实施例,一种存储器件可以包括:存储器单元阵列,包括第一子存储器单元阵列和第二子存储器单元阵列,第一子存储器单元阵列包括第一存储器单元,第二子存储器单元阵列包括第二存储器单元;列解码器,包括第一列多路复用器和第二列多路复用器,第一列多路复用器向第一存储器单元提供与第一值相对应的第一电流或第一合并节点的与第二值相对应的第一电压,第二列多路复用器向第二存储器单元提供与第一值相对应的第二电流或第一合并节点的与第二值相对应的第一电压;以及合并写入驱动器,通过写入输入/输出线接收“n个”数据比特(n为2或更大的自然数),并且响应于n比特数据向列解码器提供第一电流、第二电流或第一电压。合并写入驱动器可以包括:第一电流写入电路,响应于“n个”数据比特中的与第一值相对应的第一数据比特向第一列多路复用器提供第一电流;第二电流写入电路,响应于“n个”数据比特中的与第一值相对应的第二数据比特将向第二列多路复用器提供第二电流;以及第二写入电路,响应于“n个”数据比特中的与第二值相对应的第三数据比特将写入电压输出到第二合并节点。

技术特征:

1.一种存储器件,包括:

2.根据权利要求1所述的存储器件,其中,所述第一存储器单元和所述第二存储器单元中的每一个包括:

3.根据权利要求1所述的存储器件,其中,所述合并写入驱动器还包括:第二写入电路,被配置为通过所述写入输入/输出线接收所述n比特数据,响应于所述第一数据比特将第三写入电压输出到所述合并节点,以及响应于所述第二数据比特将第四写入电压输出到所述合并节点。

4.根据权利要求3所述的存储器件,其中:

5.根据权利要求1所述的存储器件,其中,所述合并写入驱动器还包括:参考电压驱动器,被配置为接收第一驱动电压或第二驱动电压,并基于所述第一驱动电压或所述第二驱动电压生成参考写入电压。

6.根据权利要求5所述的存储器件,其中:

7.根据权利要求6所述的存储器件,其中:

8.根据权利要求6所述的存储器件,其中:

9.根据权利要求6所述的存储器件,其中,所述第一写入电路包括:

10.根据权利要求9所述的存储器件,其中:

11.根据权利要求9所述的存储器件,其中:

12.根据权利要求11所述的存储器件,其中:

13.根据权利要求1所述的存储器件,还包括测试开关,所述测试开关被配置为响应于测试控制信号向所述合并节点提供外部测试电压。

14.根据权利要求1所述的存储器件,其中,当所述第一数据比特的逻辑值与所述第二数据比特的逻辑值不同时,执行写入操作,使得用于写入所述第一数据比特的第一写入周期和用于写入所述第二数据比特的第二写入周期彼此不重叠。

15.一种存储器件,包括:

16.根据权利要求15所述的存储器件,其中,所述第一存储器单元和所述第二存储器单元中的每一个包括:

17.根据权利要求15所述的存储器件,其中:

18.根据权利要求15所述的存储器件,其中:

19.根据权利要求15所述的存储器件,还包括:

20.一种存储器件,包括:

技术总结

一种存储器件,包括:存储器单元阵列,包括第一子存储器单元阵列和第二子存储器单元阵列,第一子存储器单元阵列包括第一存储器单元,第二子存储器单元阵列包括第二存储器单元;合并写入驱动器,包括第一写入电路,该第一写入电路通过写入输入/输出线接收n比特数据,响应于n比特数据中的第一数据比特将第一写入电压输出到合并节点,以及响应于n比特数据中的第二数据比特将第二写入电压输出到合并节点;以及列解码器,包括第一列多路复用器和第二列多路复用器,第一列多路复用器将合并节点的与第一数据比特相对应的第一电压施加到第一存储器单元,第二列多路复用器将合并节点的与第二数据比特相对应的第二电压施加到第二存储器单元。

技术研发人员:姜圭成,郑铉泽

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!