一种延迟锁相环和存储器的制作方法

本公开涉及半导体存储器,尤其涉及一种延迟锁相环和存储器。

背景技术:

1、在动态随机存取存储器(dynamic random access memory,dram)中,延迟锁相环需要利用延迟线对四相位时钟信号(即4个相位依次相差90度的时钟信号)进行传输,以便后续完成数据采样操作。然而,在延迟锁相环的工作过程中,需要对延迟线的工作参数进行调节和锁定,这一时间影响存储器的整体性能。

技术实现思路

1、本公开提供了一种延迟锁相环和存储器,能够减少延迟锁相环的锁定时间。

2、本公开的技术方案是这样实现的:

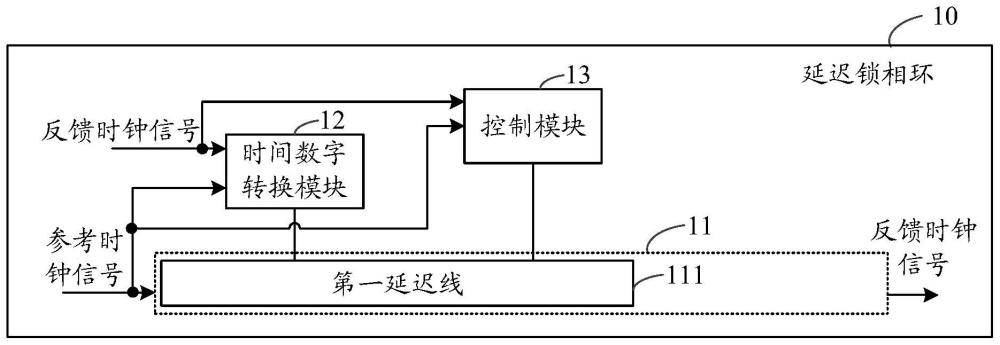

3、第一方面,本公开实施例提供了一种延迟锁相环,所述延迟锁相环包括:

4、第一信号路径,包括第一延迟线,配置为接收参考时钟信号,并对所述参考时钟信号进行延迟及调整处理,输出反馈时钟信号;其中,所述第一延迟线的延迟参数受到粗调控制码和细调控制码的控制;

5、时间数字转换模块,与所述第一信号路径连接,配置为检测所述参考时钟信号和所述反馈时钟信号之间的相位差,并将所述相位差转化为第一控制码;其中,所述第一控制码用于指示所述粗调控制码的初始值;

6、控制模块,与所述第一信号路径连接,配置为基于所述参考时钟信号和所述反馈时钟信号之间的相位差,对所述粗调控制码或所述细调控制码进行调整,直至所述参考时钟信号和所述反馈时钟信号处于对齐状态。

7、在一些实施例中,所述第一信号路径还包括传输延迟模拟模块;其中,

8、所述第一延迟线,配置为接收所述参考时钟信号,并对所述参考时钟信号进行延迟及调整处理,输出第一目标信号;

9、所述传输延迟模拟模块,与所述第一延迟线连接,配置为对所述第一目标信号进行传输路径延迟模拟处理,输出所述反馈时钟信号。

10、在一些实施例中,所述第一延迟线包括:

11、粗调延迟模块,配置为接收所述粗调控制码和所述参考时钟信号,基于所述粗调控制码对所述参考时钟信号进行延迟处理,输出第一中间信号;

12、细调延迟模块,与所述粗调延迟模块连接,配置为接收所述细调控制码和所述第一中间信号,基于所述细调控制码对所述第一中间信号进行延迟处理,输出第二中间信号;

13、占空比模块,与所述细调延迟模块连接,配置为对所述第二中间信号进行占空比调节处理,输出所述第一目标信号。

14、在一些实施例中,所述延迟锁相环还包括粗调参数生成模块;其中,

15、所述时间数字转换模块,具体配置为在所述参考时钟信号和所述反馈时钟信号之间的相位差大于第一阈值的情况下,将所述相位差转化为第一控制码并退出工作状态;在所述相位差小于等于第一阈值的情况下,直接退出工作状态;

16、所述粗调参数生成模块,与所述时间数字转换模块连接,配置为基于所述第一控制码,生成并输出所述粗调控制码。

17、在一些实施例中,所述控制模块,具体配置为若所述参考时钟信号和所述反馈时钟信号之间的相位差大于第一阈值,则输出第二控制码;以及对所述第二控制码进行调整,直至所述相位差小于等于第一阈值;

18、所述粗调参数生成模块,还与所述控制模块连接,还配置为接收所述第二控制码,并基于所述第二控制码,对所述粗调控制码进行更新。

19、在一些实施例中,所述延迟锁相环还包括细调参数生成模块;其中,

20、所述控制模块,还配置为若所述参考时钟信号和所述反馈时钟信号之间的相位差小于等于第一阈值,则输出第三控制码;以及对所述第三控制码进行调整,直至所述参考时钟信号和所述反馈时钟信号处于对齐状态;

21、所述细调参数生成模块,与所述控制模块连接,配置为接收所述第三控制码,并基于所述第三控制码,生成并输出所述细调控制码。

22、在一些实施例中,所述粗调参数生成模块包括:

23、代码产生模块,配置为接收加载指示信号、所述第一控制码和所述第二控制码;在所述加载指示信号处于第一电平状态的情况下,将所述第一控制码转换为中间控制码;在所述加载指示信号处于第二电平状态的情况下,将所述第二控制码转换为所述中间控制码;其中,所述加载指示信号指示所述时间数字转换模块是否退出工作状态;

24、译码模块,与所述代码产生模块连接,配置为接收所述中间控制码,将所述中间控制码映射为所述粗调控制码。

25、在一些实施例中,所述控制模块包括:

26、相位检测模块,与所述第一信号路径连接,配置为对所述参考时钟信号和所述反馈时钟信号进行相位检测,输出调整指示信号;

27、调整模块,与所述相位检测模块连接,配置为产生所述第二控制码或者第三控制码;以及基于所述调整指示信号对所述第二控制码或者所述第三控制码进行调整,且所述调整指示信号指示调整的方向。

28、在一些实施例中,所述时间数字转换模块包括:

29、检测模块,与所述第一信号路径连接,配置为在所述参考时钟信号和所述反馈时钟信号之间的相位差大于第一阈值的情况下,输出第一指示信号和第二指示信号;其中,所述第一指示信号中存在一个电平变化沿,且所述电平变化沿与所述参考时钟信号的上升沿对齐;所述第二指示信号存在一个电平变化沿,且所述电平变化沿与所述反馈时钟信号的上升沿对齐;

30、转换模块,与所述检测模块连接,配置为基于所述第一指示信号和所述第二指示信号,输出所述第一控制码。

31、在一些实施例中,所述检测模块包括:

32、判断模块,与所述第一信号路径连接,配置为在所述参考时钟信号和所述反馈时钟信号之间的相位差大于第一阈值的情况下,输出处于有效状态的工作指示信号;在所述相位差小于等于第一阈值的情况下,输出处于无效状态的工作指示信号;

33、第一截取模块,与所述判断模块连接,配置为接收所述工作指示信号和所述参考时钟信号,并在所述工作指示信号为有效状态的情况下,对所述参考时钟信号进行上升沿截取处理,输出所述第一指示信号;

34、第二截取模块,与所述判断模块和所述第一信号路径连接,配置为接收所述工作指示信号和所述反馈时钟信号,并在所述工作指示信号为有效状态的情况下,对所述反馈时钟信号进行上升沿截取处理,输出所述第二指示信号。

35、在一些实施例中,所述判断模块包括第一与门、第二与门、比较单元、第一触发器、第一非门;其中,

36、所述第一与门的第一输入端接收所述参考时钟信号,所述第二与门的第一输入端接收所述反馈时钟信号,所述第一与门的第二输入端和所述第二与门的第二输入端均接收第一使能信号;

37、所述比较单元的第一输入端与所述第一与门的输出端连接,所述比较单元的第二输入端与所述第二与门的输出端连接,所述比较单元的输出端输出相位比较信号,且所述相位比较信号指示所述参考时钟信号和所述反馈时钟信号之间的相位差是否大于第一阈值;

38、所述第一触发器的输入端接收所述相位比较信号,所述第一触发器的时钟端接收第一控制信号;所述第一触发器的正相输出端与所述第一非门的输入端连接,所述第一非门的输出端用于输出所述工作指示信号;

39、其中,所述第一使能信号指示所述时间数字转换模块是否处于工作状态,且所述工作状态包括初始化阶段和计算阶段;所述第一控制信号的电平变化沿指示所述时间数字转换模块进入计算阶段的时刻。

40、在一些实施例中,所述第二截取模块包括第三与门、第二触发器、第三触发器、第四触发器、第五触发器;

41、所述第三与门的第一输入端接收所述反馈时钟信号,所述第三与门的第二输入端接收所述工作指示信号;

42、所述第三与门的输出端与所述第二触发器的时钟端、第三触发器的时钟端、第四触发器的时钟端、第五触发器的时钟端均连接,所述第二触发器的输入端接收第一复位信号,所述第三触发器的输入端与所述第二触发器的正相输出端连接,所述第四触发器的输入端与所述第三触发器的正相输出端连接,所述第五触发器的输入端与所述第四触发器的正相输出端连接,所述第五触发器的正相输出端输出所述第二指示信号;

43、其中,所述第一复位信号指示所述时间数字转换模块进行复位。

44、在一些实施例中,所述第一截取模块包括第四与门和第六触发器;其中,所述第四与门的第一输入端接收所述参考时钟信号,所述第四与门的第二输入端接收所述工作指示信号,所述第四与门的输出端与所述第六触发器的时钟端连接,所述第六触发器的输入端与所述第五触发器的反相输出端连接,所述第六触发器的正相输出端用于输出所述第一指示信号。

45、在一些实施例中,所述检测模块还包括第二非门;所述第二非门的输入端接收第二复位信号,所述第二非门的输出端与所述第一触发器的置位端、所述第二触发器的复位端、所述第三触发器的复位端、所述第四触发器的复位端、所述第五触发器的复位端、所述第六触发器的置位端连接;

46、其中,所述第二复位信号指示所述延迟锁相环在所述时间数字转换模块进入初始化阶段之前完成复位或置位操作。

47、在一些实施例中,所述延迟锁相环还包括时钟处理模块和多个第二延迟线,所述时钟处理模块与所述第一延迟线、多个所述第二延迟线均连接,且每个所述第二延迟线的延迟参数均受到所述粗调控制码和所述细调控制码的控制;其中,

48、所述时钟处理模块,配置为接收初始时钟信号,基于所述初始时钟信号,输出多个分相时钟信号;其中,所述参考时钟信号是其中一个所述分相时钟信号;

49、所述第二延迟线,配置为接收一个所述分相时钟信号,对所接收的分相时钟信号进行延迟及调整处理,输出一个目标时钟信号;其中,所述目标时钟信号经过传输后用于数据采样操作。

50、第二方面,本公开实施例提供了一种存储器,所述存储器包括如第一方面所述的延迟锁相环。

51、本公开实施例提供了一种延迟锁相环和存储器,在延迟锁相环的工作过程中,先通过时间数字转换模块为粗调控制码提供一个合适的初始值,然后控制模块在此基础上继续调整粗调控制码和/或细调控制码,加快调整速度且缩短调整时间,延迟锁相环的锁定速度更快,性能提高。

- 还没有人留言评论。精彩留言会获得点赞!