控制电路及存储器的制作方法

本公开涉及集成电路领域,特别是涉及一种控制电路、方法及存储器。

背景技术:

1、动态随机存取存储器(dynamic random access memory,dram)是计算机中常用的半导体存储器件,由多个呈多行多列的存储单元及多个呈多行多列的灵敏放大器组成。现有的一种存储器如图1所示,若干行存储单元和一行灵敏放大器构成一个存储区域,存储器包括存储器阵列(未标示出)、行控制电路2’和列一码电路3’,存储器阵列包括多个存储区域1,行控制电路2’和列一码电路3’均与全部存储区域相连接。图1中以存储器中包括64各存储区域作为示例。

2、图1中行控制电路2’向各存储区域输出图2中的array(存储器阵列)位置sa(灵敏放大器)开启时间信号以打开对应的灵敏放大器对存储单元的数据进行放大,由于行控制电路2’位于存储阵列的顶部附近,其产生的array位置sa开启时间信号自存储器阵列的存储区域1向存储区域64方向传输(自上向下传输),array位置sa开启时间信号到达存储区域1的时间为图2中array位置sa开启时间的t1’时刻,array位置sa开启时间信号到达存储区域64的时间为图2中array位置sa开启时间的t1”。列译码电路3’向各存储区域输出图2中的array位置读/写信号以对执行数据放大操作的灵敏放大器执行读/写操作,array位置读信号自存储器阵列的存储区域64向存储区域1方向传输(自下向上传输),array位置读信号到达存储区域1的时间为图2中的array位置读信号的t2”,array位置读信号到达存储区域64的时间为图2中的array位置读/写信号的t2’。由此可知,array位置sa开启时间信号到达存储区域64的路径相较于array位置读信号到达存储区域64的路径多了63个存储区域的间距,从灵敏放大器开启到从灵敏放大器读/写数据的时间(t2’-t1”)过短,会导致存储区域64中的灵敏放大器还没有完全被放大,存储区域64中的存储单元通过灵敏放大器放大的数据就开始执行读操作,从而很容易导致读操作出现错误。

3、在对动态随机存储器进行测试的测试阶段,采用目前的测试电路进行测试存在在测试到有失效的存储单元时,无法确认测试到的失效是由于灵敏放大器未完全打开导致的失误,还是存储单元本身的失效而导致的测试失效,会导致测试失效误判断,不利于数据分析,不利于准确选出动态随机存储器中存在制造缺陷的点。

技术实现思路

1、基于此,有必要针对上述背景技术中的技术问题提供一种控制电路及存储器,能够在测试阶段,基于模式信号可以选择所需的读/写操作指令执行读/写操作,从而可以确保测试的准确性,能够在测试到失效时准确筛选出动态随机存储器中存在的制造缺陷点。

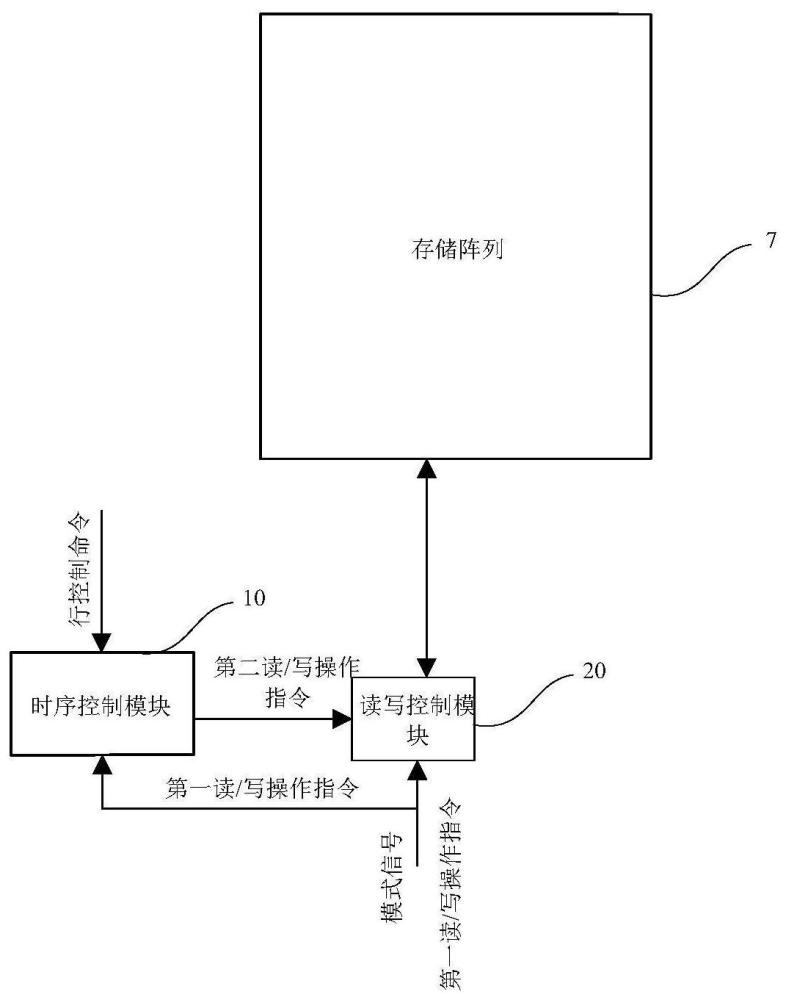

2、在第一方面,本公开提供一种控制电路,包括:

3、时序控制模块,用于接收行控制命令和第一读/写操作指令,并响应于所述第一读/写操作指令,基于所述行控制命令对应的存储单元位置信息生成第二读/写操作指令;

4、读写控制模块,用于接收所述模式信号、第一读/写操作指令和所述第二读/写操作指令,基于模式信号的控制选择所述第一读/写操作指令或所述第二读/写操作指令,并根据选取的所述第一读/写操作指令执行对应的第一读/写操作,或根据选取的所述第二读/写操作指令执行对应的第二读/写操作。

5、可选地,所述行控制命令包括灵敏放大器开启指令及对应的行地址,所述基于所述行控制命令对应的存储单元位置信息生成第二读/写操作指令,包括:基于所述行控制命令中的行地址对所述灵敏放大器开启指令进行时序偏差补偿,并基于时序偏差补偿调整后的灵敏放大器开启指令生成所述第二读/写操作指令。

6、可选地,所述第一读/写操作指令有效时,基于所述行控制命令对应的存储单元位置信息生成所述第二读/写操作指令,所述第一读/写操作指令无效时,不生成所述第二读/写操作指令。

7、可选地,所述行控制命令包括行控制逻辑指令及行地址,所述行控制逻辑指令包括灵敏放大器开启指令;所述时序控制模块包括:

8、接收模块,用于接收所述行控制命令及所述第一读/写操作指令,并根据所述第一读/写操作指令生成使能信号;

9、偏差调整模块,与所述接收模块相连接,用于接收所述使能信号,在所述使能信号的控制下,接收所述行控制命令,并根据所述行控制命令中的行地址对应的存储单元位置信息,对所述灵敏放大器开启指令进行时序偏差补偿,生成灵敏放大器开启调整信号;

10、读写时序调整模块,与所述偏差调整模块连接,接收所述灵敏放大器开启调整信号,生成与所述灵敏放大器开启调整信号具有第一预设时间间隔的读/写时序控制信号;

11、信号生成模块,与所述读写时序调整模块相连接,用于基于所述读/写时序控制信号生成所述第二读/写操作指令。

12、可选地,所述读写时序调整模块,还用于在外部测试信号的控制下,调整第一预设时间间隔的长度。

13、可选地,所述时序控制模块还用于接收所述第一读/写操作指令对应的列地址,在所述第一读/写操作指令的控制下,基于所述行地址和所述列地址对所述灵敏放大器开启指令进行时序偏差补偿。

14、可选地,所述时序控制模块包括:

15、接收模块,用于接收所述第一读/写操作指令,并根据所述第一读/写操作指令生成使能信号;

16、偏差调整模块,与所述接收模块相连接,接收所述使能信号,在所述使能信号的控制下,接收所述行控制命令及所述第一读/写操作指令对应的列地址,并基于所述行地址和所述列地址对应的存储单元位置信息,对所述灵敏放大器开启指令进行时序偏差补偿,生成灵敏放大器开启调整信号;

17、读写时序调整模块,与所述偏差调整模块连接,接收所述灵敏放大器开启调整信号,生成与所述灵敏放大器开启调整信号具有第一预设时间间隔的读/写时序控制信号;

18、信号生成模块,与所述读写时序调整模块相连接,用于基于所述读/写时序控制信号生成所述第二读/写操作指令。

19、可选地,所述读写时序调整模块,还用于在外部测试信号的控制下,调整第一预设时间间隔的长度。

20、可选地,所述读写控制模块包括:

21、选择单元,用于接收所述模式信号、所述第一读/写操作指令及所述第二读/写操作指令,并根据所述模式信号的控制,选择并输出所述第一读/写操作指令或所述第二读/写操作指令;

22、列地址锁存单元,用于锁存所述第一读/写操作指令对应的列地址;

23、读写控制单元,与所述选择单元和所述列地址锁存单元连接,用于根据从选择单元接收的所述第一读/写操作指令对接收到的所述列地址对应的存储单元执行第一读/写操作,或根据从选择单元接收的所述第二读/写操作指令对接收到的所述列地址对应的存储单元执行第二读/写操作;

24、比较单元,用于在测试模式下获取所述第一读/写操作指令和所述第二读写指令命令信号之间的时间差,并输出所述时间差。

25、可选地,所述读写控制单元基于所述第一读/写操作指令或所述第二读/写操作指令生成列控制逻辑指令,并基于所述列控制逻辑指令执行所述第一读/写操作指令或所述第二读/写操作;其中,所述列控制逻辑指令包括列地址译码控制信号、本地读写转换控制信号、第二级放大器控制信号以及写入驱动控制信号。

26、可选地,还包括:

27、列译码电路,与所述读写控制模块相连接,用于接收所述列地址译码控制信号和所述列地址,并根据所述列地址译码控制信号生成列选通信号,响应于所述列选通信号,控制所述列地址对应的灵敏放大器和本地数据线之间的数据传输;

28、读写转换电路,与所述读写控制模块相连接,用于接收所述本地读写转换控制信号,响应于所述本地读写转换控制信号,将本地数据线上的数据读出至全局数据线或者将全局数据线的数据写入至本地数据线;

29、读写电路,与所述读写控制模块相连接,用于接收所述第二级放大器控制信号和所述写入驱动控制信号,并根据所述第二级放大器控制信号执行数据读出操作以及根据所述写入驱动控制信号执行数据写入操作。

30、可选地,所述读写电路包括:

31、读放大电路,与所述读写控制模块相连接,响应于接收到的第二级放大器控制信号,将全局数据线中的数据放大并读出;

32、写驱动电路,与所述读写控制模块相连接,响应于接收到的写入驱动控制信号,将总线中的数据写入至全局数据线。

33、可选地,还包括:

34、行控制逻辑模块,用于接收激活操作命令和对应的行地址,并根据所述激活操作命令生成行控制逻辑指令,并基于所述行控制逻辑指令生成传输至所述时序控制模块的所述行控制命令,其中,所述行控制命令包括灵敏放大器开启调整信号和所述行地址。

35、可选地,所述行控制逻辑指令包括:行地址译码指令、预充电指令以及所述灵敏放大器开启指令。

36、可选地,还包括:

37、行控制电路,用于接收行控制逻辑指令和所述行地址,并根据所述行控制逻辑指令对所述行地址对应的存储单元执行对应的行操作。

38、可选地,所述行控制电路包括:

39、行译码电路,用于接收行译码指令和所述行地址,响应于所述行译码指令,控制所述行地址对应的字线打开;

40、灵敏放大器控制电路,用于接收灵敏放大器开启指令,响应于所述灵敏放大器开启指令,控制所述行地址对应的灵敏放大器执行感测放大操作。

41、可选地,所述行控制逻辑模块,还用于根据所述行地址,产生时序控制选择信号;

42、所述时序控制模块包括第一时序控制模块和第二时序控制模块,所述第一时序控制模块和所述第二时序控制模块均连接所述行控制逻辑模块,用于接收所述时序控制选择信号、行控制命令和所述第一读/写操作指令,并响应于所述时序控制选择信号,使能所述第一时序控制模块或所述第二时序控制模块,以生成第二读/写操作指令;

43、所述读写控制模块包括第一读写控制模块和第二读写控制模块,所述第一读写控制模块与所述第一时序控制模块连接,所述第二读写控制模块与所述第二时序控制模块连接,所述第一读写控制模块和所述第二读写控制模块分别用于控制不同的存储区域执行读/写操作。

44、可选地,所述控制电路还包括:

45、列译码电路,所述列译码电路包括第一列译码电路和第二列译码电路,所述第一列译码电路与所述第一读写控制模块连接,所述第二列译码电路与所述第二读写控制模块连接;

46、所述第一读写控制模块控制所述第一列译码电路对第一存储区域中的存储单元执行读/写操作,所述第二读写控制模块控制所述第二列译码电路对第一存储区域中的存储单元执行读/写操作。

47、在第二方面,本技术还提供一种存储器,包括如第一方案中所述的控制电路。

48、在第三方面,本技术还提供一种存储器,包括:

49、多个存储单元阵列,呈多行多列间隔排布;每个存储单元阵列均包括多个呈多行多列排布的存储单元;

50、多个灵敏放大器阵列,呈多行多列间隔排布;所述灵敏放大器阵列与所述存储单元阵列沿列方向交替间隔排布,所述灵敏放大器阵列与位于其两侧的所述存储单元阵列相连接;每个所述灵敏放大器阵列包括多个呈至少一行排布的灵敏放大器;

51、行控制电路,所述行控制电路经由字线与位于同一行的所述存储单元依次连接;

52、至少一个列译码电路,每个所述列译码电路经由列选通信号线与所述列译码电路对应的多个存储单元阵列中位于同一列的所述灵敏放大器依次连接;

53、如第一方面所述的控制电路;所述控制电路根据所述第一读/写操作指令或所述第二读/写操作指令控制所述列译码电路对所述存储单元阵列中的存储单元执行读/写操作。

54、可选地,存储器还包括:

55、多个读写转换电路,分别位于所述灵敏放大器阵列与所述行控制电路之间,与所述行控制电路相连接。

56、本公开的控制电路通过设置时序控制模块及读写控制模块,由于时序控制模块基于行控制命令对应的存储单元位置信息对第一读/写操作指令进行了时序调整而得到了第二读/写操作指令,当控制电路应用于存储器时,在对存储器进行测试时,可以基于模式信号在第一读/写操作指令和第二读/写操作指令二者中选择合适的读/写操作指令执行读/写操作,从而确保测试的准确性,在测试到有存储单元失效时,可以准确筛选出存在制造缺陷的位置。

- 还没有人留言评论。精彩留言会获得点赞!