灵敏放大电路及随机存储器的制作方法

本技术涉及存储,特别涉及一种灵敏放大电路及随机存储器。

背景技术:

1、随机存储器的存储阵列包括多条字线(wl,word line)、多对互补位线(bl/bl#,bit line)和多个存储单元,每个存储单元分别连接一条字线wl和一对互补位线对(bl/bl#)。

2、在对存储单元中的数据进行读写操作时,此时需要经过预充电阶段、电荷分享阶段、灵敏放大阶段及恢复阶段对存储单元中的数据进行读写操作,其中,电荷分享阶段非常重要,这是将存储单元中的数据取出的步骤的关键,电荷分享阶段目标位线是直接和访问单元交互的第一个过程,只有电荷分享阶段正确才能保证后续阶段有效进行。在现有技术的电荷分享阶段中,目标位线在与存储单元分享存储电荷时,灵敏放大模块中的晶体管会影响电荷分享阶段存储电荷的分享,从而影响电荷分享阶段的存储电荷读取的准确性。

技术实现思路

1、为了解决上述问题,本技术提供一种灵敏放大电路及随机存储器,能够使目标位线与存储单元的存储电荷分享更充分。

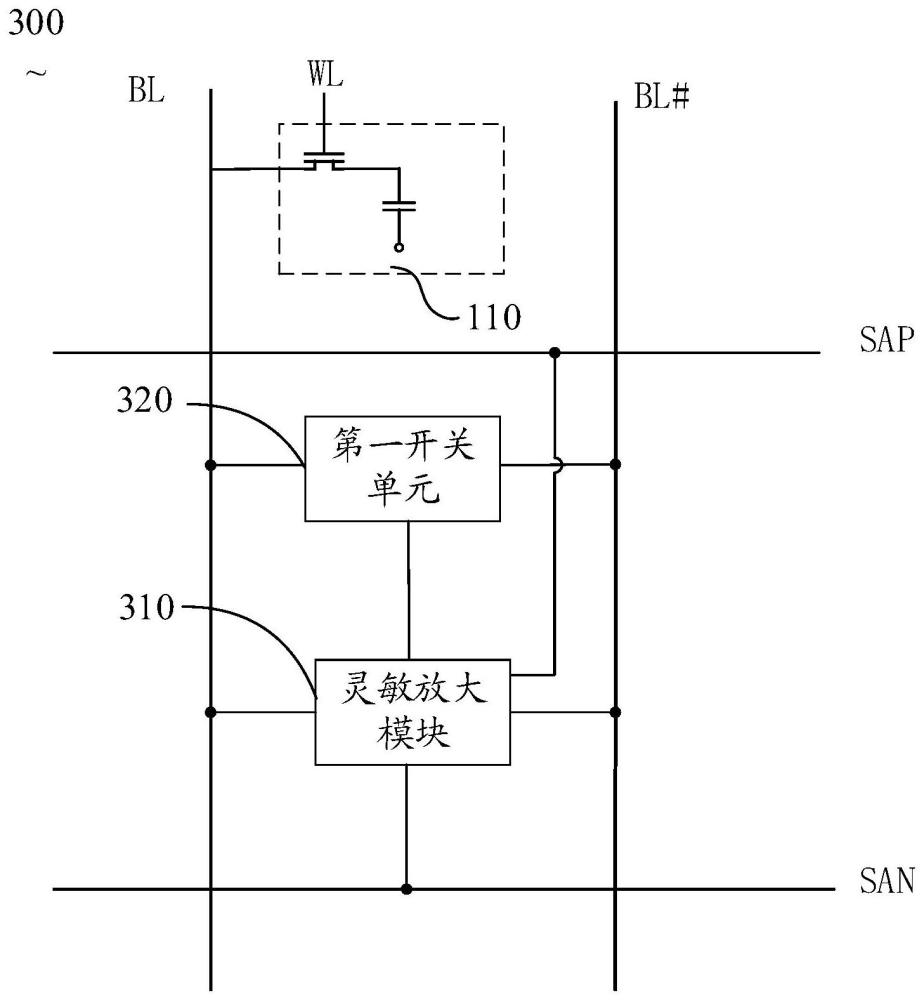

2、为解决上述技术问题,本技术采用的一个技术方案是:提供一种灵敏放大电路,该灵敏放大电路包括灵敏放大模块与第一开关单元,灵敏放大模块连接在目标位线与互补位线之间,并连接灵敏放大电压线,其中,在电荷分享阶段,目标位线分享对应开启的存储单元存储的存储电荷;在灵敏放大阶段,灵敏放大电压线被驱动至处于灵敏放大电压的状态,灵敏放大模块用于将分享了存储电荷的目标位线上的目标位线电压拉至灵敏放大电压;第一开关单元连接在目标位线与灵敏放大模块的至少一部分之间和互补位线与灵敏放大模块的至少另一部分之间;其中,在包括电荷分享阶段的至少部分的一目标时长内,第一开关单元截止,切断目标位线与灵敏放大模块的至少一部分之间的通路,以使目标位线分享存储电荷,避免灵敏放大模块的至少一部分在目标时长内分享存储电荷。

3、其中,灵敏放大电压线包括第一灵敏放大电压线和第二灵敏放大电压线,灵敏放大模块包括第一反相单元及第二反相单元,第一反相单元用于连接在目标位线与互补位线之间,并连接第一灵敏放大电压线和第二灵敏放大电压线;第二反相单元用于连接在互补位线与目标位线之间,并连接第一灵敏放大电压线和第二灵敏放大电压线,其中,第一反相单元的输出耦接第二反相单元的输入,第二反相单元的输出耦接第一反相单元的输入,其中第一开关单元还包括第一开关及第二开关,第一开关连接在目标位线与第一反相单元的输入之间;第二开关连接在互补位线与第二反相单元的输入之间,其中,在目标时长内,第一开关截止,切断目标位线与第一反相单元的输入之间的通路,和/或第二开关截止,切断互补位线与第二反相单元的输入之间的通路。

4、其中,在灵敏放大阶段,第一灵敏放大电压线被驱动至处于第一灵敏放大电压的状态,第二灵敏放大电压线被驱动至处于第二灵敏放大电压的状态,基于分享了所述存储电荷的所述目标位线上的目标位线电压,第一反相单元将互补位线上的互补位线电压拉至第一灵敏放大电压和第二灵敏放大电压之一者;在灵敏放大阶段,基于互补位线上被拉至的互补位线电压,第二反相单元将目标位线上的目标位线电压拉至第一灵敏放大电压和第二灵敏放大电压的另一者。

5、其中,第一反相单元包括第一晶体管及第二晶体管,第一晶体管,其控制端连接目标位线,其第一通路端连接第二灵敏放大电压线;第二晶体管,其控制端通过第一开关单元连接第一晶体管的控制端,其第一通路端连接第一灵敏放大电压线,其中,第一晶体管的第二通路端与第二晶体管的第二通路端通过第一连接线连接在一起;

6、第二反相单元包括第三晶体管及第四晶体管,第三晶体管,控制端连接互补位线,其第一通路端连接第二灵敏放大电压线;第四晶体管,其控制端通过第一开关单元连接第三晶体管的控制端,其第一通路端连接第一灵敏放大电压线,其中,第三晶体管的第二通路端与第四晶体管的第二通路端通过第二连接线连接在一起;其中,第一连接线用于连接第四晶体管的控制端,第二连接线用于连接第二晶体管的控制端。

7、其中,第一开关单元,包括第一开关及第二开关,第一开关连接在第二晶体管的控制端与第一晶体管的控制端之间;第二开关连接在第四晶体管的控制端与第三晶体管的控制端之间;在目标时长内,第一开关和第二开关截止,切断目标位线与第二晶体管的控制端之间的通路和互补位线与第四晶体管的控制端之间的通路,目标位线连接第一晶体管的控制端,互补位线连接第三晶体管的控制端,以避免第二晶体管的控制端通过目标位线分享存储电荷,使目标位线在目标时长内能够充分分享存储电荷。

8、其中,目标时长等于电荷分享阶段的时长的一部分或者电荷分享阶段的时长,第一开关单元中的第一开关和第二开关的导通起始时刻不晚于灵敏放大阶段的起始时刻。

9、其中,目标时长超过电荷分享阶段的时长,且第一开关单元的第一开关和第二开关的导通起始时刻晚于灵敏放大阶段的起始时刻,且不晚于灵敏放大电压线上的电压被驱动至灵敏放大电压对应的阈值电压的阈值时刻;第一灵敏放大电压线上的电压被驱动至第一灵敏放大电压对应的第一阈值电压的时刻,定义为第一阈值时刻;第二灵敏放大电压线上的电压被驱动至第二灵敏放大电压对应的第二阈值电压的时刻,定义为第二阈值时刻;阈值时刻为第一阈值时刻和第二阈值时刻中的较早者。

10、其中,调整后第一控制信号在目标时长内控制第一开关及第二开关截止,调整后第一控制信号是藉由一调整控制模块对原始第一控制信号的调整而产生,原始第一控制信号通过随机存储器中的控制逻辑模块产生;调整控制模块包括延迟链及多个可导通支路,延迟链包括多个串联在一起的延迟单元,其中,延迟链的第一端连接控制逻辑模块以接收原始第一控制信号,延迟链的第二端连接第一开关单元以输出调整后的第一控制信号;每个可导通支路分别与一个对应的延迟单元并联,且每个可导通支路上分别设置对应的档位开关,响应于对应的档位开关截止,对应的可导通支路非导通,对应的延迟单元处于工作状态;响应于对应的档位开关导通,对应的可导通支路导通,对应的延迟单元处于非工作状态;调整控制模块通过调制延迟链中处于工作状态的延迟单元的数量,对原始第一控制信号进行延迟调整,以产生调整后的第一控制信号。

11、其中,调整控制模块进一步包括多工解调单元,多工解调单元连接控制逻辑模块以接收第二控制信号并对第二控制信号进行多工解调,产生多个解调控制信号,其中,每个解调控制信号用于控制一个对应的档位开关。

12、其中,调整后第一控制信号在目标时长内控制第一开关及第二开关截止,调整后第一控制信号在电荷分享阶段的起始时刻截止第一开关和第二开关,调整后第一控制信号是藉由一调整控制模块通过随机存储器中的控制逻辑模块产生;

13、其中,调整控制模块包括:

14、第一比较器,其第一输入端连接第一灵敏放大电压线以接收第一灵敏放大电压线上的电压,其第二输入端接收第一灵敏放大电压对应的第一阈值电压,其中,当第一灵敏放大电压线上的电压大于第一阈值电压时,第一比较器输出第一触发数据;

15、第二比较器,其第一输入端连接第二灵敏放大电压线以接收第二灵敏放大电压线上的电压,其第二输入端接收第二灵敏放大电压对应的第二阈值电压,其中,当第二灵敏放大电压线上的电压小于第二阈值电压时,第二比较器输出第一触发数据;

16、第一逻辑门电路,连接第一比较器和第二比较器的输出端,响应于第一比较器和第二比较器之任一输出第一触发数据,第一逻辑门电路发出第二触发数据;

17、第一控制电路,其第一输入端接收第一逻辑门电路发出第二触发数据,其第二输入端接收第一开关的控制端的反相触发数据及第二开关的控制端的反相触发数据,其中,响应于第一逻辑门电路发出第二触发数据,导通第一开关及第二开关。

18、其中,灵敏放大电路进一步包括偏移消除模块,偏移消除模块包括第二开关单元,

19、第二开关单元包括:

20、第三开关,连接在第一晶体管的控制端与第一晶体管的第二通路端之间;

21、第四开关,连接在第三晶体管的控制端与第三晶体管的第二通路端之间;

22、其中,在偏移补偿阶段,第一开关和第二开关截止;

23、第三开关和第四开关导通,以使第一晶体管和第三晶体管分别等效于二极管连接,并藉由第一灵敏放大电压线和第二灵敏放大电压线的驱动能力,执行偏移消除操作;在电荷分享阶段和灵敏放大阶段,第三开关和第四开关截止。

24、其中,灵敏放大模块中第一连接线直接连接至第四晶体管的控制端;第二连接线直接连接至第二晶体管的控制端;或者

25、灵敏放大模块进一步包括第三开关单元,包括:

26、第五开关,连接在第一连接线与互补位线或者第四晶体管的控制端之间;

27、第六开关,连接在第二连接线与目标位线或者第二晶体管的控制端之间;在偏移补偿阶段、电荷分享阶段和灵敏放大阶段,第五开关和第六开关导通。

28、其中,偏移消除模块包括第四开关单元,包括:

29、第七开关,连接在第二晶体管的控制端与第二晶体管的第二通路端之间;

30、第八开关,连接在第四晶体管的控制端与第四晶体管的第二通路端之间;

31、其中,在偏移补偿阶段,第七开关和第八开关导通,以使第二晶体管和第四晶体管分别等效于二极管连接,并藉由第一灵敏放大电压线和第二灵敏放大电压线的驱动能力,执行偏移消除操作;在电荷分享阶段和灵敏放大阶段,第七开关和第八开关截止。

32、为解决上述技术问题,本技术采用的又一个技术方案是:提供一种随机存储器,该随机存储器包括如上述的灵敏放大电路。

33、本技术实施例的有益效果是:区别于现有技术,本技术通过在灵敏放大模块与目标位线及灵敏放大模块与互补位线之间设置第一开关单元,通过控制第一开关单元在包括电荷分享阶段的至少部分的一目标时长内截止,可以切断目标位线与灵敏放大模块的至少一部分之间的通路,以使目标位线在电荷分享阶段分享存储单元的存储电荷的同时,避免灵敏放大模块的至少一部分在所述目标时长内分享存储电荷,使得目标位线能够充分分享存储单元的存储电荷,能够使目标位线读取存储电荷的准确性提高,从而提高随机存储器的电路性能。

- 还没有人留言评论。精彩留言会获得点赞!