感测放大器布局设计以及相关设备和方法与流程

本公开大体上涉及感测放大器布局设计,且更具体来说,涉及包括与交叉耦合的晶体管对共享连续活性材料的感测放大器控制晶体管的感测放大器布局设计。

背景技术:

1、对越来越小的集成电路装置的需求促使半导体装置设计者在集成电路装置中使用最小的装置节距和间距。管控这些集成电路装置的设计标准的实体要求集成电路装置设计者满足各种需求。在许多情况下,这些需求可能是关于给定的集成电路装置可能有多小的限制因素。

技术实现思路

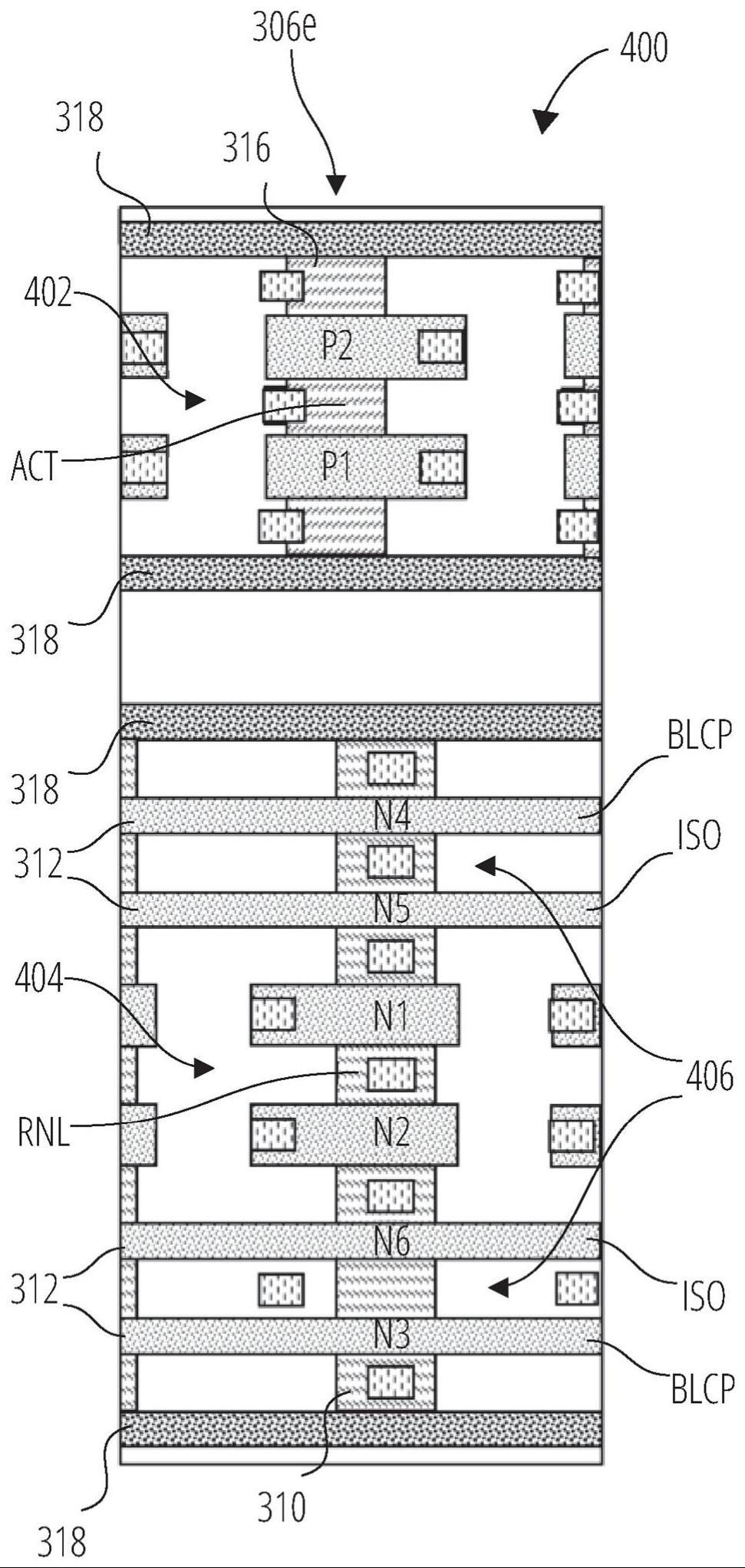

1、在一些实施例中,一种设备包含感测放大器的交叉耦合的上拉晶体管对、感测放大器的交叉耦合的下拉晶体管对、将交叉耦合的上拉晶体管对电连接到交叉耦合的下拉晶体管对的导电线对,以及与交叉耦合的上拉晶体管对或交叉耦合的下拉晶体管对中的一个共享连续活性材料的感测放大器控制晶体管。

2、在一些实施例中,操作感测放大器的方法包含通过断言感测放大器控制晶体管的共享控制栅极端子与交叉耦合的下拉晶体管对共享连续活性材料并且将预充电电压电势施加到导电线对,以此将位线对和导电线对预充电,所述导电线对将感测放大器的交叉耦合的上拉晶体管对电连接到感测放大器的交叉耦合的下拉晶体管对。所述方法还包含将存储器单元电连接到经预充电的位线对,并且放大通过存储器单元递送到位线对的电荷。

3、在一些实施例中,一种设备包含第一感测放大器和第二感测放大器。所述第一感测放大器包含第一交叉耦合的上拉晶体管对、第一交叉耦合的下拉晶体管对,以及与第一交叉耦合的下拉晶体管对共享第一连续活性材料的第一感测放大器控制晶体管集。所述第二感测放大器包含第二交叉耦合的上拉晶体管对、第二交叉耦合的下拉晶体管对,以及与第二交叉耦合的下拉晶体管对共享第二连续活性材料的第二感测放大器控制晶体管集。

技术特征:

1.一种设备,其包括:

2.根据权利要求1所述的设备,其中所述感测放大器控制晶体管与所述交叉耦合的下拉晶体管对共享所述连续活性材料。

3.根据权利要求1所述的设备,其中所述交叉耦合的上拉晶体管对和所述交叉耦合的下拉晶体管对是鳍式场效应晶体管finfet。

4.根据权利要求3所述的设备,其中:

5.根据权利要求1所述的设备,其中所述交叉耦合的上拉晶体管对共享共同鳍片。

6.根据权利要求1所述的设备,其中与其它感测放大器的其它感测放大器控制晶体管的其它控制栅极端子共享所述感测放大器控制晶体管的控制栅极端子的栅极材料线。

7.根据权利要求6所述的设备,其中所述感测放大器控制晶体管的所述控制栅极端子的所述栅极材料线至少以大致垂直于所述导电线对的方式延伸。

8.根据权利要求1所述的设备,其中所述导电线对至少以大致垂直于所述感测放大器电连接到的位线的方式延伸。

9.根据权利要求1所述的设备,其中所述导电线对至少以与所述连续活性材料基本平行的方式延伸。

10.根据权利要求1至9中任一权利要求所述的设备,其中所述交叉耦合的下拉晶体管对包含电连接到其它感测放大器的其它交叉耦合的下拉晶体管对的其它源极端子的源极端子。

11.根据权利要求1至9中任一权利要求所述的设备,其中所述交叉耦合的上拉晶体管对包含电连接到其它感测放大器的其它交叉耦合的上拉晶体管对的其它源极端子的源极端子。

12.根据权利要求1至9中任一权利要求所述的设备,其另外包括从预充电电压电势节点电连接到位线的预充电晶体管,所述位线电连接到所述感测放大器或电连接到所述导电线对中的一个。

13.一种操作感测放大器的方法,所述方法包括:

14.根据权利要求13所述的方法,其中将所述预充电电压电势施加到所述导电线对包括断言电连接于预充电电压电势节点与所述导电线对中的至少一个导电线之间的预充电晶体管的栅极端子。

15.根据权利要求14所述的方法,其中将所述预充电电压电势施加到所述导电线对包括:

16.一种设备,其包括:

17.根据权利要求16所述的设备,其中所述第一交叉耦合的上拉晶体管对的第一源极端子电连接到所述第二交叉耦合的上拉晶体管对的第二源极端子。

18.根据权利要求16所述的设备,其中所述第一交叉耦合的下拉晶体管对的第一源极端子电连接到所述第二交叉耦合的下拉晶体管对的第二源极端子。

19.根据权利要求16所述的设备,其中所述第一感测放大器控制晶体管集的第一栅极端子与所述第二感测放大器控制晶体管集的第二栅极端子共享共同栅极材料线。

20.根据权利要求16至19中任一权利要求所述的设备,其另外包括第三感测放大器,所述第三感测放大器包含:

技术总结

本申请案涉及感测放大器布局设计,以及相关设备和方法。一种设备包含感测放大器的交叉耦合的上拉晶体管对、所述感测放大器的交叉耦合的下拉晶体管对,以及将所述交叉耦合的上拉晶体管对电连接到所述交叉耦合的下拉晶体管对的导电线对。所述设备还包含与所述交叉耦合的上拉晶体管对或所述交叉耦合的下拉晶体管对中的一个共享连续活性材料的感测放大器控制晶体管。一种方法包含断言感测放大器控制晶体管的共享控制栅极端子与所述交叉耦合的下拉晶体管对共享连续活性材料;将预充电电压电势施加到所述导电线对;将存储器单元电连接到所述经预充电的位线对;和放大通过所述存储器单元递送到所述位线对的电荷。

技术研发人员:C·G·维迪维尔特,E·J·舒尔茨

受保护的技术使用者:美光科技公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!