存储装置及其操作方法与流程

发明构思涉及存储装置,并且更具体地,涉及包括映射存储器的存储装置及其操作方法。

背景技术:

1、由于近来半导体装置的集成的程度的提高,纠错电路(ecc)被嵌入半导体装置中作为防止存储器单元的故障并提高半导体装置的可靠性的方法。

2、为了提高半导体装置的可靠性,关于存储器单元的写入错误率(wer)可在半导体装置的制造阶段期间被检查和提高。然而,即使在制造阶段之后,也需要通过检查和提高wer来进一步提高半导体装置的可靠性。

技术实现思路

1、发明构思提供一种包括映射存储器的存储装置,以在制造阶段之后提高写入错误率(wer)。

2、发明构思还提供一种通过利用映射存储器和存储器装置二者来存储奇偶校验位以降低成本的存储装置。

3、发明构思的技术目标不限于以上提及的技术目标,并且本领域普通技术人员将从以下的描述中清楚地理解未提及的其他技术目标。

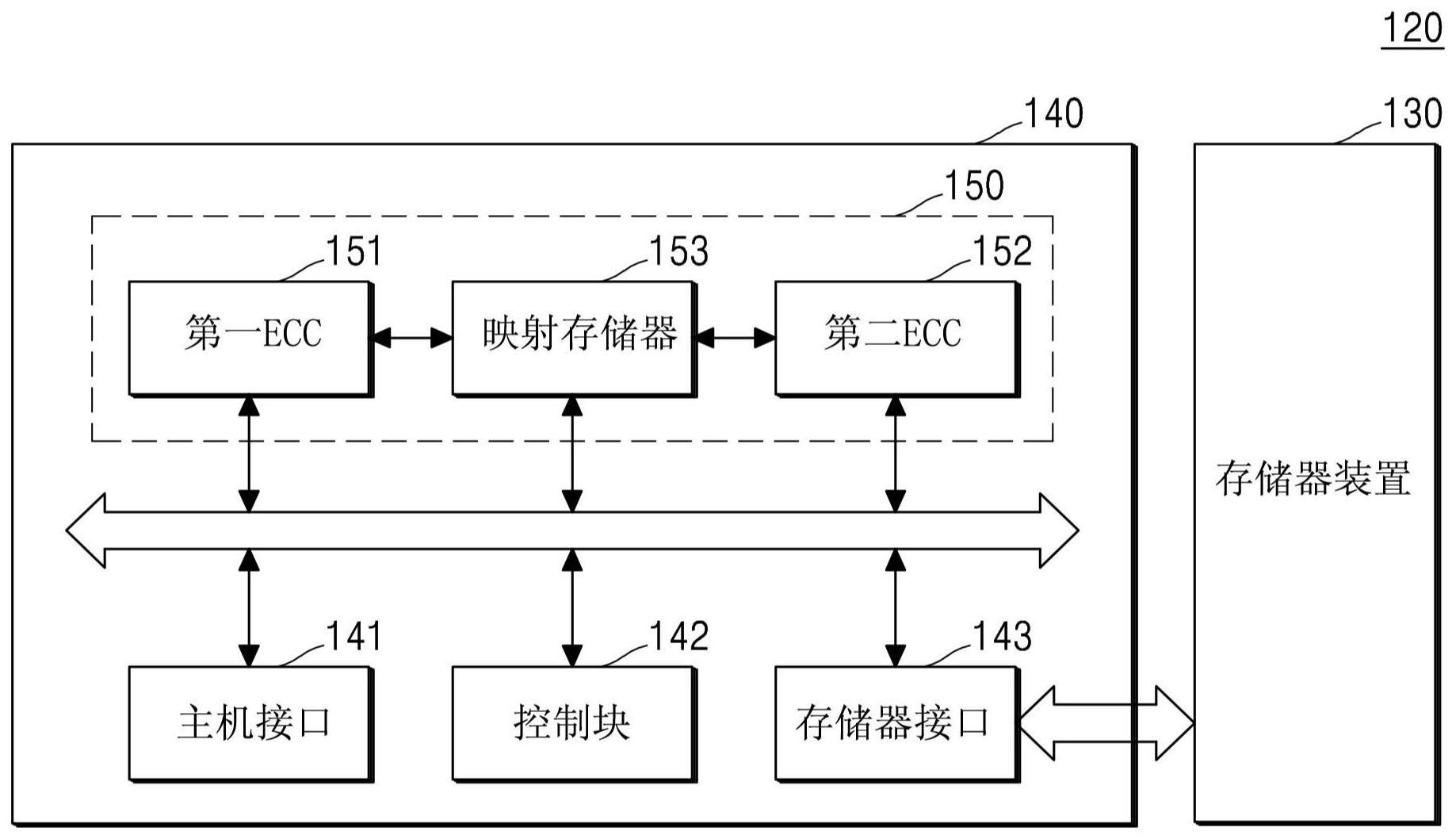

4、根据发明构思,提供一种存储装置,所述存储装置包括:存储器装置,被配置为存储原始数据;以及控制器,被配置为控制存储器装置,控制器包括:第一纠错电路,被配置为纠正原始数据的错误;第二纠错电路,被配置为纠正原始数据的错误,第二纠错电路的可纠正错误位的最大数量大于第一纠错电路的可纠正错误位的最大数量;映射存储器,被配置为存储由第二纠错电路生成的奇偶校验位中的至少一些,并且存储存储原始数据的存储器装置的地址;以及控制块,被配置为控制第一纠错电路、第二纠错电路和映射存储器。

5、根据发明构思,提供一种存储装置,所述存储装置包括:存储器装置,被配置为存储包括原始数据和原始数据的奇偶校验位的码字;以及纠错电路模块,被配置为通过对原始数据进行编码来生成所述码字,其中,纠错电路模块包括:第一纠错电路;第二纠错电路,比第一纠错电路具有更大的可纠正错误位的最大数量;以及映射存储器,被配置为存储由第二纠错电路生成的所述码字的一部分和存储原始数据的存储器装置的地址。

6、根据发明构思,提供一种操作存储装置的方法,所述方法包括:从所述存储装置的外部接收写入请求和原始数据,所述存储装置包括存储器装置;检查与写入请求对应的地址是否与存储在映射存储器中的地址相同;基于与写入请求对应的地址与存储在映射存储器中的地址不同,通过使用第一纠错电路对原始数据执行纠错编码来生成奇偶校验位;将原始数据和由第一纠错电路生成的奇偶校验位存储在存储器装置中;当与写入请求对应的地址与存储在映射存储器中的地址相同时,通过使用第二纠错电路对原始数据执行纠错编码来生成奇偶校验位;以及将原始数据和由第二纠错电路生成的奇偶校验位中的一些存储在存储器装置中,并且将地址和由第二纠错电路生成的剩余奇偶校验位存储在映射存储器中,其中,第二纠错电路的可纠正错误位的最大数量大于第一纠错电路的可纠正错误位的最大数量。

7、根据发明构思,提供一种存储装置,所述存储装置包括:存储器装置;以及控制器,被配置为控制存储器装置,其中,控制器包括:纠错电路,被配置为纠正数据的错误;映射存储器,被配置为存储由纠错电路生成的奇偶校验位中的至少一些,并且存储存储所述数据的存储器装置的地址;以及控制块,被配置为响应于写入请求将原始数据写入存储器装置中,读取存储在存储器装置中的数据,并且基于将读取的数据与原始数据进行比较的结果来控制纠错电路。

技术特征:

1.一种存储装置,包括:

2.根据权利要求1所述的存储装置,其中,控制块还被配置为:

3.根据权利要求1所述的存储装置,其中,映射存储器被配置为:存储存储原始数据的存储器装置的地址和由第二纠错电路生成的全部奇偶校验位。

4.根据权利要求1所述的存储装置,其中,基于从所述存储装置的外部接收到写入请求或读取请求,控制块还被配置为:检查写入地址或读取地址是否与存储在映射存储器中的存储器装置的地址相同,并且选择第一纠错电路和第二纠错电路中的一个执行纠错编码或纠错解码。

5.根据权利要求4所述的存储装置,其中,基于写入地址与存储在映射存储器中的存储器装置的地址相同,控制块还被配置为:选择第二纠错电路对包括在写入请求中的数据执行纠错编码。

6.根据权利要求1所述的存储装置,其中

7.根据权利要求1所述的存储装置,其中

8.根据权利要求1所述的存储装置,其中,控制块还被配置为:将存储在映射存储器中的地址和奇偶校验位存储在存储器装置中。

9.根据权利要求1至8中任一项所述的存储装置,其中,控制器还包括:第三纠错电路,被配置为纠正存储在映射存储器中的数据的错误,并且比第二纠错电路具有更大的可纠正错误位的最大数量。

10.一种存储装置,包括:

11.根据权利要求10所述的存储装置,其中,由第一纠错电路或第二纠错电路基于原始数据中的错误位的数量对原始数据执行纠错编码。

12.根据权利要求10所述的存储装置,其中,基于所述存储装置接收到写入请求或读取请求并且写入地址或读取地址与存储在映射存储器中的地址相同,第二纠错电路还被配置为:对受到写入请求或读取请求的原始数据执行纠错编码或纠错解码。

13.根据权利要求10所述的存储装置,其中

14.根据权利要求10所述的存储装置,其中

15.根据权利要求10所述的存储装置,其中,存储器装置存储所述地址和存储在映射存储器中的所述码字的一部分。

16.一种操作存储装置的方法,所述方法包括:

17.根据权利要求16所述的方法,还包括:

18.根据权利要求17所述的方法,其中,参考值等于第一纠错电路的可纠正错误位的最大数量。

19.根据权利要求16所述的方法,还包括:

20.根据权利要求16所述的方法,还包括:

技术总结

提供一种存储装置及其操作方法。所述存储装置包括:存储器装置,被配置为存储原始数据;以及控制器,被配置为控制存储器装置,控制器包括:第一纠错电路,被配置为纠正原始数据的错误;以及第二纠错电路,被配置为纠正原始数据的错误,第二纠错电路的可纠正错误位的最大数量大于第一纠错电路的可纠正错误位的最大数量;映射存储器,被配置为存储由第二纠错电路生成的奇偶校验位中的至少一些,并且存储存储原始数据的存储器装置的地址;以及控制块,被配置为控制第一纠错电路、第二纠错电路和映射存储器。

技术研发人员:吴恩惠,朴太煜,姜智守,李容基

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!