相变存储器的制作方法

1.本技术实施例涉及半导体技术领域,特别涉及一种相变存储器。

背景技术:

2.相变随机存取存储器(phase change random access memory,pcram)弥补了动态随机存取存储器(dynamic random access memory,dram)和闪存(flash)之间的性能差距,具有高速读取、高可擦写次数、非易失性、元件尺寸小、功耗低、抗强震动和抗辐射等优点,而被广泛地使用。

3.相变存储器的相变存储单元的测试主要包括置位(set)、复位(reset)和读(read)操作。然而,相关技术中采用施加电压脉冲的方法对相变存储单元进行reset操作,这不仅容易造成相变存储单元的损坏,而且使得相变过程中相变存储单元的瞬态电流的准确计算非常困难,从而限制了相变存储器性能的提升。

技术实现要素:

4.有鉴于此,本技术实施例提供一种相变存储器。

5.本技术实施例提供一种相变存储器,包括:

6.相变存储单元阵列及与所述存储单元阵列耦接的外围电路;其中,

7.所述相变存储单元阵列包括:多条字线、多条位线及位于所述多条字线和所述多条位线之间的多个相变存储单元;

8.所述外围电路包括:电流脉冲产生电路及电流脉冲控制电路;其中,

9.所述电流脉冲产生电路与所述多个相变存储单元连接,用于在所述字线和所述位线之间产生电流脉冲,并通过所述电流脉冲使得待操作的相变存储单元形成通路;

10.所述电流脉冲控制电路与所述多个相变存储单元连接,用于调整所述通路上的电流脉冲的大小。

11.上述方案中,所述电流脉冲产生电路包括电流发生子电路、字线选择子电路、位线选择子电路;其中,所述电流发生子电路的输出端与所述字线选择子电路的一端连接,所述字线选择子电路的另一端与所述多个相变存储单元的一端连接,所述多个相变存储单元的另一端与所述位线选择子电路的一端连接,所述位线选择子电路的另一端与所述电流脉冲控制子电路连接;

12.所述电流发生子电路用于产生所述电流脉冲;通过所述字线选择子电路选择所述待操作的相变存储单元对应的字线,通过所述位线选择子电路选择所述待操作的相变存储单元对应的位线。

13.上述方案中,所述字线选择子电路和/或位线选择子电路包括多个上拉管,所述上拉管通过第一电阻连接到高电平。

14.上述方案中,所述相变存储单元包括层叠设置的相变存储层、选通层及三个电极层,所述相变存储层位于所述三个电极层中第一电极层和第二电极层之间,所述选通层位

于所述三个电极层中第二电极层和第三电极层之间;每个所述相变存储单元通过所述字线与所述字线选择子电路的一端连接,所述相变存储单元通过所述位线与所述位线选择子电路的一端连接。

15.上述方案中,所述电流脉冲控制电路包括电流镜子电路,所述电流镜子电路的一端与外部参考电流连接,所述电流镜子电路的另一端与所述多个相变存储单元连接;所述电流镜子电路用于控制所述通路上的电流脉冲大小。

16.上述方案中,所述电流镜子电路还包括多个下拉管,所述下拉管通过第二电阻连接到地低电平。

17.上述方案中,所述电流脉冲控制电路还包括电流测试子电路,的输入端与所述电流镜子电路的输出端连接,所述电流测试子电路用于测试所述电流镜子电路产生的电流与设定的电流是否相同。

18.上述方案中,所述电流镜子电路的输入端与外部电压源或电流源连接,通过所述电压源控制电压实现所述通路的电流控制或者通过所述电流源控制电流实现所述通路的电流控制。

19.本技术实施例提供一种相变存储器,包括:

20.相变存储单元阵列及与所述存储单元阵列耦接的外围电路;其中,所述相变存储单元阵列包括:多条字线、多条位线及位于所述多条字线和所述多条位线之间的多个相变存储单元;所述外围电路包括:电流脉冲产生电路及电流脉冲控制电路;其中,所述电流脉冲产生电路与所述多个相变存储单元连接,用于在所述字线和所述位线之间产生电流脉冲,并通过所述电流脉冲使得待操作的相变存储单元形成通路;所述电流脉冲控制电路与所述多个相变存储单元连接,用于调整所述通路上的电流脉冲的大小。本技术各实施例中,通过在相变存储器内部的外围电路中设置所述电流脉冲产生电路和所述电流脉冲控制电路,从而能够产生高精度电流脉冲并实现精确的电流脉冲控制。可以理解的是,设置所述电流脉冲产生电路和所述电流脉冲控制电路,相较于传统设置在相变存储器外部的电流脉冲系统而言电阻电容(resistance capacitance,rc)延迟存在较大程度的改善,并且,不易受到其他设备的干扰,进而相变存储器的性能得到了提高。

附图说明

21.图1a为本技术实施例提供的一种相变存储单元及电流脉冲硬件测试系统的组成框图示意图;

22.图1b为本技术实施例提供的一种相变存储单元及电流脉冲硬件测试系统的电路模型示意图;

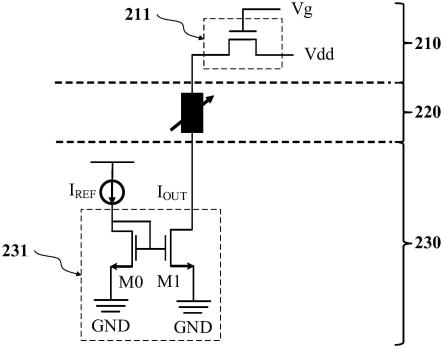

23.图2为本技术实施例提供的一种相变存储器的局部电路模型示意图;

24.图3为本技术实施例提供的另一种相变存储器的局部电路模型示意图。

25.图4为本技术实施例提供的又一种相变存储器的功能层示意图。

具体实施方式

26.以下结合说明书附图及具体实施例对本技术的技术方案做进一步的详细阐述。

27.在本技术实施例中,术语“第一”、“第二”等是用于区别类似的对象,而不用于描述

特定的顺序或先后次序。

28.在本技术实施例中,术语“a与b接触”包含a与b直接接触的情形,或者a、b两者之间还间插有其它部件而a间接地与b接触的情形。

29.在本技术实施例中,术语“层”是指包括具有厚度的区域的材料部分。层可以在下方或上方结构的整体之上延伸,或者可以具有小于下方或上方结构范围的范围。此外,层可以是厚度小于连续结构厚度的均质或非均质连续结构的区域。例如,层可位于连续结构的顶表面和底表面之间,或者层可在连续结构顶表面和底表面处的任何水平面对之间。层可以水平、垂直和/或沿倾斜表面延伸。并且,层可以包括多个子层。

30.可以理解的是,本技术中的“在

……

上”、“在

……

之上”和“在

……

上方”的含义应当以最宽方式被解读,以使得“在

……

上”不仅表示其“在”某物“上”且其间没有居间特征或层(即直接在某物上)的含义,而且还包括“在”某物“上”且其间有居间特征或层的含义。

31.需要说明的是,虽然本说明书按照实施方式加以描述,但并非每个实施方式仅包含一个独立的技术方案,说明书的这种叙述方式仅仅是为清楚起见,本领域技术人员应当将说明书作为一个整体,各实施方式中的技术方案也可以经适当组合,形成本领域技术人员可以理解的其它实施方式。

32.为了便于描述,本技术实施例及附图中z轴表示堆叠层堆叠的方向,x轴表示与堆叠的方向垂直的方向。

33.相变存储器基于存储单元的相变材料的电阻改变(例如,处于高电阻状态或低电阻状态)来存储数据。相变存储器具有无晶体管的交叉点架构,该架构使存储单元位于垂直导体的相交处,这里的垂直导体包括彼此垂直相交的字线(word line,wl)与位线(bit line,bl),wl和bl一般由图案化工艺之后形成的20nm/20nm等幅线宽(line/space,l/s)构成。

34.不同于以电荷形式存储数据的dram和flash,相变存储器是利用相变材料的结晶态和非结晶态的特性来存储数据,对相变材料用不同的电脉冲诱导,使得相变材料在非结晶态与结晶态之间进行快速和可逆的相变。使用电流加热,使得相变材料从非结晶态转化为结晶态,这一过程称为set操作;或者,使得相变材料从结晶态转换为非结晶态,这一过程称为reset操作。相变材料的这种状态的变化就可以表示一个比特的数据“0”或“1”。向所述相变材料输入一电信号,使所述相变材料不发生相变,测量电路中的电流大小,得出所述相变材料的电阻,根据电阻值的大小从而读取数据“0”或“1”,这一过程称为read操作。

35.对相变存储器的相变存储单元的测试主要包括set、reset和read操作。然而,相对于set和read操作,reset操作(结晶态转换为非结晶态)电流过大,通常采用施加电压脉冲的方法对相变存储单元进行reset操作时,这不仅容易造成相变存储单元的损坏,而且使得相变过程中相变存储单元的瞬态电流的准确计算非常困难,从而限制了相变存储器性能的提升。

36.图1a为本技术实施例提供的一种相变存储单元及电流脉冲硬件测试系统的组成框图示意图。本技术实施例提供的电流脉冲测试系统与待测试的相变存储单元107相连,所述电流脉冲测试系统包括脉冲发生器101、恒流驱动芯片102、可编程电阻103、数字信号源104、切换盒105、示波器106。本技术实施例提供的电流脉冲测试系统的设计结构复杂,导致系统设备繁多,连接线多,不利于提高对相变存储单元107的测试精度;并且,所述电流脉冲

测试系统的rc延迟很严重,没有办法实现高频脉冲测试;再就是,所述电流脉冲测试系统的集成度较低,单一设备受到的干扰较大,难以实现高精度的测试。

37.图1b为本技术实施例提供的一种相变存储单元及电流脉冲硬件测试系统的电路模型示意图。所述电流脉冲产生电路110包括电流发生子电路111、字线选择子电路(未示出)、位线选择子电路(未示出);所述电流发生子电路111的输出端与所述多个相变存储单元120的一端连接,所述多个相变存储单元120的另一端与公共端gnd连接;所述电流发生子电路111的输入端与电压源vdd连接,通过所述电流发生子电路111的控制端vg控制电流脉冲时间,就能够输出一定脉宽和脉幅的高频脉冲。

38.然而,相对于set操作,reset操作(结晶态转换为非结晶态)电流过大,本技术实施例采用施加电压脉冲的方法对相变存储单元进行reset操作时,产生的所述高频脉冲,由于所述高频脉冲的脉宽和脉幅的精度不高,不仅容易造成相变存储器的相变存储单元的损坏,而且使得相变存储单元的相变过程中瞬态电流的准确计算非常困难,从而限制了相变存储器性能的提升。

39.基于此,为解决上述问题中的一个或多个,本技术实施例提供了一种相变存储器。本技术实施例提供了一种相变存储器可以用于对相变存储单元进行电流脉冲测试,所述相变存储器可以提供准确可控的电流脉冲来对相变存储单元进行操作,从而提升相变存储器的性能。

40.图2为本技术实施例提供的一种相变存储器的局部电路模型示意图。

41.如图2所示,本技术实施例提供一种相变存储器,包括:相变存储单元阵列及与所述存储单元阵列耦接的外围电路;其中,

42.所述相变存储单元阵列包括:多条字线(未示出)、多条位线(未示出)及位于所述多条字线和所述多条位线之间的多个相变存储单元220;

43.所述外围电路包括:电流脉冲产生电路210及电流脉冲控制电路230;其中,

44.所述电流脉冲产生电路210与所述多个相变存储单元220连接,用于在所述字线和所述位线之间产生电流脉冲,并通过所述电流脉冲使得待操作的相变存储单元220形成通路;

45.所述电流脉冲控制电路230与所述多个相变存储单元220连接,用于调整所述通路上的电流脉冲的大小。

46.在一些实施例中,所述电流脉冲产生电路210包括电流发生子电路211、字线选择子电路(未示出)、位线选择子电路(未示出);其中,所述电流发生子电路211的输出端与所述字线选择子电路(未示出)的一端连接,所述字线选择子电路(未示出)的另一端与所述多个相变存储单元220的一端连接,所述多个相变存储单元220的另一端与所述位线选择子电路(未示出)的一端连接,所述位线选择子电路(未示出)的另一端与所述电流脉冲控制子电路211连接;

47.所述电流发生子电路211用于产生所述电流脉冲;通过所述字线选择子电路(未示出)选择所述待操作的相变存储单元220对应的字线,通过所述位线选择子电路(未示出)选择所述待操作的相变存储单元220对应的位线。

48.示例性地,所述电流发生子电路211的输入端与电压源vdd连接,通过所述电流发生子电路211的控制端vg控制电流脉冲时间,就能够输出一定脉宽和脉幅的高频脉冲。通过

所述字线选择子电路(未示出)和所述位线选择子电路(未示出)选择所述待操作的相变存储单元220,而与所述电流发生子电路211的输出端连接,这样,就可以将所述高频脉冲施加给所述待操作的相变存储单元220。

49.在一些实施例中,所述电流脉冲的频率高于预设频率。实际应用中,所述预设频率可以根据实际情况进行调整。在一具体示例中,所述预设频率为104hz。

50.这里,所述电流脉冲产生电路包括高频电流脉冲产生部分,通过电流发生子电路211能够产生一定脉宽和脉幅的高频脉冲,所述电流发生子电路211直接与相变存储单元220相连接,能够减小外部电路连接带来的较大的rc延迟,提高测试精度。

51.在一些实施例中,所述字线选择子电路(未示出)和/或位线选择子电路(未示出)包括多个上拉管,所述上拉管通过第一电阻(未示出)连接到高电平。

52.这里,所述多个上拉管可以在所述字线选择子电路和/或位线选择子电路的控制端关断的情况下,保持所述字线选择子电路和/或位线选择子电路的输入端的节点的电位稳定。

53.示例性地,在所述字线选择子电路和/或位线选择子电路中的金属-氧化物半导体(metal-oxide-semiconductor,mos)晶体管(后简称mos管)的输入端设置上拉,通过第一电阻连接到高电平,在所述字线选择子电路和/或位线选择子电路的控制端关断的情况下,可以保持所述字线选择子电路和/或位线选择子电路的输入端的电位稳定。

54.在一些实施例中,所述电流脉冲控制电路230包括电流镜子电路231,所述电流镜子电路231的一端与外部参考电流连接,所述电流镜子电路231的另一端与所述多个相变存储单元连接;所述电流镜子电路231用于控制所述通路的电流脉冲大小。

55.实际应用中,在电流镜子电路231中,在参考电压源或参考电流源产生一个参考电流i

ref

,然后采用电流镜将参考电流i

ref

按照比例放大为所需的驱动电流i

out

进行输出,即i

out

=n*i

ref

,其中,n可以大于1、小于1或等于1。输出电流与待操作的相变存储单元连接,从而可以实现对所述通路的电流幅值和/或电流脉冲大小的控制。

56.在一些实施例中,所述电流镜子电路231的输入端与外部电压源或电流源连接,通过所述电压源(未示出)控制电压实现所述通路的电流控制或者通过所述电流源(未示出)控制电流实现所述通路的电流控制。

57.示例性地,通过所述电压源控制电压产生一个能被精准控制的参考电流i

ref

或者通过所述电流源直接输入电流产生一个能被精准控制的参考电流i

ref

,所述参考电流i

ref

用于精准控制所述通路的驱动电流i

out

,从而实现通路电流(这里可以理解为驱动电流i

out

)的精准控制。

58.在一些具体的实施例中,所述电流镜子电路231包括一个输入端和一个输出端,第一至第二mos管(m0~m1);

59.其中,在电压源或电流源产生一个所述参考电流i

ref

通过所述输入端连接至所述第一mos管(m0)的漏极,所述第一mos管(m0)的漏极连接所述第一mos管(m0)的栅极,第一至第二mos管(m0~m1)的栅极相互连接,所述第二mos管(m1)的漏极对应所述输出端,所述输出端连接至所述通路中;所述第一至第二mos管(m0~m1)的源极连接至公共端gnd。通过所述参考电流i

ref

的变化控制所述预设的驱动电流i

out

。示例性地,i

out

=1*i

ref

或i

out

=0.5*i

ref

或i

out

=1.5*i

ref

。

60.这里,通过参考电压源或参考电流源产生一个参考电流i

ref

,经过电流镜子电路输出按照比例放大为所需的驱动电流i

out

,通过所述驱动电流i

out

用以控制选中的所述通路中的电流幅值以及脉冲大小。

61.图3为本技术实施例提供的另一种相变存储器的局部电路模型示意图。

62.如图3所示,在另一些具体的实施例中,所述电流镜子电路231包括一个输入端和三个输出端,第一至第四mos管(m0~m3)、第一至第三可控选择开关(s1~s3);

63.其中,在电压源或电流源产生一个所述参考电流i

ref

通过所述输入端连接至所述第一mos管(m0)的漏极,所述第一mos管(m0)的漏极连接所述第一mos管(m0)的栅极,第一至第四mos管(m0~m3)的栅极相互连接,所述第二至第四mos管(m1~m3)的漏极分别对应三个所述输入端,三个所述输入端分别连接至所述第一至第三可控选择开关(s1~s3)的一端,所述第一至第三可控选择开关(s1~s3)的另一端连接至所述通路中;所述第一至第四mos管(m0~m3)的源极连接至公共端gnd。三个所述输入端分别用于输出三种所述预设的驱动电流i

out1

、i

out2

、i

out3

。示例性地,i

out1

=1*i

ref

,i

out2

=2*i

ref

,i

out3

=3*i

ref

。

64.这里,所述电流脉冲控制电路包括所述多个输出端,所述多个输出端可以有多路输出电流,通过参考电压源或参考电流源产生一个参考电流i

ref

,经过电流镜子电路输出按照比例放大为所需的三个驱动电流i

out1

、i

out2

、i

out3

,通过不同的所述i

out1

、i

out2

、i

out3

用以控制选中的所述通路中的不同的电流幅值以及脉冲大小。

65.需要说明的是,所述电流镜子电路231包括一个输入端和多个输出端。所述多个输出端的数量可以是两个或在其他更多数量,可以参考上述一个输入端和三个输出端的实施例进行简单的数量变态进行理解,具体详情这里不在赘述。

66.在一些实施例中,所述电流镜子电路231还包括多个下拉管,所述下拉管通过第二电阻(未示出)连接到地低电平。

67.这里,所述多个下拉管与所述公共端gnd连接,所述下拉管通过第二电阻连接到地低电平,在mos管关断的情况下可以使相应的节点(所述公共端gnd)保持电位稳定。

68.在一些实施例中,所述电流脉冲控制电路还包括电流测试子电路(未示出),所述电流测试子电路的输入端与所述电流镜子电路的输出端连接,用于测试所述电流镜子电路产生的电流与设定的电流是否相同。

69.这里,所述设定的电流可以理解为相变存储器在进行reset操作时所需要的电流。所述电流测试子电路(未示出)可以与所述电流镜子电路231的输出端连接,用于测试所述电流镜子电路产生的电流与设定的电流是否相同。

70.本技术一些实施例中,相变存储器的设计结构在相变存储单元的测试中,所作出的改进为通过选择不同电流镜子电路的输出端来实现不同比例的电流倍增,并且在旁侧的测试电路中能够实现测试电流镜子电路产生的电流,实现对电路镜子电路的电流校准,此外,为了保证相应节点的稳定电位,通过在电流镜子电路旁引出下拉管来实现电位稳定。

71.图4为本技术实施例提供的又一种相变存储器的功能层示意图。

72.如图4所示,在一些实施例中,所述相变存储单元220包括层叠设置的相变存储层404、选通层405及三个电极层,所述相变存储层404位于所述三个电极层中第一电极层401和第二电极层402之间,所述选通层405位于所述三个电极层中第二电极层402和第三电极层403之间;每个所述相变存储单元220通过所述字线wl与所述字线选择子电路(未示出)的

一端连接,所述相变存储单元220通过所述位线bl与所述位线选择子电路(未示出)的一端连接。

73.需要指出的是,上述第一电极401、第二电极402以及第三电极403表示所述相变存储单元220中的电极层,所述电极层的材料可包括非晶碳,例如α相碳。所述电极层用于传导电信号。需要强调的是,第一电极401、第二电极402以及第三电极403包括的材料可以相同或者不同,不同的附图标记只是为了区分电极层位置上的不同,而不必用于描述特定的顺序或先后次序。

74.这里,所述相变存储层404的材料可以包括:锗锑碲(ge-sb-te,gst)合金,或者,gst合金中掺杂硫(s)、氮(n)、氧(o)以及硅(si)元素中的至少一种元素形成的混合物。相变存储层404的材料还可包括任何其他适合的相变材料。

75.可以理解的是,当选通层导通时,第三电极403上的电压传递给第二电极105。所述选通层405的材料可包括:阈值选择开关(ovonic threshold sitching,ots)材料,例如geasb、geaseb、geateb、znateb、nbaob或者siaasbtec等,其中,a、b、c表示为化学计量数。

76.需要指出的是,当相变存储层404发生相变时,相变存储层404的电阻发生变化。相变存储器可根据相变存储层404的电阻状态变化进行数据的存储。

77.在一些实施例中,参照图4所示,相变存储器还可包括:

78.位线bl和字线wl;其中,位线bl、相变存储单元220以及字线wl由下至上依次堆叠设置的;位线bl和字线wl平行于同一平面且彼此垂直,所述相变存储单元220与所述位线bl和字线wl均垂直。需要说明的是,位线bl和字线wl位置也可以相互调换。

79.位线bl和字线wl的材料包括导电材料。导电材料包括但不限于钨(w)、钴(co)、铜(cu)、铝(al)、多晶硅、掺杂硅或其任何组合。位线bl和字线wl可以具有相同的导电材料,也可以具有不同的导电材料。

80.需要强调的是,设置位线bl的第一平面和设置字线wl的第二平面平行,且第一平面与第二平面不重叠。选通结构位于第一平面和第二平面之间,且选通结构与第一平面和第二平面均垂直。

81.相变存储器还包括:位于位线bl下方的衬底(未示出);衬底(未示出)的材料可包括半导体材料,例如硅(si)衬底。

82.本技术各实施例中,通过在相变存储器内部的外围电路中设置所述电流脉冲产生电路和所述电流脉冲控制电路,从而能够产生高精度电流脉冲并实现精确的电流脉冲控制。可以理解的是,设置所述电流脉冲产生电路和所述电流脉冲控制电路,相较于传统设置在相变存储器外部的电流脉冲系统而言rc延迟存在较大程度的改善,并且,不易受到其他设备的干扰,进而相变存储器的性能得到了提高。

83.需要说明的是,本技术各个实施例所提供的附图(其不一定是按比例绘制的)中,涉及电路相关的部分并不是实际电路本身,而应对以电路模型的原理示意图进行理解。

84.应理解,说明书通篇中提到的“一个实施例”或“一实施例”意味着与实施例有关的特定特征、结构或特性包括在本技术的至少一个实施例中。因此,在整个说明书各处出现的“在一个实施例中”或“在一实施例中”未必一定指相同的实施例。此外,这些特定的特征、结构或特性可以任意适合的方式结合在一个或多个实施例中。应理解,在本技术的各种实施例中,上述各过程的序号的大小并不意味着执行顺序的先后,各过程的执行顺序应以其功

能和内在逻辑确定,而不应对本技术实施例的实施过程构成任何限定。上述本技术实施例序号仅仅为了描述,不代表实施例的优劣。

85.以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1