高速缓存辅助式行锤击缓解的制作方法

本公开涉及高速缓存存储器,且具体地,协调进行存储器媒体中的行锤击攻击缓解的高速缓存存储器。

背景技术:

1、存储器装置(也被称作“存储器媒体装置”)广泛用于将信息存储在例如计算机、用户装置、无线通信装置、相机、数字显示器等各种电子装置中。通过将存储器装置内的存储器单元编程为各种状态来存储信息。例如,二进制存储器单元可被编程为常常对应于逻辑1或逻辑0的两个支持状态中的一者。在一些实例中,单个存储器单元可支持多于两个可能的状态,所述状态中的任一个可由存储器单元存储。为了存取由存储器装置存储的信息,组件可以读取或感测存储器装置内的一或多个存储器单元的状态。为了存储信息,组件可以将存储器装置内的一或多个存储器单元写入或编程到对应状态。

2、存在各种类型的存储器装置,包含磁性硬盘、随机存取存储器(ram)、只读存储器(rom)、动态ram(dram)、同步动态ram(sdram)、静态ram(sram)、快闪存储器等。存储器装置可为易失性或非易失性的。除非由外部电源周期性更新,否则易失性存储器单元(例如,dram单元)可随时间推移而丢失其编程状态。sram存储器可在系统正通电的持续时间内维持其编程状态。非易失性存储器单元(例如,nand存储器单元)即使在不存在外部电源的情况下仍可在很长一段时间内维持其编程状态。

3、存储器装置可耦合到主机(例如,主机计算装置)以存储数据、命令和/或指令以供主机在计算机或其它电子系统操作时使用。例如,数据、命令和/或指令可在计算或其它电子系统的操作期间在主机与存储器装置之间传送。称为“存储器控制器”的控制器可用于管理数据、命令和/或指令在主机与存储器装置之间的传送。

4、dram被组织为存储单元阵列,其中每个单元存储经编程值。如上文所指出,如果未周期性地刷新,那么单元可失去其编程值。因此,以通常被称作“刷新间隔”的固定间隔刷新行。刷新也被称为“行激活”。在行激活中,读取dram装置中的行,校正错误且将其写入回到同一物理行。在当前dram装置中,由“行锤击事件”(也被称作“行锤击攻击”)引起的数据损坏是相当大的风险。

5、当媒体装置中的特定行在“激活间隔”(即,两个刷新/激活事件之间的间隔)中被多次存取,即,超出“行锤击阈值”(rht)次数时,行锤击事件发生。具体地说,当在激活间隔期间存取特定行(“侵入者行”)超过rht次数时,物理上接近于dram媒体中的所述特定行的一或多个行(“受害者行”)可由于特定行的频繁激活而受影响,且可发生一或多个行的数据损坏。由于收缩制造过程几何形状的各种物理影响,存储器装置的rht已降低到甚至普通计算机系统程序可能无意中损坏其自身数据或共享同一系统存储器的另一程序的数据的水平。

6、一些存储器媒体装置包含用于检测和缓解行锤击攻击的电路。常规行锤击检测器技术,例如“地址采样”和“优先级cam”(优先级内容可寻址存储器)是概率性的,且因此不能保证在任何和所有行锤击场景中完美(即完整、准确和精确)防止数据损坏。如果侵入者(例如,恶意攻击者)知道这些常规行锤击检测方法及其实施方案的足够细节,那么侵入者可攻击其缺点以绕过或破坏其并损坏数据。因此,需要改进的技术来缓解例如行锤击错误之类的软错误。

技术实现思路

1、本公开的方面涉及一种系统,其包括:高速缓存存储器,存储器媒体存取控制电路;主机接口,其被配置成将所述存储器媒体存取控制电路可操作地耦合到主机装置;媒体接口,其被配置成将所述存储器媒体存取控制电路可操作地耦合到存储器媒体装置;以及行锤击缓解器电路,其被配置成:当所述存储器媒体装置可操作地耦合到所述媒体接口时,跟踪所述存储器媒体装置中的行激活;以及将与跟踪的行激活相关联的信息传输到所述高速缓存存储器。

2、本公开的另一方面涉及一种方法,其包括:通过布置在系统中的行锤击缓解器电路在存储器媒体装置可操作地耦合到所述系统的媒体接口时跟踪所述存储器媒体装置中的行激活;以及通过所述行锤击缓解器电路将与跟踪的行激活相关联的信息传输到高速缓存存储器。

技术特征:

1.一种系统,其包括:

2.根据权利要求1所述的系统,其中所述高速缓存存储器被配置成根据所述存储器媒体装置中的对应行的所述跟踪的行激活来偏置高速缓存线分配策略。

3.根据权利要求2所述的系统,其中所述高速缓存存储器被配置成通过偏置以防所述存储器媒体装置中具有小于第一阈值的行存取计数的行插入到所述高速缓存存储器中,根据所述存储器媒体装置中的对应行的所述跟踪的行激活偏置高速缓存线分配。

4.根据权利要求1所述的系统,其中所述高速缓存存储器被配置成根据所述存储器媒体装置中的对应行的所述跟踪的行激活偏置高速缓存线逐出策略。

5.根据权利要求4所述的系统,其中所述高速缓存存储器被配置成通过偏置以防逐出与所述存储器媒体装置中具有超过第二阈值的行存取计数的行相对应高速缓存线,根据所述存储器媒体装置中的对应行的所述跟踪的行激活偏置高速缓存线逐出,其中所述第二阈值小于行锤击阈值。

6.根据权利要求1所述的系统,其中传输的信息包括所述存储器媒体装置的行的行激活计数或基于所述行激活计数确定的行锤击状态中的至少一者。

7.根据权利要求1所述的系统,其进一步包括:

8.根据权利要求7所述的系统,其中所述高速缓存存储器中的每个高速缓存线包括来自所述存储器媒体装置的数据的副本、指示所述数据的所述存储器媒体装置的一部分的标签,以及包括所述行激活电平值集中的行激活电平值的状态字段。

9.根据权利要求8所述的系统,其中所述状态字段进一步包括逐出策略指示符和一致性策略指示符。

10.根据权利要求9所述的系统,其中所述行激活电平值集基于来自所述行锤击缓解器电路的信息而更新。

11.根据权利要求1所述的系统,其中所述行锤击缓解器电路进一步被配置成:

12.根据权利要求1所述的系统,其中所述存储器存取控制电路进一步被配置成将标签信息传达到所述行锤击缓解器电路。

13.根据权利要求1所述的系统,其中所述高速缓存存储器、所述存储器媒体存取控制电路、所述主机接口、所述存储器媒体接口和所述行锤击缓解器电路布置在存储器控制器中。

14.根据权利要求1所述的系统,其中所述存储器媒体存取控制电路、所述主机接口、所述存储器媒体接口和所述行锤击缓解器电路布置在通过高速缓存存储器接口耦合到所述高速缓存存储器的存储器控制器中。

15.根据权利要求1所述的系统,其中所述存储器媒体装置包括动态随机存取存储器dram并且所述高速缓存存储器包括静态随机存取存储器sram。

16.根据权利要求1所述的系统,其中所述行锤击缓解器电路包括多个计数器,其中所述多个计数器中的计数器的总数小于由所述存储器媒体装置上的存储器错误检测器监测的行的总数。

17.根据权利要求1所述的系统,其中所述行锤击缓解器电路包括布置在内容可寻址存储器cam或静态随机存取存储器sram中的多个计数器。

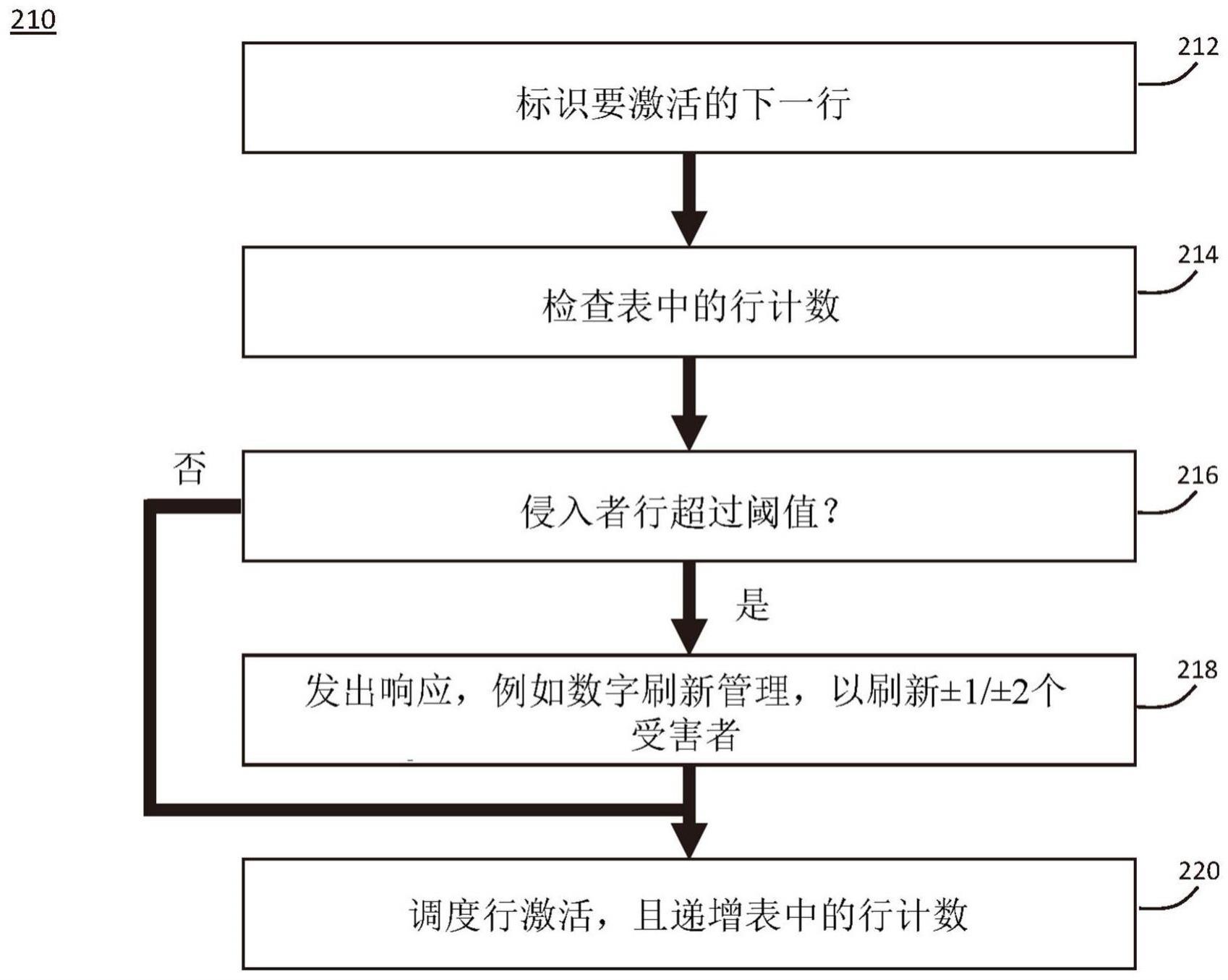

18.根据权利要求1所述的系统,其中所述行锤击缓解器电路被配置成发出包括数字刷新管理drfm命令的响应,以刷新与行标识符相对应的行的一或多个物理相邻行。

19.一种方法,其包括:

20.根据权利要求19所述的方法,其中与所述跟踪的行激活相关联的所述信息包含指示所述存储器媒体装置的相应行的所述跟踪的行激活是否超过一或多个预设阈值的行锤击状态指示。

技术总结

本公开涉及高速缓存辅助式行锤击缓解。描述一种系统,其包括行锤击缓解电路和高速缓存存储器,其协作以缓解存储器媒体装置上的行锤击攻击。所述高速缓存存储器基于由所述行锤击缓解电路维持的行存取计数信息偏置高速缓存策略。所述行锤击缓解电路可实施于存储器控制器中。所述存储器媒体装置可以是DRAM。还描述对应方法。

技术研发人员:E·吉斯克,C·德里克

受保护的技术使用者:美光科技公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!