多电平感测电路及包括其的半导体存储器件的制作方法

本公开的实施例一般而言可涉及一种多电平感测电路和包括所述多电平感测电路的半导体器件,更具体地说,涉及一种用于感测多个电平(多电平)的技术。

背景技术:

1、动态随机存取存储器或“dram”是众所周知的半导体存储器件。它也被称为“易失性”存储器件。

2、dram存储单元包括单元晶体管和单元电容器。单元晶体管控制对单元电容器的访问。dram单元电容器储存电荷。电荷的状态对应于二进制值数据。换句话说,现有技术的dram中储存的数据根据储存在dram单元电容器中的电荷量分为高电平或低电平数据。当dram半导体器件的字线被使能时,位线与取反位线、即位线上的值的布尔逻辑互补之间发生电荷共享。然后,感测放大器工作以确定dram电容器上的电荷状态。

3、除了单元晶体管和电容器外,dram还包括驱动器和/或感测放大器,其通过线路或总线传输信号。dram存储单元通常也包括感测放大器,其将从多个存储单元生成的数据输出到数据传输线或数据总线。

4、包括存储器件的半导体器件在尺寸上持续减小。然而,关于包括半导体存储器件的半导体能够被制造得有多小,是有限制的。

5、现有技术的存储器件仅使用两个不同的值或电平来储存数据。如果可以在能够使用多于两个值或电平的存储器件中储存数据,则每单位面积能够比二值存储器件储存更多的数据。

技术实现思路

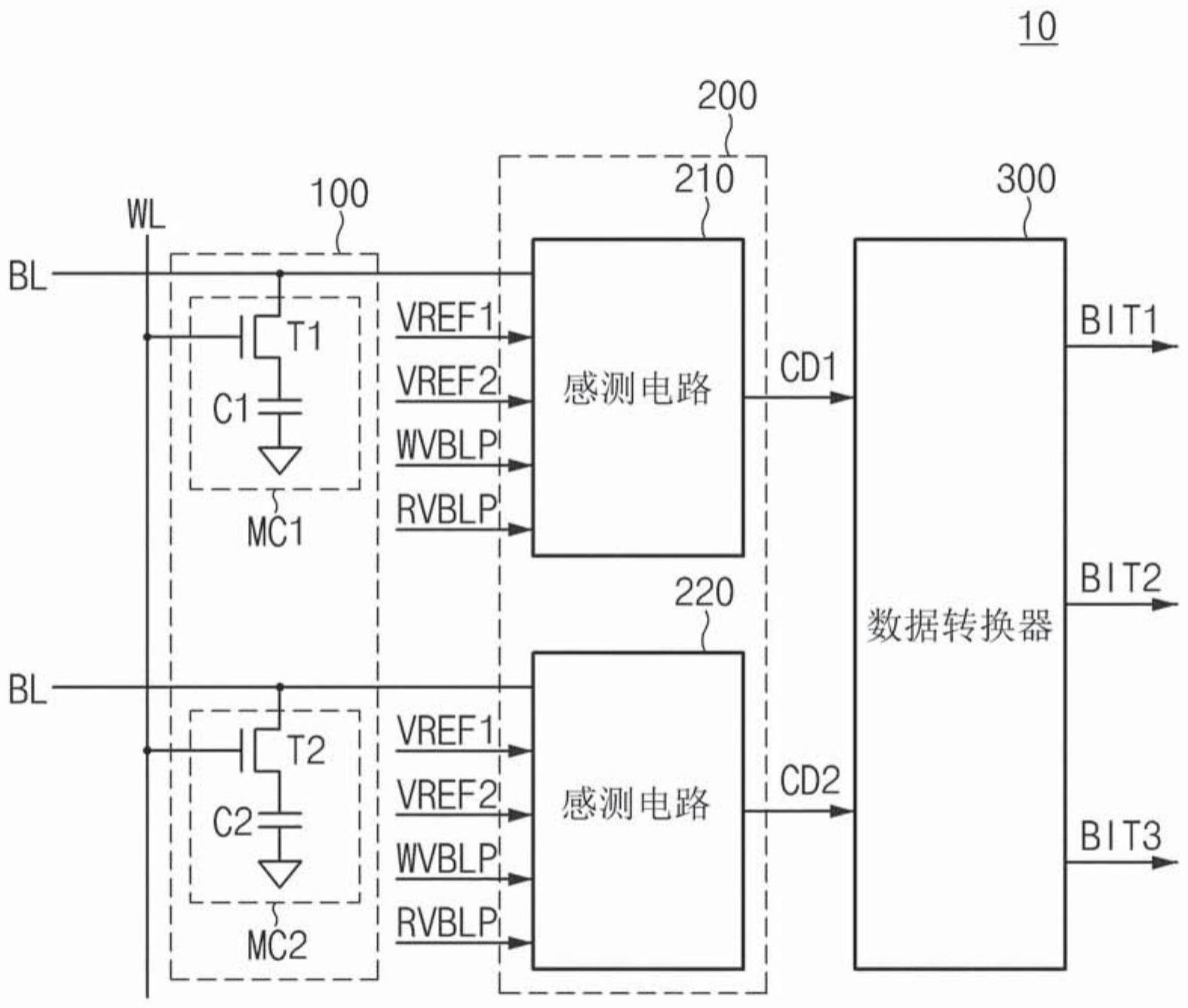

1、本文公开的电路感测代表不同数据值或不同信息的多个不同电压电平,并将这些不同电压电平转换为对应于二进制值数据的二进制值电压。

2、在一个实施例中,一种多电压电平感测电路包括预充电控制器,所述预充电控制器在感测模式期间响应于均衡信号以位线预充电电压将“位线”预充电。所述多电平感测电路还包括读取控制器,所述读取控制器在感测操作期间响应于读取控制信号将所述位线的电压保持在所述位线预充电电压电平。感测放大器在所述感测操作期间从所述位线产生数据,电压传感器通过比较位线电压与参考电压来产生均衡信号。

3、根据本发明的另一实施例,一种半导体器件包括:感测放大器,其被配置为包括第一下拉电源线和第二下拉电源线,以及在感测操作期间响应于施加到所述第一下拉电源线和所述第二下拉电源线的驱动电压来感测一对位线的数据;电压控制器,其被配置为在所述感测操作期间响应于在不同时间被激活的驱动信号而选择性地将具有不同电平的偏置电压提供给所述第一下拉电源线和所述第二下拉电源线;以及数据转换器,其被配置为将从所述一对位线接收的第一感测数据和第二感测数据相互比较,并且响应于被比较数据的取反或非取反来鉴别数据。

4、根据本公开的另一实施例,一种多电平感测电路包括:第一感测放大器,其被配置为经由第二下拉电源线和第四下拉电源线接收驱动电压;第二感测放大器,其被配置为经由第一下拉电源线和第三下拉电源线接收驱动电压;第一电压控制器,其被配置为在感测模式期间响应于第一驱动信号和第二驱动信号向所述第一下拉电源线和所述第二下拉电源线提供具有不同电平的偏置电压;以及第二电压控制器,其被配置为在所述感测模式期间响应于所述第一驱动信号和第三驱动信号向所述第三下拉电源线和所述第四下拉电源线提供具有不同电平的偏置电压。

5、本领域普通技术人员应理解,上述

技术实现要素:

和以下详细描述是为了说明的目的。权利要求书中阐述要求保护的主题的真正范围。

技术特征:

1.一种多电平感测电路,包括:

2.根据权利要求1所述的多电平感测电路,还包括:

3.根据权利要求1所述的多电平感测电路,其中,所述第一电压控制器包括:

4.根据权利要求1所述的多电平感测电路,其中,所述第二电压控制器包括:

技术总结

本发明提供一种多电平感测电路及包括其的半导体存储器件。一种用于多电平存储器件的多电平感测电路,其被配置为识别多于两个的不同电压。多电平电压感测电路可以包括预充电控制器,所述预充电控制器被配置为在感测模式期间响应于均衡信号以位线预充电电压电平将一对位线预充电。多电平电压感测电路可以包括读取控制器,所述读取控制器被配置为在感测操作期间响应于读取控制信号将所述一对位线的电压保持在位线预充电电压电平。多电平电压感测电路可以包括感测放大器,所述感测放大器被配置为在感测模式期间产生所述一对位线的数据。多电平电压检测电路可以包括电压传感器,所述电压传感器被配置为通过比较位线电压与参考电压来产生均衡信号。

技术研发人员:元炯植,金台勋

受保护的技术使用者:爱思开海力士有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!