SRAM及片上系统的制作方法

本发明涉及存储器,特别涉及一种sram及片上系统。

背景技术:

1、sram(static random-access memory,静态随机存取存储器)是一种只要在供电条件下便能够存储数据的存储器件,具有存储容量小、运算速度快、运行效率高等特点,是大多数高性能片上集成系统(system on chip,soc)的一个关键组件。

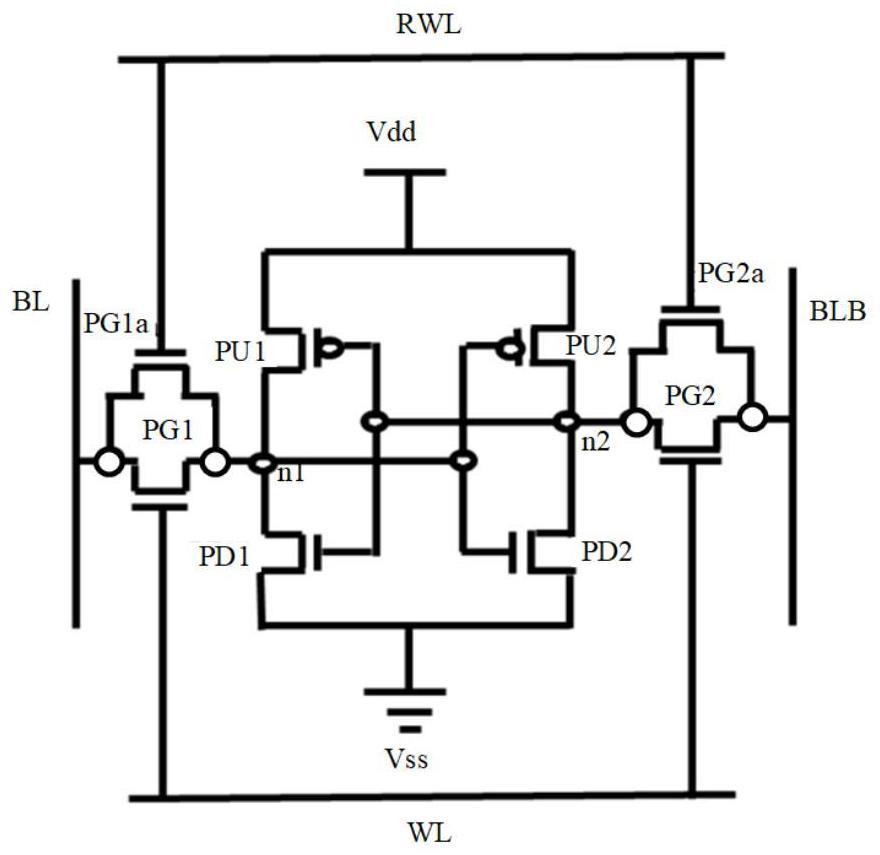

2、目前sram的主流设计是6t sram结构,该sram的基本存储单元称为一个bit,只能存储一个信号0或者1,这样一个bit由6个晶体管(transistor)构成,请参考图1,具体分为2个pmos管pu1、pu2,4个nmos管pd1、pd2、pg1、pg2。其中,nmos管pg1、pg2也称为传输门晶体管(pass gate transistor)或者存取晶体管(access transistor),其功能是实现

3、—位线(bitline)bl和bl的接入,以实现读写功能。pmos管pu1、pu2也称为上拉晶体管(pull up transistor)或负载晶体管(load transistor),其功能是实现相应节点的高电位(也就是1的状态),nmos管pd1、pd2也称为下拉晶体管(pull down transistor)或驱动晶体管(drive transistor),其功能是实现相应节点的低电位(也就是0的状态),pu1和pd1形成一个反相器,pu2和pd2形成另一个反相器,两个反相器形成互锁结构,来实现数据的保存。这样一个bit中的两个节点(snl和snr)高低电位互换,就能实现0和1两种状态的存储。

4、然而现有的6t sram读写能力存在瓶颈,难以满足更好性能的片上系统等需求。

技术实现思路

1、本发明的目的在于提供一种sram及片上系统,具有较高的读写能力。

2、为实现上述目的,本发明提供一种sram,所述sram具有存储阵列,且所述存储阵列中的基本存储单元包括:

3、第一至第二负载晶体管和第一至第二驱动晶体管,第一负载晶体管的漏极、第一驱动晶体管的漏极、第二负载晶体管的栅极和第二驱动晶体管的栅极均耦接到第一节点,第一负载晶体管的栅极、第一驱动晶体管的栅极、第二负载晶体管的漏极及第二驱动晶体管的漏极均耦接到第二节点,第一负载晶体管的源极和第二负载晶体管的源极均耦接第一电源,第一驱动晶体管的源极和第二驱动晶体管的源极均耦接第二电源;

4、第一至第四存取晶体管,第一存取晶体管的栅极和第二存取晶体管的栅极均耦接第一字线,第三存取晶体管的栅极和第四存取晶体管的栅极耦接第二字线,第一存取晶体管的源极和第三存取晶体管的源极均耦接第一位线,第一存取晶体管的漏极和第三存取晶体管的漏极均耦接第一节点,第二存取晶体管的源极和第四存取晶体管的源极均耦接第二位线,第二存取晶体管的漏极和第四存取晶体管的漏极均耦接第二节点。

5、可选地,当所述第三存取晶体管的沟道长度与所述第一存取晶体管的沟道长度相同时,所述第三存取晶体管的沟道宽度是所述第一存取晶体管的沟道宽度的1/3~1/2。

6、可选地,当所述第四存取晶体管的沟道长度与所述第二存取晶体管的沟道长度相同时,所述第四存取晶体管的沟道宽度是所述第二存取晶体管的沟道宽度的1/3~1/2。

7、可选地,对所述最小存储单元进行读操作时,所述第一字线和所述第二字线均为高电平;对所述最小存储单元进行写操作时,所述第一字线为高电平,所述第二字线为低电平。

8、可选地,第一至第四存取晶体管、第一驱动晶体管和第二驱动晶体管均为nmos管,所述第一负载晶体管和所述第二负载晶体管均为pmos管。

9、可选地,所述第一电源为系统供电电源,所述第二电源为地。

10、可选地,所述sram还包括述sram还包括控制电路以及分别耦接所述存储阵列和所述控制电路的行地址译码器、列地址译码器和灵敏放大器。

11、基于同一发明构思,本发明还提供一种片上系统,其包括如本发明所述的sram。

12、与现有技术相比,本发明的技术方案至少具有以下有益效果之一:

13、1、仅在现有的6t sram存储单元的基础上增加一组存取晶体管,不会增加工艺复杂度;

14、2.在现有的6t sram存储单元的存取晶体管上并联了额外的存取晶体管,因此可以使得β=ipd/ipg//pga,相当于增强了现有的6t sram存储单元中的驱动晶体管pd的驱动能力,增大读噪声容限snmr,sram的snmh、snmw和snmr相对更加平衡,因此提高了sram的读写能力。

技术特征:

1.一种sram,其特征在于,所述sram具有存储阵列,且所述存储阵列中的最小存储单元包括:

2.如权利要求1所述的sram,其特征在于,当所述第三存取晶体管的沟道长度与所述第一存取晶体管的沟道长度相同时,所述第三存取晶体管的沟道宽度是所述第一存取晶体管的沟道宽度的1/3~1/2。

3.如权利要求1所述的sram,其特征在于,当所述第四存取晶体管的沟道长度与所述第二存取晶体管的沟道长度相同时,所述第四存取晶体管的沟道宽度是所述第二存取晶体管的沟道宽度的1/3~1/2。

4.如权利要求1所述的sram,其特征在于,对所述最小存储单元进行读操作时,所述第一字线和所述第二字线均为高电平;对所述最小存储单元进行写操作时,所述第一字线为高电平,所述第二字线为低电平。

5.如权利要求1-4中任一项所述的sram,其特征在于,第一至第四存取晶体管、第一驱动晶体管和第二驱动晶体管均为nmos管,所述第一负载晶体管和所述第二负载晶体管均为pmos管。

6.如权利要求5所述的sram,其特征在于,所述第一电源为系统供电电源,所述第二电源为地。

7.如权利要求5所述的sram,其特征在于,所述sram还包括控制电路以及分别耦接所述存储阵列和所述控制电路的行地址译码器、列地址译码器和灵敏放大器。

8.一种片上系统,其特征在于,包括如权利要求1-7中任一项所述的sram。

技术总结

本发明提供一种SRAM及片上系统,该SRAM在6T SRAM存储单元的两个存取晶体管上分别并联了一个额外的存取晶体管,可以增大读噪声容限SNMR,SRAM的保持噪声容限SNMH、写噪声容限SNMW和读噪声容限SNMR相对更加平衡,因此提高了SRAM的读写能力,且不会增加工艺复杂度。本发明的片上系统,由于采用了本发明的SRAM,性能得以提高。

技术研发人员:赵朝珍

受保护的技术使用者:中芯先锋集成电路制造(绍兴)有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!