闪存的操作方法与流程

本发明涉及半导体集成电路领域,特别是涉及一种闪存(flash)的操作方法。

背景技术:

1、如图1所示,是现有闪存的存储单元的剖面结构示意图;现有闪存包括多个存储单元(cell)101,由多个所述存储单元101组成阵列单元301,由多个所述阵列单元301排列形成闪存的阵列结构。各所述存储单元101都采用分离栅浮栅器件。

2、如图1所示,所述分离栅浮栅器件包括:对称的第一源漏区205a和第二源漏区206,位于所述第一源漏区205a和所述第二源漏区205b之间的多个分离的具有浮栅104的第一栅极结构,位于所述第一栅极结构之间的第二栅极结构103;所述第一栅极结构中具有位于所述浮栅104顶部的控制栅105。

3、所述分离栅浮栅器件为双分离栅浮栅器件,所述第一栅极结构的数量为两个,分别用标记102a和102b表示。

4、所述分离栅浮栅器件为n型器件,所述第一源漏区205a和所述第二源漏区205b都由n+区组成。

5、p型掺杂的沟道区位于所述第一源漏区205a和所述第二源漏区205b之间且被各所述第一栅极结构和所述第二栅极结构103所覆盖。所述第一源漏区205a和所述第二源漏区205b都形成于p型半导体衬底201且和对应的两个所述第一栅极结构的外侧面自对准,所述沟道区之间由所述第一源漏区205a和所述第二源漏区205b之间的所述p型半导体衬底201组成或者进一步在所述p型半导体衬底201上进行掺杂形成。

6、所述存储单元101的所述第二源漏区205b连接到第二源漏电极,第二源漏电极会连接到位线bl1。

7、所述存储单元101的所述第一源漏区205a连接第一源漏电极,第一源漏电极会连接到位线bl0。

8、各所述第一栅极结构由隧穿介质层202、所述浮栅104、控制栅介质层203和所述控制栅105叠加而成。

9、各所述第二栅极结构103由字线栅介质层204和字线栅106叠加而成。

10、所述控制栅105连接到对应的控制栅线,所述字线栅106连接到字线wl。图1中,所述存储单元101包括两个所述第一栅极结构,故所述控制栅线也包括两根,分别用cg0和cg1表示,第一栅极结构102a的所述控制栅105连接到控制栅线cg0,第一栅极结构102b的所述控制栅105连接到控制栅线cg1。

11、对所述存储单元101的选定存储位进行编程(program)时,以对图1中所述第一栅极结构102a中的浮栅104对应的存储位‘a’为选定存储位为了,所加电压如表一所示:

12、表一

13、 cg0(v) wl(v) cg1(v) bl0(v) bl1 9 1.5 5 4.5 idp

14、如表一所示,存储位‘a’编程操作时所加电压包括:

15、所述控制栅线cg1接5v,用于将第一栅极结构102b所控制的沟道区的区域段打开即导通;

16、所述字线wl接1.5v,用于将所述第二栅极结构103所控制的沟道区的区域段打开;

17、位线bl1接编程电流idp。

18、控制栅线cg0接9v的高压,位线bl0接4.5v的高压,这样,编程电流经过所述第一栅极结构102b和所述第二栅极结构103所控制的沟道区的区域段到达所述第一栅极结构102a的底部之后,由于控制栅线cg0和所述位线bl1都是高压,故能实现源端热电子注入编程。

19、其中,所述字线wl所接的电压vwlp是固定电压,如上面列举的1.5v。但是实际上,随着使用条件如温度条件和擦写次数不同,各存储单元的所述第二栅极结构103所控制的沟道区的区域段的阈值电压会变化,例如,温度高时,存储单元的阈值电压会变低;温度低时,存储单元的阈值电压会变高;随着擦写次数的增加,所述第二栅极结构103中的缺陷捕获的电荷数量会增加,从而增加存储单元的阈值电压。

20、由于存储单元的所述第二栅极结构103所控制的沟道区的区域段的阈值电压会产生变化,这就使得所述字线wl的电压不太容易设置,同样以对存储位‘a’进行编程为例:

21、1、如果所述字线wl的电压设置的过高,则对所述第二栅极结构103所控制的沟道区的区域段的源端侧的电压为所述字线wl的电压减去阈值电压,显然所述第二栅极结构103所控制的沟道区的区域段的源端侧电压也会较高,这会使得位线bl0和所述第二栅极结构103所控制的沟道区的区域段的源端侧电压的电压差变小,即源漏电压会变小,cg0和bl0的电压设置使所述第一栅极结构102a所控制的沟道区的区域段工作在线性区,故源漏电压减少后,源漏电流也会减小,而源端热电子注入效率和源漏电流成比例,故源端热电子注入的编程效率会降低。

22、2、如果所述字线wl的电压设置的过低,则当存储单元位于低温环境时,阈值电压会升高,所述字线wl的电压和阈值电压的差值会变小,这也使得源漏电流会变小,编程效率会降低。

23、由上可知,现有技术中,字线wl的电压不太容易设置,设置过高或过低都容易降低编程效率。

技术实现思路

1、本发明所要解决的技术问题是提供一种闪存的操作方法,能提高编程效率。

2、为此,本发明提供的闪存的操作方法中,闪存包括多个存储单元;各所述存储单元都采用分离栅浮栅器件。

3、所述分离栅浮栅器件包括:对称设置的第一源漏区和第二源漏区,位于所述第一源漏区和所述第二源漏区之间的多个分离的具有浮栅的第一栅极结构,位于所述第一栅极结构之间的第二栅极结构;所述第一栅极结构中具有位于所述浮栅顶部的控制栅。

4、编程时所述第二栅极结构连接到字线编程电压,通过如下步骤设置所述字线编程电压:

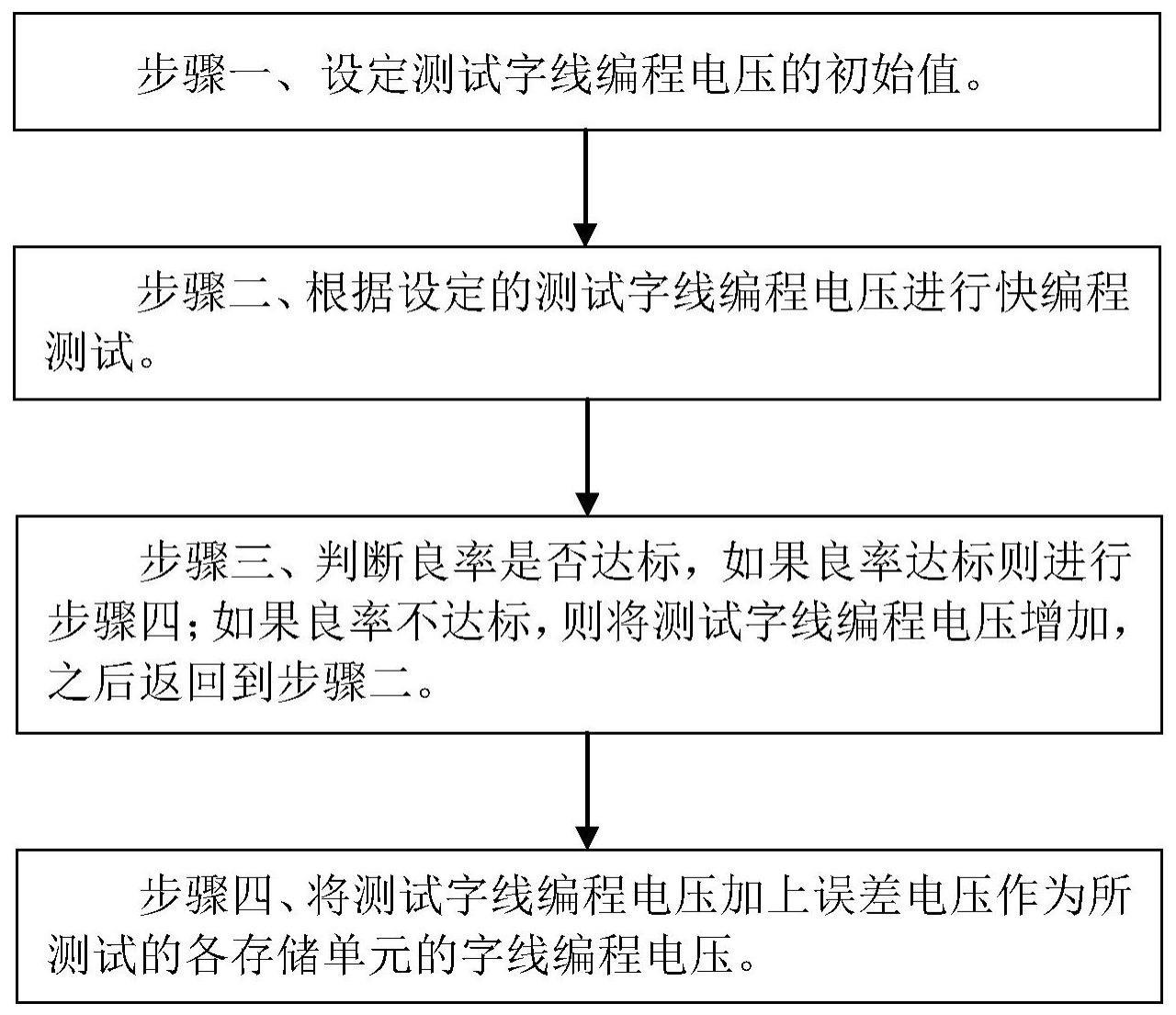

5、步骤一、设定所述测试字线编程电压的初始值。

6、步骤二、根据设定的所述测试字线编程电压进行快编程(fast program)测试,所述快编程测试一次同时实现对多个所述存储单元进行测试。

7、步骤三、判断所述快编程测试的结果的良率(yield)是否达标,如果良率达标则进行步骤四;如果良率不达标,则将所述测试字线编程电压增加,之后返回到步骤二。

8、步骤四、将良率达标时对应的所述测试字线编程电压加上误差电压作为所述快编程测试所测试的各所述存储单元的所述字线编程电压。

9、进一步的改进是,步骤二中,所述快编程测试采用晶圆芯片测试(chip probing,cp)的测试设备进行测试,各所述存储单元位于晶圆(wafer)上,所述晶圆上包括多个晶粒(die),各所述晶粒中包括多个所述存储单元。

10、进一步的改进是,步骤二中,所述快编程测试中一次测试实现对多个所述晶粒上的所述存储单元的测试。

11、进一步的改进是,步骤二中,所述快编程测试中一次测试的所述晶粒数量最大值达500个以上。

12、进一步的改进是,步骤二中,还包括设置所述快编程测试的测试标准且使所述快编程测试的测试标准严格度增加。

13、进一步的改进是,所述存储单元的阈值电压会随着温度增加而降低以及随着温度降低而增加,步骤四中,所述误差电压大于等于所述存储单元的阈值电压随温度变化产生的第一偏差。

14、进一步的改进是,所述存储单元的阈值电压会随着擦写次数的增加而增加,步骤四中,所述误差电压大于等于所述存储单元的阈值电压随擦写次数产生的第二偏差。

15、进一步的改进是,所述第一偏差和所述第二偏差都采用经验值。

16、进一步的改进是,所述第一偏差和所述第二偏差的经验值都通过对已有闪存的数据进行统计得到。

17、进一步的改进是,重复步骤一至步骤四,直至对所述晶圆上所有的所述存储单元的所述字线编程电压设置完成。

18、进一步的改进是,所述分离栅浮栅器件为双分离栅浮栅器件,所述第一栅极结构的数量为两个。

19、进一步的改进是,所述分离栅浮栅器件为n型器件,所述第一源漏区和所述第二源漏区都由n+区组成。

20、p型掺杂的沟道区位于所述第一源漏区和所述第二源漏区之间且被各所述第一栅极结构和所述第二栅极结构所覆盖,各所述第一栅极结构和所述第二栅极结构分别控制所覆盖的所述沟道区的区域段。

21、进一步的改进是,所述分离栅浮栅器件为p型器件,所述第一源漏区和所述第二源漏区都由p+区组成。

22、n型掺杂的沟道区位于所述第一源漏区和所述第二源漏区之间且被各所述第一栅极结构和所述第二栅极结构所覆盖,各所述第一栅极结构和所述第二栅极结构分别控制所覆盖的所述沟道区的区域段。

23、进一步的改进是,各所述第一栅极结构由隧穿介质层、所述浮栅、控制栅介质层和所述控制栅叠加而成。

24、各所述第二栅极结构由字线栅介质层和字线栅叠加而成。

25、进一步的改进是,所述浮栅的材料包括多晶硅,所述控制栅的材料包括多晶硅,所述字线栅的材料包括多晶硅。

26、本发明采用分离栅浮栅器件的闪存的存储单元的字线编程电压是通过测试得到,通过测试能使得字线编程电压在满足闪存良率的条件下取最小值以及同时能覆盖存储单元的阈值电压随使用条件变化产生的误差电压,其中,能覆盖存储单元的阈值电压随使用条件变化产生的误差电压则能保证在存储单元的阈值电压产生变化时字线编程电压依然保持足够大从而避免存储单元的阈值电压升高时使存储单元的编程效率降低;其中,能使得字线编程电压在满足闪存良率的条件下取最小值,则能避免字线编程电压过大时使存储单元的编程效率降低,所以,本发明能使字线编程电压的大小得到最佳设置,既不过大、也不过小,从而能避免字线编程电压在过大和过小时使存储单元的编程效率降低,从而能使存储单元的编程效率提高并最大化。

- 还没有人留言评论。精彩留言会获得点赞!