具有占空比校正器的半导体装置的制作方法

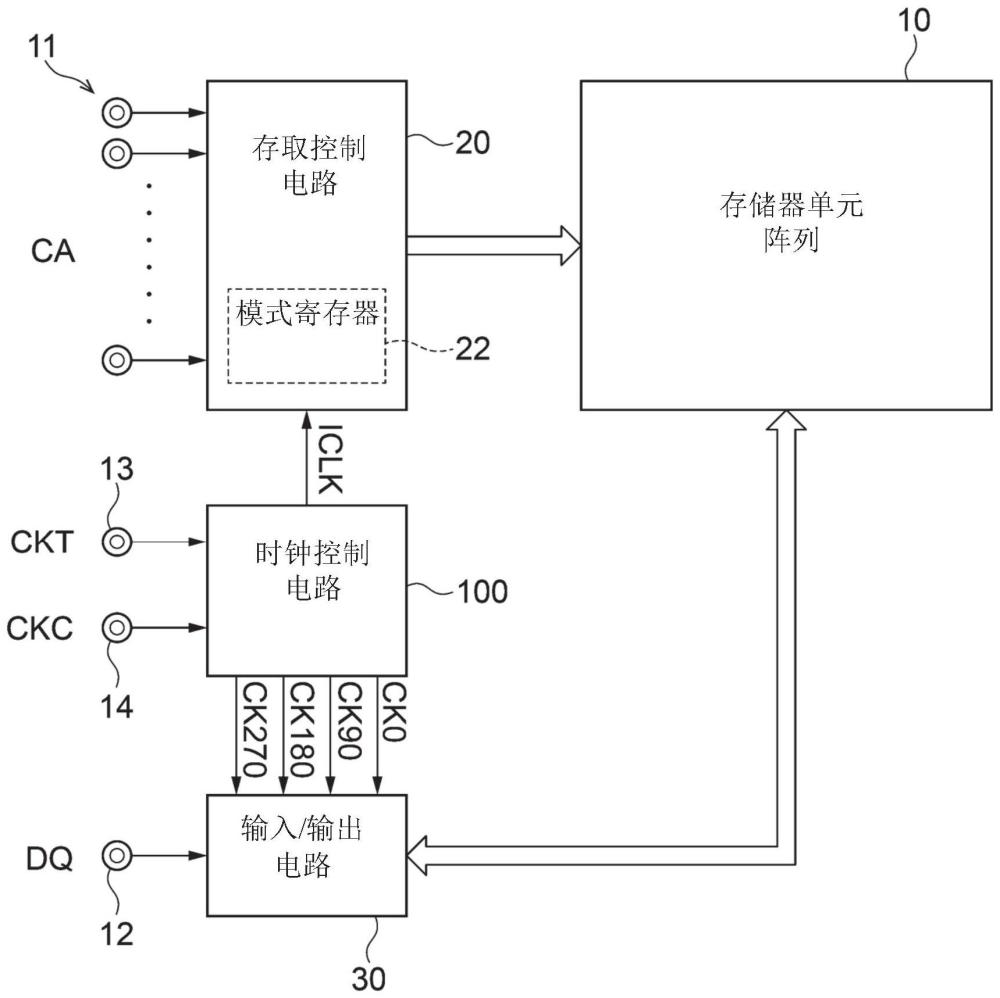

本申请涉及具有占空比校正器的半导体装置。

背景技术:

1、例如dram的半导体装置可包含用于将内部时钟信号的占空比保持在50%的占空比校正器(dcc)。然而,关于具有相当高频率的内部时钟信号,很难在保持原始频率的同时调整占空比。因此,关于具有相当高频率的内部时钟信号,有必要通过使用由对内部时钟信号进行分频产生的多个经分频时钟信号来调整占空比。

技术实现思路

1、本公开的实施例提供一种设备,其包括:第一输入节点,其被供应有第一时钟信号;第一时钟路径,其经配置以输出经延迟第一时钟信号,所述第一时钟路径包含串联耦合的第一及第二延迟元件;第二时钟路径,其经配置以输出额外的经延迟第一时钟信号,所述第二时钟路径包含串联耦合的第三及第四延迟元件;第一混频器电路,其经配置以内插所述经延迟第一时钟信号及所述额外的经延迟第一时钟信号以将经调整时钟信号再现为所述第一时钟信号;及控制电路,其经配置以利用彼此不同的第一、第二、第三及第四代码控制所述第一、第二、第三及第四延迟元件的延迟量。

2、本公开的另一实施例提供一种设备,其包括:第一反相器电路,其具有耦合到共同节点的输入节点及输出节点;第二反相器电路,其具有耦合到所述第一反相器电路的所述输出节点的输入节点及输出节点;第三反相器电路,其具有耦合到所述共同节点的输入节点及输出节点;第四反相器电路,其具有耦合到所述第三反相器电路的所述输出节点的输入节点及输出节点;混频器电路,其具有耦合到所述第二反相器电路的所述输出节点的第一输入节点及耦合到所述第四反相器电路的所述输出节点的第二输入节点;第一计数器电路;及第一解码器电路,其经配置以解码所述第一计数器电路的计数值以产生控制所述第一反相器电路的上拉能力的第一控制代码、控制所述第二反相器电路的下拉能力的第二控制代码、控制所述第三反相器电路的上拉能力的第三控制代码及控制所述第四反相器电路的下拉能力的第四控制代码。

3、本公开的又一实施例提供一种设备,其包括:第一输入节点,其被供应有第一时钟信号;第一时钟路径,其耦合在所述第一输入节点与第一输出节点之间且经配置以输出第二时钟信号,所述第一时钟路径包含串联耦合的多个第一可变延迟元件;第二时钟路径,其耦合在所述第一输入节点与第二输出节点之间且经配置以输出第三时钟信号,所述第二时钟路径包含串联耦合的多个第二可变延迟元件;及第一混频器电路,其经配置以依固定混频比内插所述第二及第三时钟信号以产生第四时钟信号。

技术特征:

1.一种设备,其包括:

2.根据权利要求1所述的设备,其中所述第一混频器电路的混频比是固定的。

3.根据权利要求2所述的设备,其中所述第一混频器电路的所述混频比是50%。

4.根据权利要求1所述的设备,其进一步包括第一计数器电路,

5.根据权利要求4所述的设备,

6.根据权利要求5所述的设备,

7.根据权利要求6所述的设备,

8.根据权利要求5所述的设备,

9.根据权利要求5所述的设备,

10.根据权利要求5所述的设备,其进一步包括第二计数器电路,

11.根据权利要求10所述的设备,

12.根据权利要求11所述的设备,

13.根据权利要求1所述的设备,其进一步包括:

14.一种设备,其包括:

15.根据权利要求14所述的设备,其中所述第一解码器电路经配置以当所述第一计数器电路的所述计数值从第一值改变为第二值时更新所述第一控制代码,而不更新所述第二、第三及第四控制代码。

16.根据权利要求15所述的设备,其中所述第一解码器电路经配置以当所述第一计数器电路的所述计数值从所述第二值改变为第三值时更新所述第三控制代码,而不更新所述第一、第二及第四控制代码。

17.根据权利要求16所述的设备,其中所述第一解码器电路经配置以当所述第一计数器电路的所述计数值从所述第三值改变为第四值时更新所述第二控制代码,而不更新所述第一、第三及第四控制代码。

18.根据权利要求14所述的设备,其进一步包括:

19.一种设备,其包括:

20.根据权利要求19所述的设备,其进一步包括:

技术总结

本申请涉及具有占空比校正器的半导体装置。本文中公开一种设备,其包含:第一输入节点,其被供应有第一时钟信号;第一时钟路径,其经配置以输出经延迟第一时钟信号,所述第一时钟路径包含串联耦合的第一及第二延迟元件;第二时钟路径,其经配置以输出额外的经延迟第一时钟信号,所述第二时钟路径包含串联耦合的第三及第四延迟元件;第一混频器电路,其经配置以内插所述经延迟第一时钟信号及所述额外的经延迟第一时钟信号以将经调整时钟信号再现为所述第一时钟信号;及控制电路,其经配置以利用彼此不同的第一、第二、第三及第四代码控制所述第一、第二、第三及第四延迟元件的延迟量。

技术研发人员:佐藤康夫

受保护的技术使用者:美光科技公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!