包括页缓冲器电路的存储器件的制作方法

本公开涉及存储器件,更具体地,涉及包括页缓冲器电路的存储器件。

背景技术:

1、近来,随着信息通信装置的多功能化趋势,已经出现对存储器件的大容量和高集成度的需求。存储器件可以包括用于在存储单元中存储数据或者从存储单元输出数据的页缓冲器,并且该页缓冲器可以包括诸如晶体管的半导体器件。

技术实现思路

1、本发明构思的各方面提供了一种通过调整发展时段的长度来识别多个编程状态的存储器件。

2、根据本发明构思的一个方面,一种存储器件包括:存储单元阵列,所述存储单元阵列包括多个存储单元;以及页缓冲器电路,所述页缓冲器电路包括多个页缓冲器单元和多个高速缓存锁存器,所述多个页缓冲器单元分别经由多条位线连接到所述多个存储单元,所述多个高速缓存锁存器分别对应于所述多个页缓冲器单元。所述多个页缓冲器单元均包括传输晶体管,所述传输晶体管连接到对应的感测节点并且根据传输控制信号被驱动,并且所述存储器件被配置为使得:在数据感测时段内,所述多个页缓冲器单元当中的选定页缓冲器单元的感测节点有效地连接到所述多个页缓冲器单元当中的未选页缓冲器单元的感测节点。

3、根据本发明构思的另一方面,一种存储器件包括:存储单元阵列,所述存储单元阵列包括多个存储单元;以及页缓冲器电路,所述页缓冲器电路包括n个页缓冲器单元和分别对应于所述n个页缓冲器单元的n个高速缓存锁存器,所述n个页缓冲器单元分别经由n条位线连接到所述多个存储单元,其中,n是小于或等于8的自然数。所述存储器件被配置为使得:在数据感测时段内,所述n个页缓冲器单元当中的感测所述多个存储单元中的至少一个存储单元中存储的数据的第一页缓冲器单元的感测节点,有效地电连接到所述n个页缓冲器单元当中的除所述第一页缓冲器单元以外的至少第二页缓冲器单元的感测节点。

4、根据本发明构思的另一方面,一种存储器件包括:存储单元区域,所述存储单元区域包括多个存储单元和第一金属焊盘;以及外围电路区域,所述外围电路区域包括第二金属焊盘并且通过所述第一金属焊盘和所述第二金属焊盘垂直地连接到所述存储单元区域,其中,所述外围电路区域包括页缓冲器电路,所述页缓冲器电路包括多个页缓冲器单元和多个高速缓存锁存器,所述多个页缓冲器单元沿第一水平方向布置并且分别经由多条位线连接到所述多个存储单元,所述多个高速缓存锁存器沿所述第一水平方向布置并且分别对应于所述多个页缓冲器单元。所述存储器件被配置为使得:在数据感测时段内,所述多个页缓冲器单元当中的感测所述多个存储单元当中的至少一个存储单元中存储的数据的第一页缓冲器单元的感测节点,有效地电连接到所述多个页缓冲器单元当中的至少第二页缓冲器单元的感测节点。

技术特征:

1.一种存储器件,所述存储器件包括:

2.根据权利要求1所述的存储器件,其中,包括在所述选定页缓冲器单元中的传输晶体管和包括在所述未选页缓冲器单元中的传输晶体管彼此串联连接,其中,所述存储器件被配置为使得在所述数据感测时段内,通过使每个传输晶体管接通来使所述选定页缓冲器单元的所述感测节点和所述未选页缓冲器单元的所述感测节点彼此有效地连接。

3.根据权利要求1所述的存储器件,所述存储器件被配置为使得:

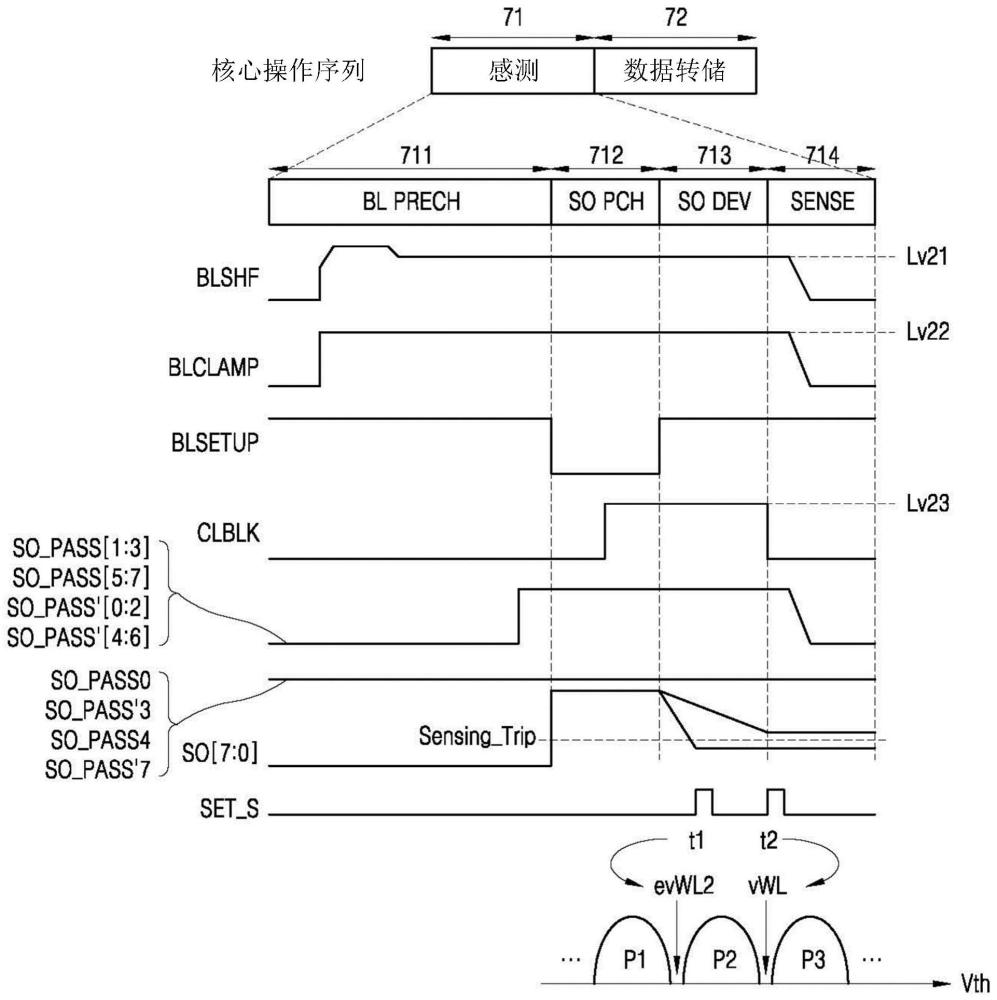

4.根据权利要求1所述的存储器件,其中,所述页缓冲器电路被配置为:执行多个读取操作,所述多个读取操作均包括所述选定页缓冲器单元的所述感测节点连接到所述选定页缓冲器单元的位线的发展时段;以及通过针对所述多个读取操作中的每一个读取操作调整所述发展时段的长度,来识别由所述多个存储单元形成的阈值电压分布中的至少三个阈值电压。

5.根据权利要求4所述的存储器件,其中,所述多个页缓冲器单元中的每一个页缓冲器单元包括感测锁存器,所述感测锁存器被配置为:当置位信号被激活时,基于所述感测节点的电平和参考电平,感测对应存储单元中存储的数据,并且

6.根据权利要求4所述的存储器件,其中,在所述多个读取操作当中,施加到与所述多个存储单元连接的字线的读取电压的大小是恒定的。

7.根据权利要求4所述的存储器件,其中,所述页缓冲器电路还被配置为:如果所述多个页缓冲器单元都是所述选定页缓冲器单元,将所述多条位线预充电到第一电平,以及如果所述多个页缓冲器单元中的一些页缓冲器单元是所述选定页缓冲器单元,而所述多个页缓冲器单元中的其他页缓冲器单元是所述未选页缓冲器单元,将所述多条位线预充电到第二电平,并且所述第二电平大于所述第一电平。

8.根据权利要求1所述的存储器件,所述存储器件被配置为使得,在所述数据感测时段内,所述多个页缓冲器单元当中与第一选定页缓冲器单元的感测节点有效连接的未选页缓冲器单元的感测节点的数目等于所述多个页缓冲器单元当中与第二选定页缓冲器单元的感测节点有效连接的未选页缓冲器单元的感测节点的数目。

9.根据权利要求1所述的存储器件,所述存储器件被配置为使得:当所述多个页缓冲器单元当中的与所述多个高速缓存锁存器相邻的页缓冲器单元是所述选定页缓冲器单元时,在所述数据感测时段内,所述选定页缓冲器单元和所述多个高速缓存锁存器彼此电绝缘。

10.根据权利要求1所述的存储器件,其中,所述选定页缓冲器单元包括主锁存器,所述主锁存器存储所述多个存储单元当中的至少一个存储单元中存储的数据,并且所述主锁存器被配置为使得:在数据传送时段内,位于所述主锁存器与对应于所述选定页缓冲器单元的高速缓存锁存器之间的数据路径上的至少一个传输晶体管被接通。

11.一种存储器件,所述存储器件包括:

12.根据权利要求11所述的存储器件,其中,所述n个页缓冲器单元均包括传输晶体管,所述传输晶体管连接到对应感测节点并且根据传输控制信号被驱动,并且

13.根据权利要求12所述的存储器件,其中,所述第一页缓冲器单元包括主锁存器,所述主锁存器存储所述至少一个存储单元中存储的数据,并且

14.根据权利要求11所述的存储器件,其中,所述页缓冲器电路还被配置为:如果所述n个页缓冲器单元都是所述第一页缓冲器单元,将所述n条位线中的每一条位线预充电到第一电平,以及如果所述n个页缓冲器单元中的一些页缓冲器单元是所述第一页缓冲器单元,而所述n个页缓冲器单元中的其他页缓冲器单元是所述第二页缓冲器单元,将所述n条位线中的每一条位线预充电到第二电平,并且

15.根据权利要求11所述的存储器件,其中,所述页缓冲器电路还被配置为:执行多个读取操作,所述多个读取操作均包括每个第一页缓冲器单元的感测节点连接到每个第一页缓冲器单元的对应位线的发展时段;以及通过针对所述多个读取操作中的每一个读取操作调整所述发展时段的长度,来识别由所述多个存储单元形成的阈值电压分布中的至少三个阈值电压。

16.根据权利要求15所述的存储器件,其中,所述第一页缓冲器单元包括感测锁存器,所述感测锁存器被配置为:当置位信号被激活时,基于所述感测节点的电平和参考电平,感测对应存储单元中存储的数据,并且

17.一种存储器件,所述存储器件包括:

18.根据权利要求17所述的存储器件,其中,所述多个页缓冲器单元均包括传输晶体管,所述传输晶体管连接到对应感测节点并且根据传输控制信号被驱动,并且

19.根据权利要求17所述的存储器件,所述存储器件被配置为使得:在所述数据感测时段内,所述多个页缓冲器单元当中的感测所述多个存储单元当中的至少一个存储单元中存储的数据的第三页缓冲器单元的感测节点电连接到所述多个页缓冲器单元当中的至少第四页缓冲器单元的感测节点,并且

20.根据权利要求17所述的存储器件,其中,所述页缓冲器电路被配置为:通过针对多个读取操作中的每一个读取操作调整期间所述第一页缓冲器单元的所述感测节点连接到所述第一页缓冲器单元的位线的发展时段的长度,来识别由所述多个存储单元形成的阈值电压分布中的至少三个阈值电压,并且

技术总结

一种包括页缓冲器电路的存储器件包括:存储单元阵列,所述存储单元阵列包括多个存储单元;以及页缓冲器电路,所述页缓冲器电路包括多个页缓冲器单元和多个高速缓存锁存器,所述多个页缓冲器单元分别经由多条位线连接到所述多个存储单元,所述多个高速缓存锁存器分别对应于所述多个页缓冲器单元。所述多个页缓冲器单元均包括传输晶体管,所述传输晶体管连接到对应的感测节点并且根据传输控制信号被驱动,并且所述存储器件被配置为使得:在数据感测时段内,所述多个页缓冲器单元当中的选定页缓冲器单元的感测节点有效地连接到所述多个页缓冲器单元当中的未选页缓冲器单元的感测节点。

技术研发人员:曹溶成,姜仁昊,金寅洙,申载厚

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/2/25

- 还没有人留言评论。精彩留言会获得点赞!