具有分段单元位线的半导体存储器器件的制作方法

实施例涉及一种半导体存储器器件。更具体地,实施例涉及具有存储器单元阵列和位线感测放大器(blsa)在平面中重叠的结构的半导体存储器器件。

背景技术:

1、半导体存储器器件可以分为易失性存储器器件和非易失性存储器器件。当电源关闭时,易失性存储器器件丢失存储的数据,而非易失性存储件即使在电源关闭时也保留存储的数据。

2、正在开发各种单元结构以改进半导体存储器器件的集成度。

3、在本背景技术部分中公开的上述信息仅用于增强对本发明背景的理解,因此其可能包含不构成本领域普通技术人员在国内已知的现有技术的信息。

技术实现思路

1、本发明的示例性实施例的特征是通过减少单元位线的电容来增加电荷共享电压,并且减少位线感测放大器的功耗。

2、示例性实施例的另一特征是通过使得未配对且未在存储器器件的外围使用的单元位线可用来提高存储器器件的容量。

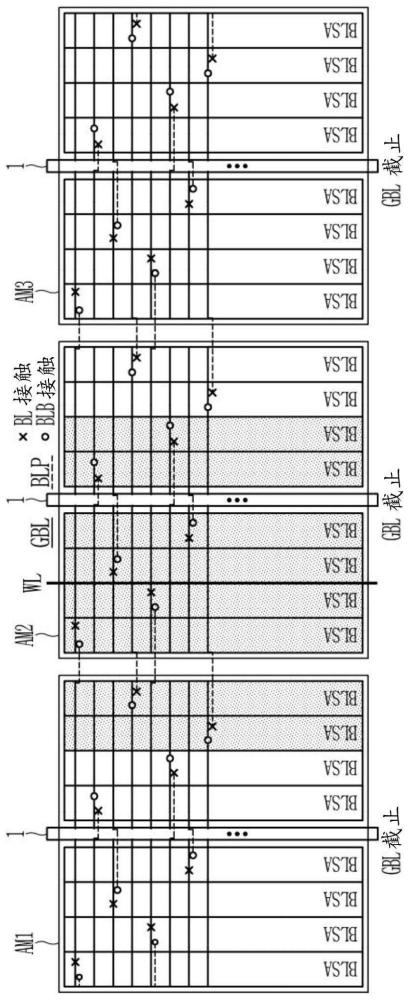

3、根据示例性实施例的半导体存储器器件包括:存储器单元阵列,其位于第一层中,并且包括至少一个字线、至少一个单元位线和位于至少一个字线和至少一个单元位线交叉的区域中的至少一个存储器单元。半导体存储器器件还包括位于不同于第一层的第二层中的至少一个位线感测放大器,并且位线感测放大器连接到与至少一个单元位线连接的至少一个位线,以及连接到与至少一个位线相对应的至少一个互补位线。位线感测放大器检测存储在至少一个存储器单元中的数据。至少一个单元位线中的每一个被分割为至少两个部分,并且至少两个部分别连接到与至少一个位线感测放大器连接的至少一个位线和至少一个互补位线。

4、至少一个存储器单元可以或可以不位于在垂直方向上与至少一个单元位线中的每一个被分割为彼此分离的区域重叠的区域中。

5、至少一个单元位线中的每一个可以被分割为三个或更多部分以彼此分离,并且在其中至少一个单元位线的每一个可以被分割为彼此分离的区域包括第一分离区域和第二分离区域,以及至少一个存储器单元可以位于在垂直方向上与第一分离区域重叠的区域中,并且至少一个存储器单元可以不位于在垂直方向上与第二分离区域重叠的区域中。

6、至少一个存储器单元可以包括垂直沟道晶体管,并且垂直沟道晶体管的沟道可以包括铟镓锌氧化物(igzo)。

7、至少两个部分可以形成在与连接到至少一个位线感测放大器的至少一个位线和至少一个互补位线不同的层上,第一绝缘层介于其间,并且通过穿透第一绝缘层的通孔连接。

8、至少一个位线感测放大器可以包括连接布线层,并且可以经由连接布线层在至少一个位线感测放大器与至少一个位线和至少一个互补位线之间进行连接。

9、至少一个位线和至少一个互补位线可以形成在与连接布线层不同的层中,第二绝缘层位于其间,并且通过穿透第二绝缘电层的通孔连接到连接布线层。

10、根据示例性实施例的半导体存储器器件包括:存储器单元阵列,其位于第一层中,并且包括至少一个字线、至少一个单元位线和位于至少一个字线和至少一个单元位线交叉的区域中的至少一个存储器单元;虚拟(dummy)单元阵列,其位于第一层中并且位于存储器单元阵列的至少一个周向(circumferential)侧,所述虚拟单元阵列包括至少一个虚拟字线、至少一个虚拟单元位线以及位于至少一个虚拟字线和至少一个虚拟单元位线交叉的区域中的至少一个虚拟存储器单元;以及位于不同于第一层的第二层中的至少一个位线感测放大器,并且位线感测放大器连接到与至少一个单元位线连接的至少一个位线以及与至少一个位线相对应的至少一个互补位线。至少一个位线感测放大器检测存储在至少一个存储器单元中的数据。至少一个位线感测放大器包括位于存储器单元阵列与虚拟单元阵列之间的边界处的边缘位线感测放大器。连接到边缘位线感测放大器的至少一个位线和至少一个互补位线分别连接到至少一个单元位线和至少一个虚拟单元位线。

11、至少一个虚拟单元位线可以包括奇数编号的虚拟单元位线和偶数编号的虚拟单元位线,并且彼此相邻的奇数编号的虚拟单元位线的一个和偶数编号虚拟单元位线的一个通过开关彼此连接。导通信号可以总是施加到虚拟字线中的至少一个。开关在电荷共享之后在边缘位线感测放大器被激活之后导通,并且在均衡信号被施加到边缘线感测放大器之后关断。

12、至少一个虚拟单元位线可以包括奇数编号的虚拟单元位线和偶数编号的虚拟单元位线,并且彼此相邻的奇数编号的虚拟单元位线中的一个和偶数编号的虚拟单元位线的一个可以彼此连接。导通信号可以总是施加到虚拟字线中的至少一个。

13、连接到边缘位线感测放大器的单元位线可以是奇数单元位线或偶数单元位线。

14、边缘位线感测放大器可以分别位于存储器单元阵列的列解码器侧的边缘和相对的边缘。

15、至少一个存储器单元可以包括垂直沟道晶体管,并且垂直沟道晶体管的沟道可以包括铟镓锌氧化物(igzo)。

16、至少一个单元位线和至少一个虚拟单元位线可以形成在与连接到边缘位线感测放大器的至少一个位线和至少一个互补位线不同的层中,其中第一绝缘层位于其间,并且通过穿透第一绝缘层的通孔彼此连接。

17、根据本发明实施例的半导体存储器器件可以通过将单元位线分割成多个并减小单元位线的电容来增加电荷共享电压,并降低位线感测放大器的功耗。

18、此外,根据本发明实施例的半导体存储器器件可以通过设置虚拟单元阵列来提高存储器器件的容量,从而使得能够使用由于在存储器器件的外围上未配对而未使用的单元位线。

技术特征:

1.一种半导体存储器器件,包括:

2.根据权利要求1所述的半导体存储器器件,其中,至少一个存储器单元位于在垂直方向上与其中至少一个单元位线中的每一个被分割为彼此分离的区域重叠的区域中。

3.根据权利要求1所述的半导体存储器器件,其中,至少一个存储器单元不位于在垂直方向上与其中至少一个单元位线中的每一个被分割为彼此分离的区域重叠的区域中。

4.根据权利要求1所述的半导体存储器器件,其中

5.根据权利要求1所述的半导体存储器器件,其中,至少一个存储器单元包括垂直沟道晶体管。

6.根据权利要求5所述的半导体存储器器件,其中,垂直沟道晶体管的沟道包括铟镓锌氧化物(igzo)。

7.根据权利要求1所述的半导体存储器器件,其中,至少两个部分形成在与连接到至少一个位线感测放大器的至少一个位线和至少一个互补位线不同的层上,第一绝缘层介于其间,并且所述至少两个部分通过穿透第一绝缘层的通孔连接。

8.根据权利要求7所述的半导体存储器器件,其中,至少一个位线感测放大器包括连接布线层,并且经由连接布线层在至少一个位线感测放大器与至少一个位线和至少一个互补位线之间进行连接。

9.根据权利要求8所述的半导体存储器器件,其中,至少一个位线和至少一个互补位线形成在与连接布线层不同的层中,第二绝缘层位于其间,并且所述至少一个位线和至少一个互补位线通过穿透第二绝缘电层的通孔连接到连接布线层。

10.一种半导体存储器器件,包括:

11.根据权利要求10所述的半导体存储器器件,其中,至少一个虚拟单元位线包括奇数编号的虚拟单元位线和偶数编号的虚拟单元位线,并且彼此相邻的奇数编号的虚拟单元位线的一个和偶数编号虚拟单元位线的一个通过开关彼此连接。

12.根据权利要求11所述的半导体存储器器件,其中,导通信号总是施加到虚拟字线中的至少一个。

13.根据权利要求11所述的半导体存储器器件,其中,开关在电荷共享之后在边缘位线感测放大器被激活之后导通,并且在均衡信号被施加到边缘线感测放大器之后关断。

14.根据权利要求10所述的半导体存储器器件,其中,至少一个虚拟单元位线包括奇数编号的虚拟单元位线和偶数编号的虚拟单元位线,并且彼此相邻的奇数编号的虚拟单元位线中的一个和偶数编号的虚拟单元位线的一个彼此连接。

15.根据权利要求14所述的半导体存储器器件,其中,导通信号总是施加到虚拟字线中的至少一个。

16.根据权利要求10所述的半导体存储器器件,其中,连接到边缘位线感测放大器的单元位线是奇数单元位线或偶数单元位线。

17.根据权利要求10所述的半导体存储器器件,其中,边缘位线感测放大器分别位于存储器单元阵列的列解码器侧的边缘和相对的边缘。

18.根据权利要求10所述的半导体存储器器件,其中,至少一个存储器单元包括垂直沟道晶体管。

19.根据权利要求18所述的半导体存储器器件,其中,垂直沟道晶体管的沟道包括铟镓锌氧化物(igzo)。

20.根据权利要求10所述的半导体存储器器件,其中,至少一个单元位线和至少一个虚拟单元位线形成在与连接到边缘位线感测放大器的至少一个位线和至少一个互补位线不同的层中,其中第一绝缘层位于其间,并且所述至少一个单元位线和至少一个虚拟单元位线通过穿透第一绝缘层的通孔彼此连接。

技术总结

半导体存储器器件包括:存储器单元阵列,其位于第一层中,并且包括字线、单元位线和位于字线和单元位线交叉的区域中的存储器单元;以及位于不同于第一层的第二层中的至少一个位线感测放大器。位线感测放大器连接到与单元位线连接的位线以及连接到与位线相对应的互补位线。位线感测放大器检测存储在至少一个存储器单元中的数据。至少一个单元位线中的每一个被分割为两个或更多个部分,并且该两个或更多个部分别连接到与位线感测放大器连接的位线和互补位线。

技术研发人员:林周元,徐宁焄,金尚玧

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/2/25

- 还没有人留言评论。精彩留言会获得点赞!