用于改进DDR存储器装置中的写入前同步码的系统和方法与流程

本公开涉及用于存储器装置的电路系统,且更确切地,涉及用于在例如双数据速率(ddr)存储器装置等存储器装置的数据写入期间可以使用的写入前同步码的系统和方法。

背景技术:

1、随机存取存储器(ram)装置,例如可以在电气装置中用于提供数据处理和/或存储的那些的随机存取存储器装置,可以提供对存储在装置的存储器电路系统中的可寻址数据的直接可用性。例如同步动态ram(sdram)装置的某些ram装置可以例如具有多个存储器存储体,所述存储器存储体具有许多可寻址存储器元件。基于选通的数据总线可以与某些选通信号结合使用,以提供对可寻址存储器元件的读写存取。数据选通信号(例如,dqs)可以包含可编程前同步码部分、切换部分和后同步码部分。可编程前同步码部分可以为接收装置提供可编程时序窗口,以在选通信号上存在已知/有效电平时启用数据捕获电路系统,从而避免数据捕获电路系统的错误触发。在可编程前同步码部分之后以及在切换部分期间,dqs将与时钟信号(clk)一起通过高电平和低电平转换进行切换,以传输数据。然后最后一次转换之后的时间被称为后同步码部分。

2、clk与dqs选通之间的相位差(tdqss)可能会导致写入突发开始时出现域交叉问题。也就是说,应该保持与外部数据选通信号dqs同步的信号的激活周期,直到内部时钟被激活以确保适当的功能为止。当发出的写入命令如此靠近以致编程的写入前同步码不完整时,此域交叉问题会变得更加严重,从而减少了解决域交叉所需的时间窗口。改进用于可编程写入前同步码的技术将是有益的。

3、本发明的实施例可针对于上文所阐述的一或多个问题。

技术实现思路

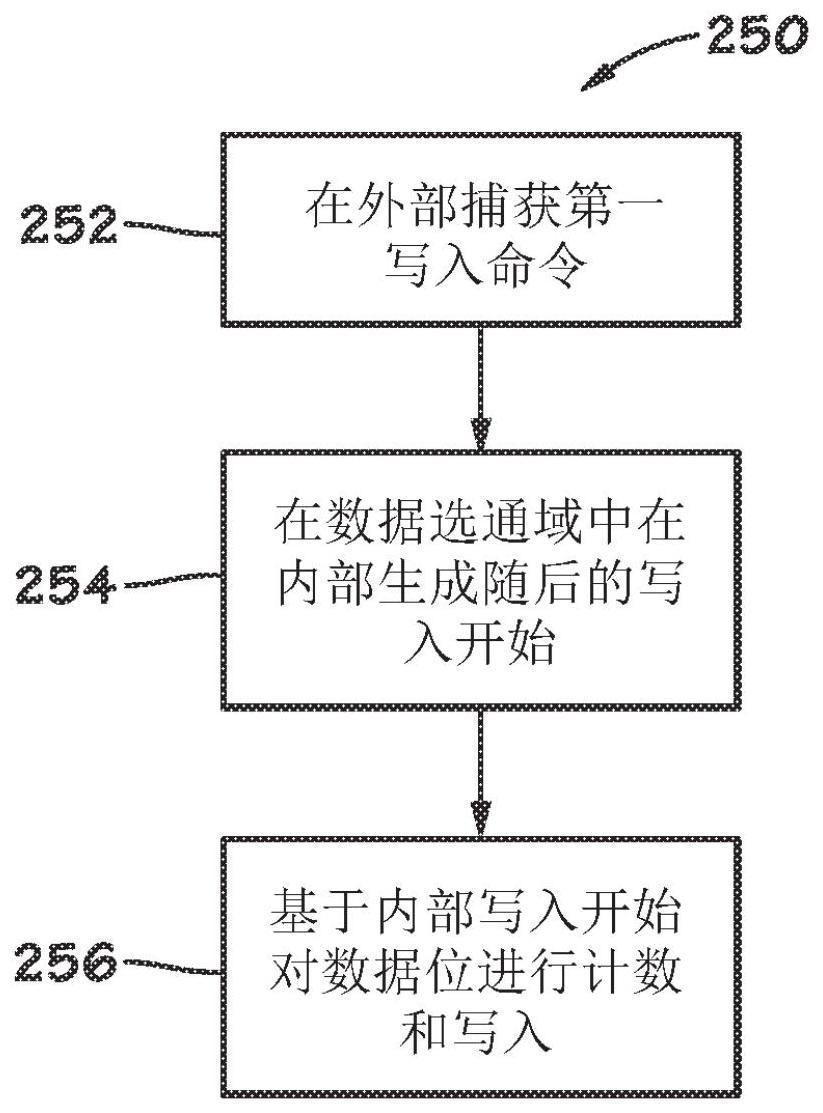

1、一方面,本公开提供一种存储器装置,其包括:数据写入电路系统,其经配置以:捕获经由外部输入/输出i/o接口接收的第一写入命令;在捕获所述第一写入命令后,在数据选通dqs域中生成第一内部写入开始internalwrstart;以及基于所述第一internalwrstart将第一一或多个数据位写入至少一个存储器存储体中,其中所述第一internalwrstart包括用于开始在所述存储器装置内部生成的存储器写入的命令。

2、另一方面,本公开提供一种方法,其包括:经由存储器装置捕获第一写入命令;经由所述存储器装置在捕获所述第一写入命令后在数据选通dqs域中生成第一内部写入开始internalwrstart;以及基于所述第一internalwrstart经由所述存储器装置将第一一或多个数据位写入至少一个存储器存储体中,其中所述第一internalwrstart包括用于开始在所述存储器装置内部生成的存储器写入的命令。

技术特征:

1.一种存储器装置,其包括:

2.根据权利要求1所述的存储器装置,其中所述数据写入电路系统包括写入命令转写入命令计数器系统,其经配置以基于时钟clk波形和所述第一写入命令来生成部分写入前同步码信号partialwpre,并且其中所述数据写入电路系统经配置以使用所述partialwpre在内部且在所述dqs域中生成所述第一internalwrstart。

3.根据权利要求2所述的存储器装置,其中所述数据写入电路系统包括数据选通周期计数器,其经配置以基于数据选通波形和所述partialwpre来生成所述第一internalwrstart,并且其中所述数据写入电路系统经配置以将所述第一internalwrstart、所述partialwpre和经移位写入命令组合成组合信号,所述组合信号用于将所述第一一或多个数据位写入所述至少一个存储器存储体中。

4.根据权利要求3所述的存储器装置,其中所述数据写入电路系统包括锁存器系统,其经配置以使用所述组合信号和所述数据选通波形来生成捕获写入命令信号,所述捕获写入命令信号用于将所述第一一或多个数据位写入所述至少一个存储器存储体中。

5.根据权利要求3所述的存储器装置,其中所述数据写入电路系统包括移位器系统,其经配置以将所述第一写入命令相移为所述经移位写入命令。

6.根据权利要求1所述的存储器装置,其中所述数据写入电路系统经配置以在写入所述第一一或多个数据位之后在所述dqs域中生成第二internalwrstart,且应用所述第二internalwrstart来写入第二一或多个数据位。

7.根据权利要求1所述的存储器装置,其中所述数据写入电路系统经配置以在所述第一内部写入开始之后在内部生成所有后续写入开始。

8.根据权利要求1所述的存储器装置,其中所述数据写入电路系统经配置以在存在部分写入前同步码的情况下写入所述第一一或多个数据位,所述部分写入前同步码包括小于完整写入前同步码的时间窗口。

9.根据权利要求8所述的存储器装置,其包括具有所述数据写入电路系统的双数据速率类型五ddr5存储器装置,并且其中所述完整写入前同步码包括具有1、2、3或更多时钟周期的可编程写入前同步码。

10.一种方法,其包括:

11.根据权利要求10所述的方法,其中经由所述存储器装置生成所述第一internalwrstart包括:经由包含在所述存储器装置中的写入命令转写入命令计数器系统基于时钟clk波形和所述第一写入命令来生成部分写入前同步码信号partialwpre。

12.根据权利要求11所述的方法,其中将所述第一一或多个数据位写入所述至少一个存储器存储体中包括:将所述第一internalwrstart、所述partialwpre和相移写入命令组合成组合信号。

13.根据权利要求12所述的方法,其包括经由所述组合信号锁存数据选通波形,以将所述第一一或多个数据位写入所述至少一个存储器存储体中。

14.根据权利要求10所述的方法,其包括在写入所述第一一或多个数据位后在所述dqs域中生成第二intemalwrstart,并且应用所述第二internalwrstart以写入第二一或多个数据位。

15.根据权利要求10所述的方法,其包括在所述第一内部写入开始之后在内部生成所有后续写入开始。

技术总结

本公开涉及用于改进DDR存储器装置中的写入前同步码的系统和方法。一种存储器装置包含数据写入电路系统。所述数据写入电路系统经配置以捕获经由外部输入/输出I/O接口接收的第一写入命令。所述数据写入电路系统进一步经配置以在捕获所述第一写入命令后,在数据选通DQS域中生成第一内部写入开始InternalWrStart。所述数据写入电路系统另外经配置以基于所述第一InternalWrStart将第一一或多个数据位写入至少一个存储器存储体中,其中在所述存储器装置内部生成所述第一InternalWrStart。

技术研发人员:D·B·彭妮,D·R·布朗,G·L·霍韦

受保护的技术使用者:美光科技公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!