半导体器件及电子设备的制作方法

本技术涉及半导体,具体而言,本技术涉及一种半导体器件及电子设备。

背景技术:

1、存储器是计算机中数据存放的主要介质,随着存储技术的发展和进步,存储器件不断朝着小型化、更高器件密度、高集成度的方向发展。

技术实现思路

1、本技术提出一种半导体器件及电子设备,通过位线共享和字线共享,最大程度减少外围电路面积;使存储部、走线部和外围电路部三个部分位于不同层的相同面积下,无需占用其他多余面积,可节省走线和外围电路面积,提高器件密度和集成度。

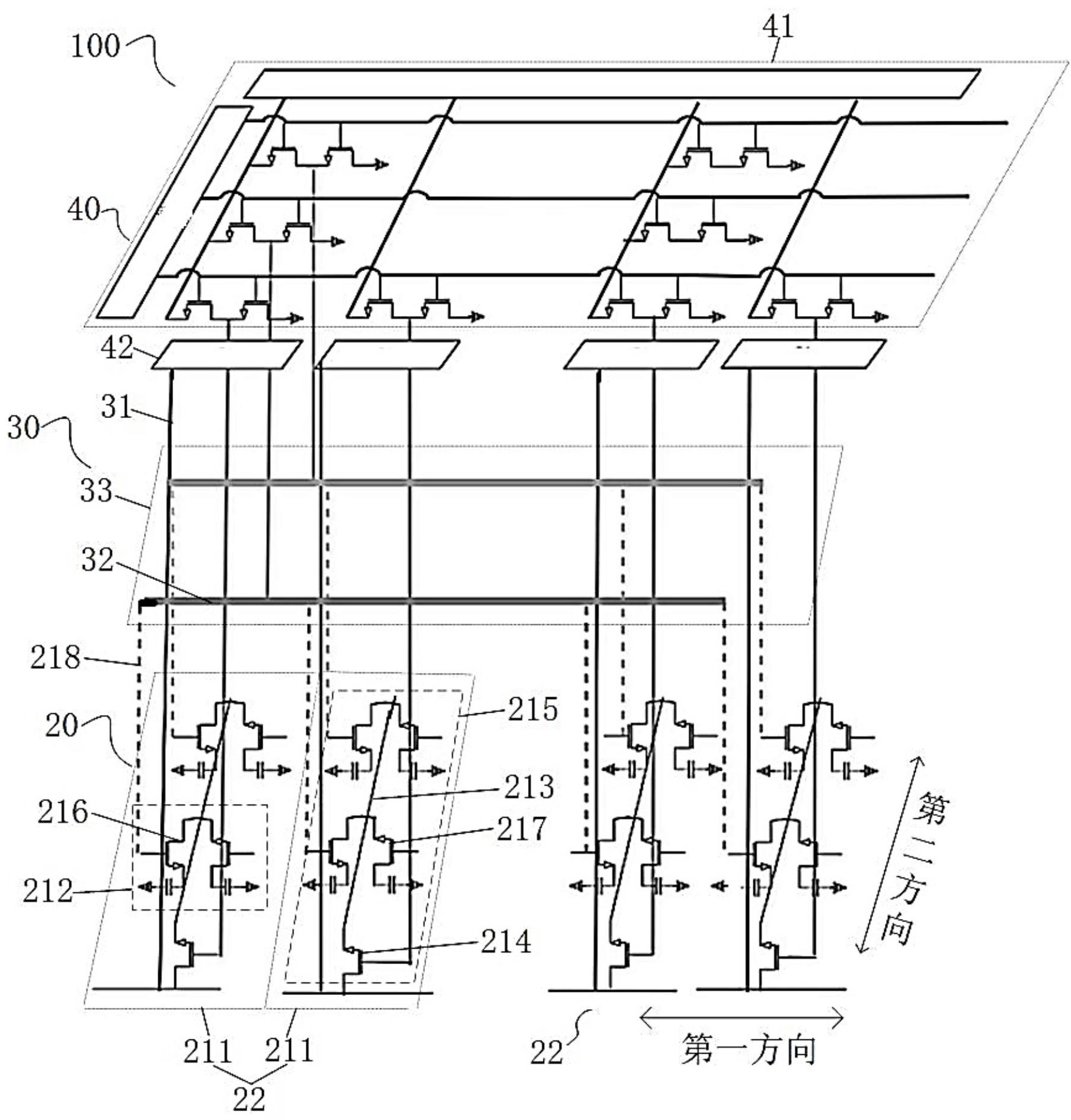

2、第一个方面,本技术实施例提供了一种半导体器件,包括:衬底以及设置在衬底一侧的存储部、走线部和外围电路部,

3、在垂直于衬底的方向上,存储部、走线部和外围电路部的位置不同;

4、存储部包括至少两个子存储阵列,至少两个子存储阵列沿平行于衬底的第一方向依次排布;

5、子存储阵列包括至少一个存储单元,存储单元包括晶体管;走线部包括至少一个共享字线;

6、至少两个子存储阵列中,位于不同子存储阵列的存储单元的晶体管的栅极与同一共享字线电连接,共享字线与外围电路部连接。

7、在本技术一些可选的实施方式中,位于不同子存储阵列的相同的相应位置的存储单元的晶体管的栅极与同一共享字线电连接。

8、在本技术一些可选的实施方式中,走线部还包括至少两个共享位线,至少两个共享位线与至少两个子存储阵列一一对应连接。

9、在本技术一些可选的实施方式中,子存储阵列包括本地位线、选通结构和多个存储单元,多个存储单元沿平行于衬底的第二方向依次排布;

10、本地位线分别与多个存储单元的晶体管的源极或漏极电连接,且本地位线与选通结构电连接,以形成存储单元列;

11、选通结构与对应的共享位线电连接;

12、其中,第二方向与第一方向呈夹角设置。

13、在本技术一些可选的实施方式中,与同一个子存储阵列中的多个存储单元一一对应连接的多个共享字线位于同一走线层,该走线层平行于衬底,在该走线层内,多个共享字线沿第二方向依次排布。

14、在本技术一些可选的实施方式中,子存储阵列具有至少两个存储单元列,至少两个存储单元列沿第一方向依次排布;

15、同一子存储阵列的至少两个存储单元列均与对应的同一共享位线电连接;

16、同一子存储阵列的至少两个存储单元列中,与不同存储单元列分别连接的共享字线位于不同走线层,与至少两个存储单元列分别连接的至少两个走线层沿垂直于衬底的方向依次排布。

17、在本技术一些可选的实施方式中,存储单元包括第一晶体管和第二晶体管,第一晶体管的源极或漏极和第二晶体管的源极或漏极均与本地位线电连接;

18、与存储单元对应连接的共享字线包括第一子共享字线和第二子共享字线,第一子共享字线与第一晶体管的栅极电连接,第二子共享字线与第二晶体管的栅极电连接;

19、第一子共享字线和第二子共享字线位于同一走线层,在该走线层内,第一子共享字线和第二子共享字线沿第二方向间隔排布且在第一方向上错开设置。

20、在本技术一些可选的实施方式中,至少两个子存储阵列位于同一存储阵列层,存储部具有多个存储阵列层,多个存储阵列层沿垂直于衬底的方向依次层叠设置;

21、多个存储阵列层中,在衬底上的正投影交叠的各子存储阵列与同一共享位线电连接;和/或,

22、多个存储阵列层中,在衬底上的正投影交叠的各存储单元的晶体管与同一共享字线电连接。

23、在本技术一些可选的实施方式中,外围电路部包括字线驱动器电路,共享字线与字线驱动器电路电连接;

24、字线驱动器电路在衬底上的正投影、共享字线在衬底上的正投影与对应连接的存储单元在衬底上的正投影交叠。

25、在本技术一些可选的实施方式中,子存储阵列的数量为多个,沿第一方向依次排布的多个子存储阵列划分为至少两个存储阵列;

26、同一存储阵列的各子存储阵列中位于相同的相应位置的存储单元的晶体管的栅极与同一共享字线电连接;

27、位于不同存储阵列的子存储阵列中存储单元的晶体管的栅极与同一共享字线电连接;或者,

28、位于不同存储阵列的子存储阵列中存储单元的晶体管的栅极分别与不同共享字线电连接。

29、在本技术一些可选的实施方式中,位于不同存储阵列的子存储阵列中相同的相应位置的存储单元的晶体管的栅极分别与不同共享字线电连接;

30、字线驱动器电路包括至少两个子字线驱动器电路,至少两个子字线驱动器电路与至少两个存储阵列一一对应连接;和/或,

31、与位于不同存储阵列的子存储阵列中相同的相应位置的存储单元的晶体管的栅极,分别电连接的至少两个共享字线位于同一走线层,或者分别位于不同走线层。

32、在本技术一些可选的实施方式中,外围电路部包括字线驱动器电路,与同一个存储单元对应连接的第一子共享字线和第二子共享字线分别连接至同一个字线驱动器电路的不同位置。

33、在本技术一些可选的实施方式中,外围电路部还包括与至少两个共享位线一一对应连接的至少两个感应放大器电路;

34、感应放大器电路在衬底上的正投影与对应连接的共享位线在衬底上的正投影交叠。

35、在本技术一些可选的实施方式中,沿远离衬底的方向,存储部、走线部和外围电路部依次设置;或者,

36、沿远离衬底的方向,外围电路部、走线部和存储部依次设置。

37、第二个方面,本技术实施例提供了一种电子设备,包括上述的半导体器件。

38、本技术实施例提供的技术方案带来的有益技术效果包括:

39、本技术实施例中,在垂直于衬底的方向上,存储部、走线部和外围电路部的位置不同,可以在垂直于衬底的方向上,将存储部、走线部和外围电路部分别布置在不同位置,便于合理分配空间,减小占用面积。存储部的至少两个子存储阵列沿平行于衬底的第一方向依次排布,便于对至少两个子存储阵列进行布置,能够避免干涉。

40、本技术实施例中,各子存储阵列均包括至少一个存储单元,走线部包括至少一个共享字线,至少一个共享字线与各子存储阵列中至少一个存储单元一一对应,且至少两个子存储阵列中,位于不同子存储阵列的存储单元的晶体管的栅极与同一共享字线电连接,即存储部的至少两个子存储阵列中,位于不同子存储阵列的存储单元的晶体管的栅极可共用一个共享字线,并可通过共用的这一条共享字线与外围电路部连接。本技术实施例通过共享字线方式,可以大幅减少走线和降低外围电路面积,不占用多余面积,提高器件密度和集成度。

41、本技术实施例中,走线部的至少两个共享位线与至少两个子存储阵列一一对应连接,不同子存储阵列分别与不同共享位线一一对应连接,通过共享位线能够读取对应的子存储阵列中存储单元的数据或者将数据写入至对应子存储阵列中的存储单元。多个存储阵列层中,在衬底上的正投影交叠的各子存储阵列与同一共享位线电连接,即位于不同存储阵列层的子存储阵列中,在衬底上的正投影交叠的各子存储阵列可以共用同一个共享位线。多个存储阵列层中,在衬底上的正投影交叠的各存储单元的晶体管与同一共享字线电连接,即位于不同存储阵列层的子存储阵列的存储单元中,在衬底上的正投影交叠的各存储单元的晶体管可以共用同一个共享字线。通过这种设计方式,可以使半导体器件的多个存储阵列层、多个子存储阵列、多个存储单元能够同时工作,实现位线共享和字线共享,从而最大程度减少外围电路面积。并且,当存储部为具有多个存储阵列层的三维结构时,不影响走线部和外围电路部排布。

42、字线驱动器电路在衬底上的正投影、共享字线在衬底上的正投影与对应的存储单元在衬底上的正投影交叠,使字线驱动器电路、共享字线与对应的存储单元三个部分位于不同层的相同面积下,不多余占用面积,节省走线和外围电路面积;并且,本技术实施例通过共享字线方式,可大幅节省字线驱动器电路面积,不占用多余面积,提高器件密度和集成度。

43、感应放大器电路在衬底上的正投影与对应连接的共享位线在衬底上的正投影交叠,使感应放大器电路与对应连接的共享位线位于不同层的相同面积下,不多余占用面积,节省走线和外围电路面积。

44、通过该走线方法和结构,使存储部、走线部和外围电路部三个部分位于不同层的相同面积下,无需占用其他多余面积,可节省走线和外围电路面积。

45、本技术附加的方面和优点将在下面的描述中部分给出,这些将从下面的描述中变得明显,或通过本技术的实践了解到。

- 还没有人留言评论。精彩留言会获得点赞!