存储器阵列及存内计算电路

本发明涉及存储器,更为具体地,涉及一种存储器阵列及存内计算电路。

背景技术:

1、近年来,人工智能市场取得了显著增长,特别是在语音识别和机器视觉等领域。同时随着智能终端如智能手机、手表和手环等的不断普及,市场对于高能效硬件的需求也在不断增加。然而,传统的计算架构依赖冯·诺依曼体系结构,该体系将处理器和存储器分开,通过处理器从存储器中检索数据进行处理,然后将数据存回存储器。这个过程需要在处理器和存储器之间进行大量的数据传输,导致能耗和时间延迟显著增加。

2、目前,为缓解上述问题,常规方案是采用阻变存储器、相变存储器、磁性存储器和铁电存储器等新型器件实现数据存内计算。这些新型阻性存储器件利用器件的电阻值来存储数据,允许在单个单元中存储多个位。在阵列中,新型阻性存储器可以使用欧姆定律和基尔霍夫定律在模拟域内执行乘积累加操作,从而加速人工智能计算。因此,基于新型阻性存储器的存内计算芯片近年来受到了广泛研究。

3、其中,新型阻性存储器执行乘积累加的关键之一是权重映射方案,该方案将算法参数(例如神经网络中的权重)映射为电阻值并存储在阻变存储器阵列中,但是由于传统阻性存储器阵列中晶体管和存储的电学连接关系不对称,读取在存内计算应用中存在非对称权重读取问题,非对称权重读取读取问题使得存储权重正数和负数部分的1t1r结构上晶体管的栅压不稳定,使得对使栅宽/栅长(w/l)比较小的晶体管的存内计算阵列的识别精度退化。

4、可知,在传统阵列结构中,以及基本存储单元由串联集成的晶体管和电阻性器件组成,例如阻变存储器、相变存储器、磁性存储器和铁电存储器的存内计算系统都会面临不对称权重读取问题,导致准确性降低,而放大晶体管尺寸或过度驱动晶体管,均无法完全挽救准确性的损失,还可能会导致功耗更高,以及可靠性降低等问题。

技术实现思路

1、鉴于上述问题,本发明提供一种存储器阵列及存内计算电路,以解决现有存储器件所存在的存在不对称权重读取,导致准确性降低,无法满足栅宽/栅长比较小的晶体管的存内计算阵列的识别精度等问题。

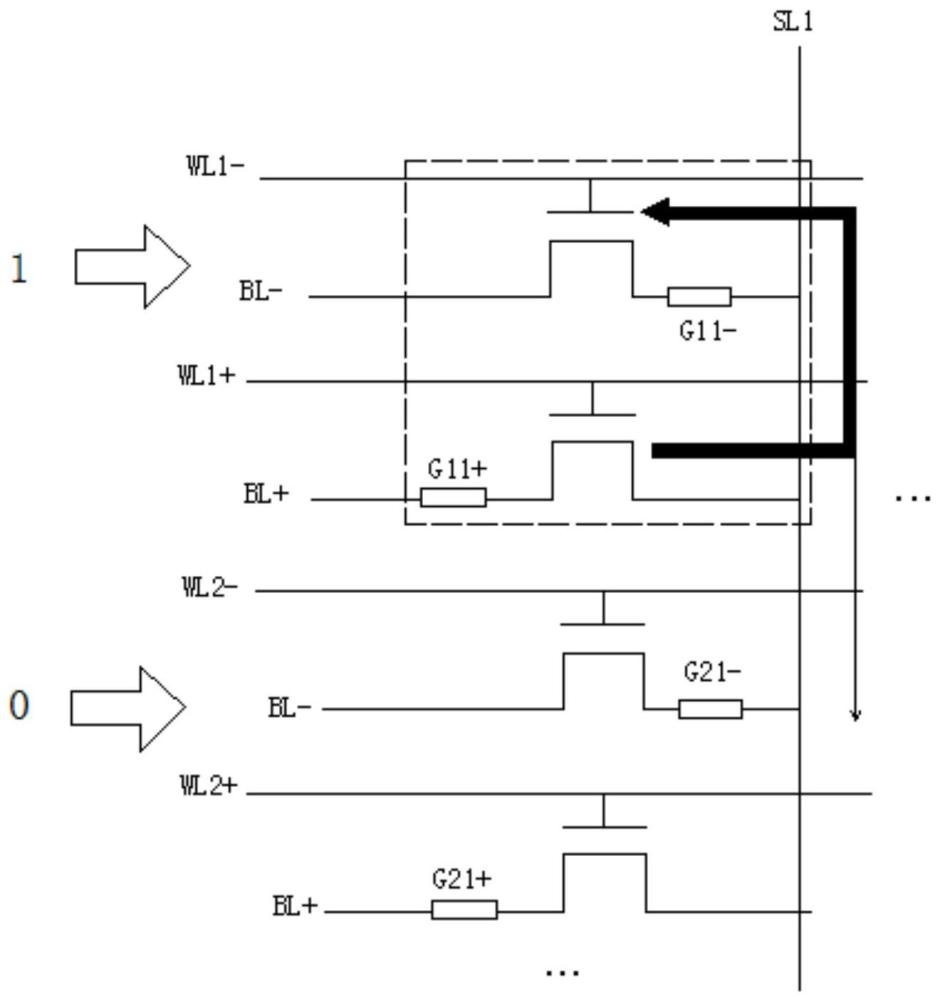

2、本发明提供的存储器阵列,包括呈阵列分布的存储单元,存储单元包括互补的第一存储结构和第二存储结构;其中,第一存储结构包括第一晶体管以及连接在第一晶体管的漏极上的第一存储器;第二存储结构包括第二晶体管以及连接在第二晶体管的漏极上的第二存储器;第一存储结构和第二存储结构之间相互隔离,且第一存储结构和第二存储结构呈中心对称。

3、此外,可选的技术方案是,设定电流方向由第二存储结构流至第一存储结构,其中,第一晶体管的栅极与字线wl-连接,第一晶体管的源极与位线bl-连接,第一存储器与源线sl连接;第二晶体管的栅极与字线wl+连接,第二晶体管的源极与源线sl连接,第二存储器与位线bl+连接。

4、此外,可选的技术方案是,当外部输入信号施加在字线wl-和字线wl+上时,若输入信号为“1”,第二存储结构的栅极上施加的电压为:vref+vg,第一存储结构的栅极上施加的电压为:vref+vg-vread;若输入信号为“0”,第二存储结构的栅极上施加的电压为:vref,第一存储结构的栅极上施加的电压为:vref-vread;其中,vread表示读取电压,vref表示参考电压,vg表示设计栅电压;vref和vg为固定值。

5、此外,可选的技术方案是,读取电压施加在位线bl-和位线bl+上,位线bl-上的电压为:vbl-=vref-vread,位线bl+上的电压为:vbl+=vref+vread;其中,vread表示读取电压,vref表示参考电压。

6、此外,可选的技术方案是,当外部输入信号施加在位线bl-和位线bl+上时,第二存储结构的栅极上施加的电压为:vref+vg,第一存储结构的栅极上施加的电压为:vref+vg-vread;其中,vread表示读取电压,vref表示参考电压,vg表示设计栅电压;vref和vg为固定值。

7、此外,可选的技术方案是,若输入信号为“0”,位线bl-和位线bl+上的电压为:vbl+=vbl-=vref;若输入信号为x,位线bl+上的电压为:vbl+=vref+vin,位线bl-上的电压为:vbl-=vref-vin;其中,vin=x·vread。

8、此外,可选的技术方案是,第一晶体管和第二晶体管为金属氧化物半导体场效应晶体管;第一存储器和第二存储器包括阻变存储器、相变存储器、铁电存储器和磁存储器。

9、此外,可选的技术方案是,第一晶体管和第二晶体管的沟道类型相同。

10、另一方面,本发明还提供一种存内计算电路,包括上述存储器阵列。

11、利用上述存储器阵列及存内计算电路,设置互补的第一存储结构和第二存储结构,并对第一存储结构和第二存储结构进行隔离设置,使其具备电学对称性质,在存储器阵列进行累积计算时,能够消除不对称权重读取问题,同时,还能够提高运算的准确度,并保持较小的晶体管栅宽/栅长,从而提高阵列的集成密度以及存储器的整体性能。

12、为了实现上述以及相关目的,本发明的一个或多个方面包括后面将详细说明的特征。下面的说明以及附图详细说明了本发明的某些示例性方面。然而,这些方面指示的仅仅是可使用本发明的原理的各种方式中的一些方式。此外,本发明旨在包括所有这些方面以及它们的等同物。

技术特征:

1.一种存储器阵列,其特征在于,包括呈阵列分布的存储单元,所述存储单元包括互补的第一存储结构和第二存储结构;其中,

2.根据权利要求1所述的存储器阵列,其特征在于,设定电流方向由所述第二存储结构流至所述第一存储结构,其中,

3.根据权利要求2所述的存储器阵列,其特征在于,当外部输入信号施加在所述字线wl-和所述字线wl+上时,

4.根据权利要求3所述的存储器阵列,其特征在于,

5.根据权利要求2所述的存储器阵列,其特征在于,当外部输入信号施加在所述位线bl-和所述位线bl+上时,

6.根据权利要求5所述的存储器阵列,其特征在于,

7.根据权利要求1所述的存储器阵列,其特征在于,

8.根据权利要求1所述的存储器阵列,其特征在于,

9.一种存内计算电路,其特征在于,包括如权利要求1至8任一项所述的存储器阵列。

技术总结

本发明提供一种存储器阵列及存内计算电路,其中的存储器阵列包括呈阵列分布的存储单元,存储单元包括互补的第一存储结构和第二存储结构;其中,第一存储结构包括第一晶体管以及连接在第一晶体管的漏极上的第一存储器;第二存储结构包括第二晶体管以及连接在第二晶体管的漏极上的第二存储器;第一存储结构和第二存储结构之间相互隔离,且第一存储结构和第二存储结构呈中心对称。利用上述发明能够在晶体管栅宽/栅长(W/L)较小的情况下,消除存储器阵列非对称权重读取问题。

技术研发人员:王宗巍,王翠梅,蔡一茂,凌尧天

受保护的技术使用者:北京大学

技术研发日:

技术公布日:2024/4/7

- 还没有人留言评论。精彩留言会获得点赞!