一种DDR5内存条的SPD烧录装置的制作方法

本技术涉及内存条烧录,特别涉及一种ddr5内存条的spd烧录装置。

背景技术:

1、spd全称为serial presence detect(模组存在的串行检测),是通过iic串行接口的eeprom(电可擦写可编程只读存储器)对内存插槽中的模组存在的信息检查。相关行业规定ddr5内存条的spd文件为1024kbyte,spd文件包含了内存条芯片时序、容量、工作电压、频率、生产厂商和rcd时钟地址驱动强度等重要参数,ddr5内存条spd烧录装置可以把spd二进制文件烧录到ddr5内存模组的spd芯片,cpu开机的时候通过i2c总线去读取spd文件对内存初始化和配置,从而可以充分发挥内存条的性能。

2、相关技术中,已有内存编程器四代烧录器ddr4内存烧录器,该技术每次对ddr4内存条烧录spd文件时,都必须搭配pc端以及相应的操作软件使用,而且是脱网单机使用,无法与生产系统进行互动;还有一种技术是eureka2933ddr42933mhz memory tester(ddr4存储器测试器),该技术也是每次必须搭配pc端以及相应的操作软件使用,如果没有pc端,该设备无法实现spd烧录功能。上述两种技术都只能实现ddr4的spd文件烧录,无法实现ddr5spd文件烧录,未来的发展中,ddr5内存条有着巨大的市场规模与需求,开发ddr5 spd烧录器迫在眉睫。

技术实现思路

1、本实用新型的目的是提供一种ddr5内存条的spd烧录装置,旨在解决如何实现对ddr5内存条进行spd文件烧录的问题。

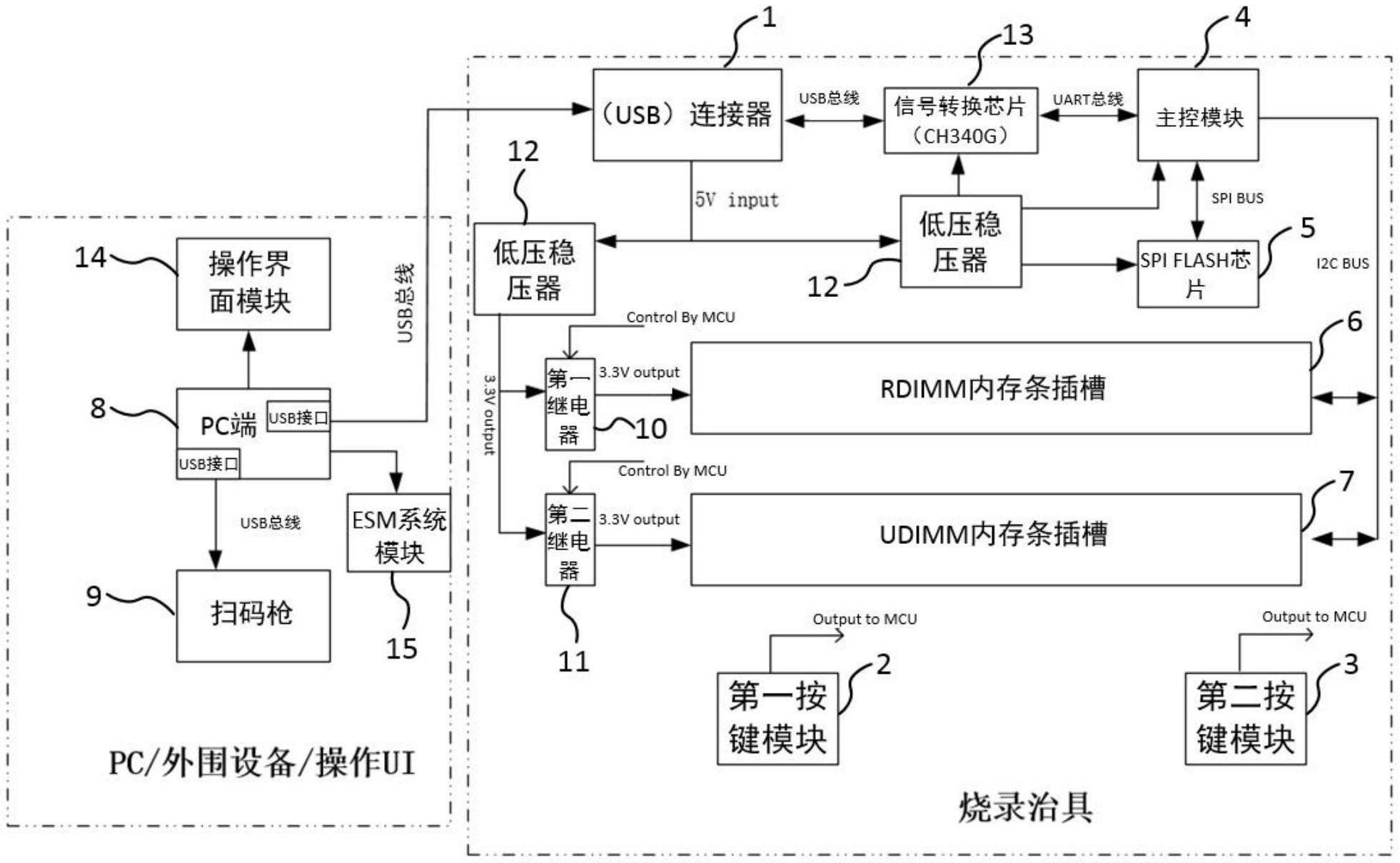

2、为解决上述技术问题,本实用新型的目的是通过以下技术方案实现的:提供一种ddr5内存条的spd烧录装置,包括:连接器、第一按键模块、第二按键模块、主控模块、spiflash芯片、rdimm内存条插槽和udimm内存条插槽;

3、所述连接器与主控模块连接,所述主控模块与spi flash芯片连接;

4、所述第一按键模块、主控模块和rdimm内存条插槽依次连接;

5、所述第二按键模块、主控模块和udimm内存条插槽依次连接。

6、进一步地,所述ddr5内存条的spd烧录装置,其特征在于,还包括pc端和扫码枪,所述扫码枪与所述pc端连接,所述扫码枪用于扫描待烧录内存卡条码。

7、进一步地,所述ddr5内存条的spd烧录装置,还包括第一继电器和第二继电器;所述主控模块分别与所述第一继电器和第二继电器连接,所述第一继电器和第二继电器分别与所述rdimm内存条插槽和udimm内存条插槽连接。

8、进一步地,所述ddr5内存条的spd烧录装置,还包括低压降稳压器,所述连接器通过所述低压降稳压器分别与所述主控模块、spi flash芯片、第一继电器和第二继电器连接。

9、进一步地,所述低压降稳压器的输出电压为3.3v。

10、进一步地,所述ddr5内存条的spd烧录装置,其特征在于,还包括信号转换芯片;所述pc端、连接器、信号转换芯片和主控模块依次连接。

11、进一步地,所述ddr5内存条的spd烧录装置,还包括uart总线,所述信号转换芯片和主控模块通过所述uart总线连接。

12、进一步地,所述ddr5内存条的spd烧录装置,还包括操作界面模块,所述操作界面模块与所述pc端连接。

13、进一步地,所述ddr5内存条的spd烧录装置,还包括mes系统模块,所述mes系统模块与所述pc端连接。

14、本实用新型实施例提供一种ddr5内存条的spd烧录装置,包括:连接器、第一按键模块、第二按键模块、主控模块、spi flash芯片、rdimm内存条插槽和udimm内存条插槽;所述连接器与主控模块连接,所述主控模块与spi flash芯片连接;所述第一按键模块、主控模块和rdimm内存条插槽依次连接;所述第二按键模块、主控模块和udimm内存条插槽依次连接。本实用新型实施例通过连接器作为通信接口将对应ddr5内存条的sdp文件预先存储至spi flash芯片中,再通过主控模块控制对应的sdp文件分别烧录至rdimm内存条插槽和udimm内存条插槽上的ddr5 rdimm内存条和ddr5urdimm内存条,可以单独或同时对两种ddr5内存条实现spd烧录功能。

技术特征:

1.一种ddr5内存条的spd烧录装置,其特征在于,包括:连接器、第一按键模块、第二按键模块、主控模块、spiflash芯片、rdimm内存条插槽和udimm内存条插槽;

2.根据权利要求1所述的ddr5内存条的spd烧录装置,其特征在于,还包括pc端和扫码枪,所述扫码枪与所述pc端连接,所述扫码枪用于扫描待烧录内存卡条码。

3.根据权利要求1所述的ddr5内存条的spd烧录装置,其特征在于,还包括第一继电器和第二继电器;所述主控模块分别与所述第一继电器和第二继电器连接,所述第一继电器和第二继电器分别与所述rdimm内存条插槽和udimm内存条插槽连接。

4.根据权利要求3所述的ddr5内存条的spd烧录装置,其特征在于,还包括低压降稳压器,所述连接器通过所述低压降稳压器分别与所述主控模块、spiflash芯片、第一继电器和第二继电器连接。

5.根据权利要求4所述的ddr5内存条的spd烧录装置,其特征在于:所述低压降稳压器的输出电压为3.3v。

6.根据权利要求2所述的ddr5内存条的spd烧录装置,其特征在于,还包括信号转换芯片;所述pc端、连接器、信号转换芯片和主控模块依次连接。

7.根据权利要求6所述的ddr5内存条的spd烧录装置,其特征在于,还包括usb总线,所述连接器和信号转换芯片通过所述usb总线连接。

8.根据权利要求7所述的ddr5内存条的spd烧录装置,其特征在于,还包括uart总线,所述信号转换芯片和主控模块通过所述uart总线连接。

9.根据权利要求2所述的ddr5内存条的spd烧录装置,其特征在于,还包括操作界面模块,所述操作界面模块与所述pc端连接。

10.根据权利要求2所述的ddr5内存条的spd烧录装置,其特征在于,还包括mes系统模块,所述mes系统模块与所述pc端连接。

技术总结

本技术公开了一种DDR5内存条的SPD烧录装置,包括:连接器、第一按键模块、第二按键模块、主控模块、SPIFLASH芯片、RDIMM内存条插槽和UDIMM内存条插槽;所述连接器与主控模块连接,所述主控模块与SPI FLASH芯片连接;所述第一按键模块、主控模块和RDIMM内存条插槽依次连接;所述第二按键模块、主控模块和UDIMM内存条插槽依次连接。本技术通过连接器作为通信接口将对应DDR5内存条的SDP文件预先存储至SPI FLASH芯片中,再通过主控模块控制对应的SDP文件分别烧录至RDIMM内存条插槽和UDIMM内存条插槽上的DDR5RDIMM内存条和DDR5URDIMM内存条,可以单独或同时对两种DDR5内存条实现SPD烧录功能。

技术研发人员:黄坚,黄秋容

受保护的技术使用者:南宁泰克半导体有限公司

技术研发日:20230109

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!