一种低功耗抗单粒子翻转SRAM存储单元

本发明属于集成电路设计,具体涉及一种抗单粒子翻转的sram存储单元。

背景技术:

1、从上个世纪70年代提出抗辐射加固电路设计以来,科学家陆续提出多种加固存储单元。1996年t.calin等人在“upset hardened memory design for submicron cmos”一文中提出典型的dice-12t存储单元。但随着工艺节点缩小,加固单元也面临的临界电荷不够,抗翻转能力下降的问题。因此,近些年来人们又提出多种4节点,6节点甚至更多节点的存储单元结构,例如2021年s.pal等人在“soft-error-aware read decoupled sram withmulti-node recovery for aerospace applications”一文中提出sarp-14t单元,m.p.kumar在“a 1.2v,radiation hardened 14t sram memory cell for aerospaceapplications”一文中提出rhs-14t单元。

2、然而现有的加固存储单元依然有以下问题,第一,由于节点之间的电荷共享问题,存储单元并不能从在大部分多节点翻转组合中恢复过来。第二,由于存储单元采用了冗余技术,增大的单元面积使得负载电容增大,且节点增多后,单元的漏电流也增大,最终导致加固单元的功耗增大。

技术实现思路

1、本发明目的在于提供一种静态功耗和访问功耗低的抗单粒子翻转的sram存储单元。

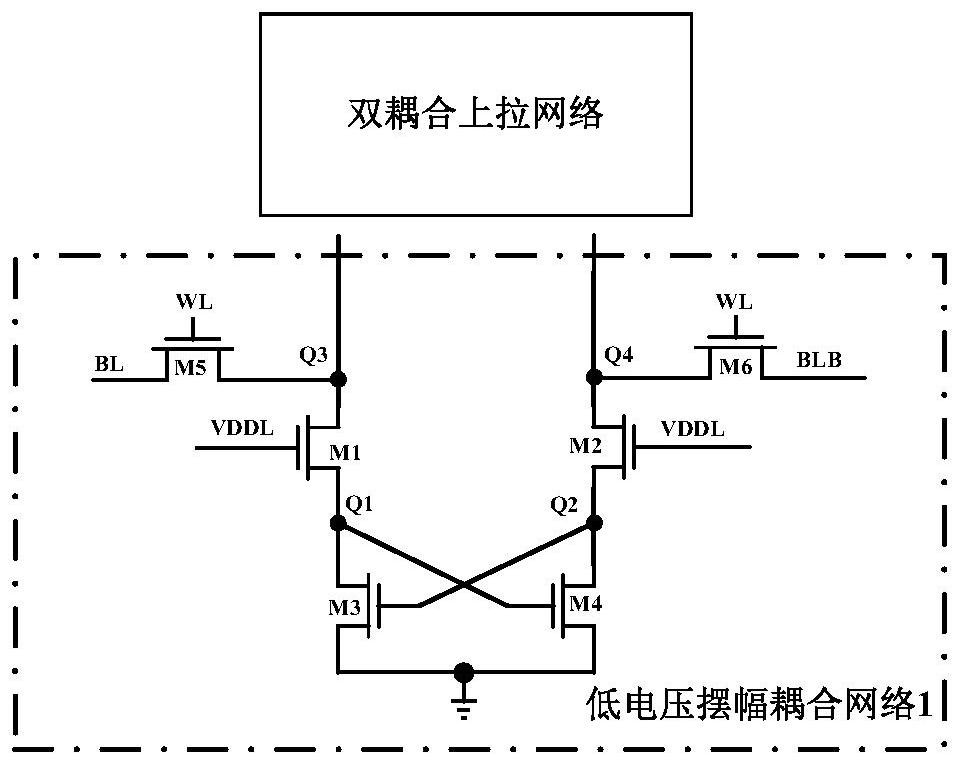

2、本发明提供的低功耗抗单粒子翻转的sram存储单元,其电路结构包含低电压摆幅的下拉网络、耦合上拉网络和半摆幅电压控制;sram存储单元具体分为双耦合存储单元和4耦合存储单元两种类型;其中:

3、所述低电压摆幅的下拉网络包含下堆叠管、上堆叠管、写选通管,下堆叠管交叉耦合,上堆叠管由写位线wbl和wblb控制;在双耦合存储单元中,上拉网络不做调整,下拉网络为一对交叉耦合的下拉堆叠结构,单元从强电位的逻辑节点读出;在4耦合存储单元中,增加写字线wwlb控制耦合存储单元的上拉网络电位,辅助写操作,单元从强电位逻辑节点读出,读电路为串联的n型晶体管。

4、低电压摆幅的下拉网络为主要写入结构;下拉网络主要组成部分为2对堆叠n型晶体管;在写入和保持过程中,上堆叠管的栅极由写字线控制;写字线的电压小于工作电压vdd,控制在50%-75%vdd以有效地提高稳定性,同时降低单元的漏电流和操作过程中的通路电流,从而降低功耗;写字线控制着堆叠网络上堆叠管,降低写字线的位线电压可以增强堆叠电路的分压能力,降低敏感节点产生的电压脉冲对堆叠管的中间节点的影响,从而提高单元抗翻转的能力。

5、本发明中,根据不同的存储单元的上拉网络,引入额外的读写控制信号选择不同的读写节点,通过写wl控制的选通管来增强单元的读写性能,使得单元可以在读写阶段共用一对位线。

6、本发明中,基于低电压摆幅的下拉网络,根据抗辐射能力需求增加冗余网络;存储单元为8t单元结构和16t单元结构两种类型。

7、本发明中,双耦合sram单元为8t结构,包含低电压摆幅的下拉网络和上拉网络;下拉网络包含下堆叠管、上堆叠管、写选通管;mos管m1,m2,m3和m4组成两组n-mos堆叠结构,mos管m1和m2为上堆叠管,其栅极由低电压信号vddl控制。

8、在操作过程中保持bl和blb的最大摆幅电压与保持电压vddl一致;vddl可以设置在50%-100%vdd之间。。

9、进一步地,对于双耦合8t结构的sram单元,通过降低vddl来降低流经节点q1和q2的漏电流,从而降低漏电流功耗,同时可以降低bl和blb的电压摆幅,从而降低单元的写入功耗;通过降低vddl可以增加串联晶体管分压的能力,降低敏感节点的电压脉冲对非敏感节点的电位的影响。

10、本发明中,对于4耦合存储单元,包括4个上拉网络,两个下拉网络,一个低电压摆幅耦合网络和一个读辅助电路;低电压摆幅下拉网络的写入节点略做调整,改变为中间节点q1和q2,且上拉堆叠管m1和m2分别由写入位线wbl和wblb控制;下拉网络和上拉网络通过耦合方式连接。

11、进一步地,对于4耦合存储单元,由6个n型晶体管m9-m14组成下拉低电压摆幅耦合网络;6个p型晶体管m1、m3、m2、m4、m7和m8为上拉管;其中,m1、m3与m2、m4的源极由wwlb控制;中间节点q3和q4分别交叉控制上拉网络晶体管m1、m8和m2、m7;中间节点q1和q2控制下拉网络和部分上拉网络晶体管,具体分别控制m3、m5、m12和m4、m6、m11;增加读旁路电路m15和m16,提高单元的读稳定性。

12、进一步地,对于4耦合存储单元,wwlb可以调节单元的上拉网络的电位,在写入过程中,wwlb使部分上拉网络电位降低至gnd,可以加快wbl和wblb对节点q1和q2的写入速度,降低通路电路,从而达到降低写入功耗。由于wbl和wblb控制堆叠管的上堆叠管,中间节点q1和q2的最高电位与wbl和wblb的最高一致,因而降低wbl和wblb的电位可以降低流经中间节点q1和q2的漏电流;控制wbl和wblb的电位高于n型管的阈值电压,可以实现单元的快速写入;通过降低wbl和wblb的最高保持电位,可以增强堆叠网络的分压能力,从而增强交叉耦合冗余网络抗p型势阱中多节点翻转的能力。

技术特征:

1.一种低功耗抗单粒子翻转的sram存储单元,其特征在于,电路结构包含低电压摆幅的下拉网络、耦合上拉网络和半摆幅电压控制;sram存储单元具体分为双耦合存储单元和4耦合存储单元两种类型;

2.根据权利要求1所述的低功耗抗单粒子翻转的sram存储单元,其特征在于,根据不同的存储单元的上拉网络,引入额外的读写控制信号选择不同的读写节点,通过写wl控制的选通管来增强单元的读写性能,使得单元可以在读写阶段共用一对位线。

3.根据权利要求1所述的低功耗抗单粒子翻转的sram存储单元,其特征在于,所述双耦合单元,包含低电压摆幅的下拉网络和上拉网络;下拉网络包含下堆叠管、上堆叠管、写选通管;其具体结构如下:n型mos管m3和m4为下堆叠管,漏极交叉控制对方栅极,源极接地;n型mos管m1和m2为上堆叠管,漏极分别与m3和m4的源极串联;m1与m3的中间串联节点为q1,m2与m4的中间串联节点为q2;m1和m2的栅极由电压信号vddl控制;m1和m2的漏极分别连接上拉管网络,连接点为q3和q4;n型mos管m5和m6为写选通管,其栅极由字线wl控制,写选通管m5和m6分别连接节点q3和q4与bl和blb。

4.根据权利要求1所述的低功耗抗单粒子翻转的sram存储单元,其特征在于,所述双耦合存储单元为8t结构,其中,n型mos管m3和m4为下堆叠管,漏极交叉控制对方栅极,源极接地;n型mos管m1和m2为上堆叠管,漏极分别与m3和m4的源极串联;m1与m3的中间串联节点为q1,m2与m4的中间串联节点为q2;m1和m2的栅极由电压信号vddl控制;m1和m2的漏极分别连接上拉管网络,连接点为q3和q4;n型mos管m5和m6为写选通管,其栅极由字线wl控制,写选通管m5和m6连接节点q3和q4与bl和blb;p型晶体管m7和m8的漏极交叉控制对方的栅极。

5.根据权利要求4所述的低功耗抗单粒子翻转的sram存储单元,其特征在于,在操作过程中降低bl和blb的最大摆幅电压与保持电压vddl保持一致;在保存阶段,所有选通管关闭,bl和blb的电压与vddl一致,vddl设置在50%-100%vdd之间;在写阶段,bl和blb接受数据信息,最大电压摆幅与保持电压一致,wl打开选通管,数据写入存储节点;读出阶段,bl/blb被预充到vddl,然后wl打开选通管,通过存储节点q3和q4读出数据,当bl和blb的电压差达到可分辨的阈值时,wl关闭选通管。

6.根据权利要求1所述的低功耗抗单粒子翻转的sram存储单元,其特征在于,所述4耦合单元,包括4个上拉网络,两个下拉网络,一个低电压摆幅耦合网络;两个上拉网络的源极由写控制信号wwlb控制,漏极与两个下拉网络的漏极串联;两个上拉网络的源极接电源,漏极与下拉网络的漏极串联;所有下拉网络的源极接地;上拉网络和下拉网络的串联结构之间通过串联结构内部的节点控制网络中的mos管栅极的方式交叉耦合连接;低电压摆幅耦合网络的结构为:n型mos管m3和m4为下堆叠管,漏极交叉控制对方栅极,源极接地;n型mos管m1和m2为上堆叠管,漏极分别与m3和m4的源极串联;m1与m3的中间串联节点为q1,m2与m4的中间串联节点为q2;m1和m2的栅极分别由wbl和wblb控制;m1和m2的漏极分别连接上拉管网络,连接点为q3和q4;n型mos管m5和m6为写选通管,其栅极由字线wwl控制,写选通管分别连接节点q1和q1与bl和blb。

7.根据权利要求1所述的低功耗抗单粒子翻转的sram存储单元,其特征在于,所述4耦合单元,为6t结构;由8个n型晶体管m5、m6、m9-m14组成下拉网络和写入结构;由6个p型晶体管m1、m3、m2、m4、m7和m8组成上拉网络;增加读旁路电路m15和m16;其中:m1漏极和m3源极串联,m1漏极和m3源极串联,m1和m2的源极接wwlb,m5和m6的源极接地;m3和m4的漏极分别与m5和m6的漏极串联,串联节点分别为q4和q3;m9的源极和m11的漏极串联,m10的源极和m12的漏极串联,串联节点分别为q1和q2;m9的漏极和m7的漏极串联,m0的漏极和m8的漏极串联,串联节点分别为s1和s2;m7和m8的源极接vdd,m11和m12的源极接地;选通管m13连接q1和wbl,选通管m14连接q2和wblb,m13和m14的栅极由写字线wwl控制;m9和m10的栅极分别由wbl和wblb控制;节点q1控制m3、m5和m12的栅极,节点q2控制m4、m6和m11的栅极;节点q4控制m7和m2的栅极,节点q3控制m1和m8的栅极;读旁路由n型晶体管m15源极和m16漏极串联而成,m16的栅极由节点q3控制,m15的栅极由读字线rwl控制;m15的漏极接读位线rbl,m16的源极接读字线rwl。

8.根据权利要求7所述的低功耗抗单粒子翻转的sram存储单元,其特征在于,操作阶段的控制信号的中位线的电压摆幅设置为50%vdd;在读阶段,disc将rbl下拉到gnd的控制信号,disc为“1”时,将rbl下拉至gnd,disc为“0”时,停止下拉;在写阶段,wwlb被拉低到gnd,同时wwl打开选通管,数据写入过程与双耦合单元类似,wbl和wblb接受数据信息,最大电压摆幅与保持电压一致;当内部节点q1-q4到达稳定状态,wwlb恢复到vdd,最终wwl关闭选通管完成写操作;在保持阶段,wwlb维持vdd,wbl和wblb都维持在写入状态的高电位。

技术总结

本发明属于集成电路设计技术领域,具体为低功耗抗单粒子翻转的SRAM存储单元。本发明SRAM存储单元电路结构包含低电压摆幅的下拉网络、耦合上拉网络和半摆幅电压控制;具体分为双耦合存储单元和4耦合存储单元两种类型;本发明以半VDD电压控制下拉堆叠网络,降低中间节点的保持电压,从而降低电路的漏电流功耗;字线电位半VDD摆幅的控制策略可以降低单元的写功耗,设计额外读电路,分离读写字线,提高电路的读稳定性。下拉堆叠网络的中间节点可以免疫特殊翻转,降低下拉网络的上堆叠管的栅电压可以使堆叠网络分压能力大幅抬高,从而提高敏感节点的临界电荷,使单元更加稳定。

技术研发人员:程旭,韩源源,韩军,曾晓洋

受保护的技术使用者:复旦大学

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!