基于SRAM接口带宽拓展的缓存方法、系统及装置与流程

本发明涉及isp图像信号处理缓存,尤其涉及一种基于sram接口带宽拓展的缓存方法、系统及装置。

背景技术:

1、随着coms技术的发展,图像分辨率越来越高、单个像素所占的比特数目也越来越多。如今的cmos图像分辨率涵盖了从百万像素到千万像素甚至上亿像素,单个像素所占的比特数从8比特到10比特甚到24比特,因此缓存多行图像数据需要使用到的sram容量也就越来越大,这对于芯片的面积、功耗和成本都是不利的。在对cmos图像一般都是采用isp处理,isp处理对一帧的图像通常是按行顺序传输的,前一行和后一行传输的间隔通常称为h_blank。一行图像缓存完成后进行读取,在h_blank比较小时会出现前一行还没有读完第二行数据又输入的情况。

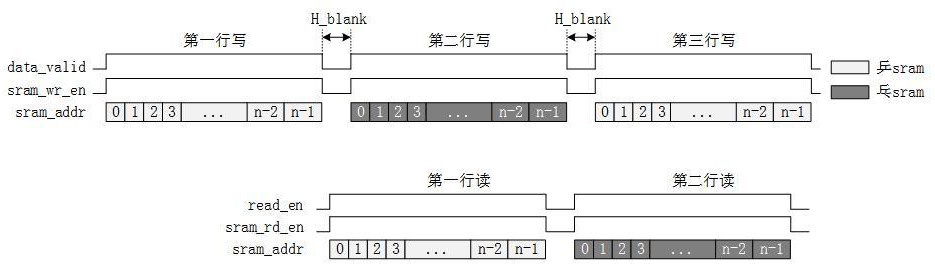

2、现有技术中,为了解决单口sram无法同时读写的问题,通常采用如图1所示的乒乓结构缓存图像数据,该结构使用乒和乓两个块sram构成,其通常让第一行数据完全写入乒sram后才开始读取乒sram,且第一行传输结束后等待间隔时间后第二行数据开始写入乓sram中,第二行写入完成后即开始读取乓sram。在一帧图像中包含多行时按照上述读写方式周期性的操作。另外,如果图像还需要进行水平镜像处理,此时的sram需要支持正序写入倒序读出的操作。如图2所示,输入数据还是按照地址0、1、2…、n-1的顺序写入sram,但读出时按照n-1、…、2、1、0的相反顺序进行读出。

3、另外,还存在有公布号为:cn103186474a、名称为:一种用于多流的数据缓存方法和装置的中国专利,其提出一种用于多流的数据缓存方法和装置。在该方法中,读操作和写操作共用同一个缓存,该方法包括 :对该缓存进行读操作以清空该缓存的部分地址的内容:将数据写入所述被清空的部分地址中。采用本发明的方案,只需要使用一个缓存,因而以相比乒乓缓存器节省 50%的存储器尺寸。

4、在上述专利中,其进行读和写操作虽然是共用一个缓存,但其进行数据缓存时需要连续的读或写操作,且只有读或写操作完成后,才能进行写或读操作,继而容易使得在进行缓存时发生操作冲突,影响缓存效率。

技术实现思路

1、本发明的目的是为了解决现有技术中在共用一个缓存时容易发生操作冲突影响缓存效率的缺点,而提出的一种基于sram接口带宽拓展的缓存方法、系统及装置。

2、为了实现上述目的,本发明采用了如下技术方案:

3、本发明第一方面提供了一种基于sram接口带宽拓展的缓存方法,包括:

4、根据数据操作需求,将目标接口的原有位宽拓宽,获得目标接口的拓宽位宽;

5、根据数据操作需求和目标接口的拓宽位宽,获得目标接口中的读操作周期和/或写操作周期;

6、a:根据读操作周期进行读操作,并获取读操作空隙期,在读操作空隙期在写操作;

7、或b:根据写操作周期进行写操作,并获取写操作空隙期,在写操作空隙期在读操作;

8、其中,所述读操作和写操作共用一个缓存。

9、在一种可行的实施例中,所述目标接口的拓宽位宽为目标接口的原有位宽的n倍,且n≥2,且n为整数。

10、在一种可行的实施例中,根据数据操作需求和目标接口的拓宽位宽,当进行数据水平操作时,奇数行顺序写入倒序读出和/或偶数行倒序写入顺序读出。

11、在一种可行的实施例中,所述缓存方法包括:

12、根据数据操作需求,确定数据输入行数和数据输入顺序;

13、根据目标接口的拓宽位宽和目标接口中的读操作周期和/或写操作周期,将数据输入行数按照数据输入顺序进行组合,获得输入组合行数,并将输入组合行数输入至目标接口的缓存地址中;

14、按照目标接口中的读操作周期和/或写操作周期,将目标接口的缓存地址进行读空,继续重复输入组合行数写入至目标接口的读空缓存地址中。

15、在一种可行的实施例中,所述并将输入组合行数输入至目标接口的缓存地址中前还包括:

16、需要进行读空一个目标接口的缓存地址。

17、在一种可行的实施例中,读空地址速度大于等于写入地址速度。

18、在一种可行的实施例中,所述获得目标接口中的读操作周期和/或写操作周期包括:

19、根据数据操作需求,获得读操作和/或写操作时序;

20、根据读操作和/或写操作时序,制定优先操作指令;

21、根据优先操作指令,优先进行读操作/写操作,并同时将写操作/读操作进行延时缓存;

22、在读操作/写操作完成后,立即进行写操作/读操作。

23、在一种可行的实施例中,所述缓存方法中还包括:

24、根据目标接口的拓宽位宽进行读取输入组合行数时,按照读取方式选择如下:

25、m:当读取位置处于奇数次时,直接读取输入组合行数,按照输入组合行数中单个数据输入行数的数据输入顺序,进行读取处于优先数据输入顺序的单个数据输入行数,并将输入组合行数中其他数据输入行数进行返回至目标接口的缓存地址中;

26、n:当读取位置处于偶数次时,将读取位置处于奇数次时返回目标接口缓存地址中的数据输入行数按照数据输入顺序进行排序读取。

27、本发明第二方面提供了一种基于sram接口带宽拓展的缓存系统,采用了如第一方面中任一项所述一种基于sram接口带宽拓展的缓存方法,所述缓存系统还包括:

28、数据拼接模块,所述数据拼接模块用于根据读操作周期和/或写操作周期,对数据输入行数进行拼接;

29、sram模块,所述sram模块用于进行读写缓存;

30、优先仲裁模块,所述优先仲裁模块用于制定写操作/读操作周期;

31、寄存模块,所述寄存模块用于配合优先仲裁模块进行制定写操作/读操作周期;

32、后级读取模块,所述后级读取模块用于将sram模块进行读出恢复。

33、本发明第三方面提供了一种基于sram接口带宽拓展的缓存装置,采用了如第一方面中任一项所述一种基于sram接口带宽拓展的缓存方法或如第二方面中所述一种基于sram接口带宽拓展的缓存系统。

34、在一种可行的实施例中,包括:

35、读装置,用于根据数据操作需求进行读操作,以选择性读空目标接口的缓存地址;

36、写装置,用于根据数据操作需求进行写操作,以写入已读空目标接口的缓存地址中。

37、在一种可行的实施例中,还包括:

38、数据拼接装置,所述数据拼接装置用于执行根据目标接口的拓宽位宽和目标接口中的读操作周期和/或写操作周期,将数据输入行数按照数据输入顺序进行组合,获得输入组合行数。

39、在一种可行的实施例中,还包括:

40、仲裁执行装置,所述仲裁执行装置用于对读操作/写操作时序进行优先操作指令附加,根据优先操作指令优先进行读操作/写操作,并同时将写操作/读操作进行延时缓存。

41、在一种可行的实施例中,还包括:

42、后级读取装置,所述后级读取装置用于根据读取所处位置,选择性对目标接口缓存地址中的输入组合行数进行读取。

43、在一种可行的实施例中,所述后级读取装置选择性对目标接口缓存地址中的输入组合行数进行读取的操作包括:

44、m:当读取位置处于奇数次时,直接读取输入组合行数,按照输入组合行数中单个数据输入行数的数据输入顺序,进行读取处于优先数据输入顺序的单个数据输入行数,并将输入组合行数中其他数据输入行数进行返回至目标接口的缓存地址中;

45、n:当读取位置处于偶数次时,将读取位置处于奇数次时返回目标接口缓存地址中的数据输入行数按照数据输入顺序进行排序读取。

46、本发明的有益效果为:

47、本发明通过提高单块sram接口位宽的方式让原有的连续读或连续写操作变为间断的读或写操作,从而能够在读操作或写操作间隔进行写操作或读操作,同时,在需要图像数据进行水平镜像时根据奇偶行周期性地调换读写顺序,进而能够充分利用已经被读空的地址缓存新的数据,从而避免了乒乓结构占用过多资源的情况。

- 还没有人留言评论。精彩留言会获得点赞!