忆阻器阵列列电流读出电路及装置

本发明属于微纳电子,具体涉及一种忆阻器阵列列电流读出电路及装置。

背景技术:

1、忆阻器阵列又称rram(resistive random access memory)阵列,是一种利用非易失的忆阻器和开关器件组成的交叉阵列,可以同时进行存储和计算,有望打破“存储墙”瓶颈。最常用的rram阵列为1t1r结构,1t1r称为rram单元。t(transistor)为晶体管,作为开关控制器件,一般选用nmos作为选通晶体管。r(memristor)为忆阻器件,阻值高低表示存储的信息,高阻态(hrs,high resistance state)和低阻态(lrs,low resistance state)分别代表0和1。

2、由于rram阵列非易失、面积小并与cmos工艺兼容等优势,可高速低功耗地实现乘累加操作,因此被广泛用于神经网络推理计算的加速应用。由于rram阵列的乘累加计算结果为模拟形式的列电流,因此需要使用读出电路将列电流量化为数字量以进行后续处理。传统高精度的模数转换器(adc,analog to digital converter)读出电路功耗高、面积大与能效低的劣势会抵消来自忆阻器阵列的高能效计算优势,因此设计合适精度的高速低功耗面积小的读电路成为急需解决的问题。

技术实现思路

1、基于此,有必要针对上述技术问题,提供一种忆阻器阵列列电流读出电路以及一种计算存储装置。

2、为了实现上述目的,本发明实施例采用以下技术方案:

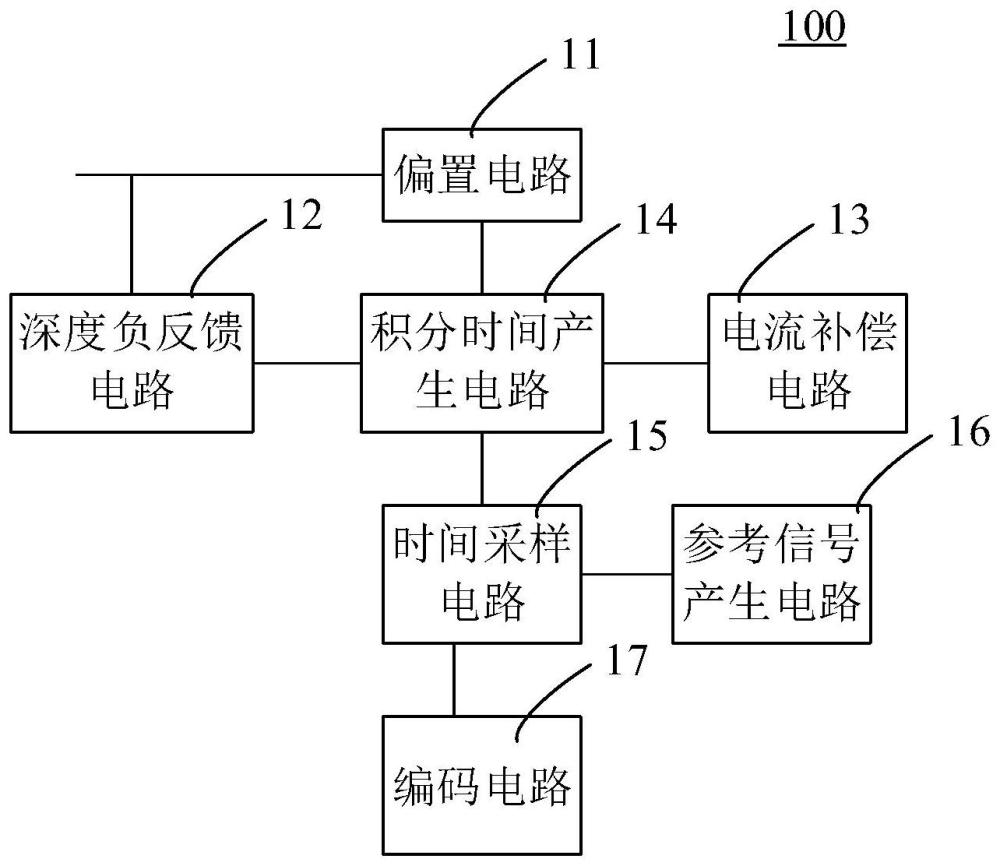

3、一方面,提供一种忆阻器阵列列电流读出电路,包括偏置电路、深度负反馈电路、电流补偿电路、积分时间产生电路、时间采样电路、参考信号产生电路和编码电路;

4、偏置电路分别连接深度负反馈电路和积分时间产生电路,偏置电路和深度负反馈电路均用于连接忆阻器阵列的列线输出端,积分时间产生电路分别连接深度负反馈电路、电流补偿电路和时间采样电路,时间采样电路分别连接参考信号产生电路和编码电路,编码电路的输出端用于输出忆阻器阵列的列线电流的数字量;

5、偏置电路用于为深度负反馈电路提供偏置电压,深度负反馈电路用于稳定列线端口的电压,电流补偿电路用于对列电流中由高阻态忆阻器产生的电流进行补偿,积分时间产生电路用于将经过稳定与补偿后的输入电流转换为时间跳变信号,时间采样电路用于对时间跳变信号的跳变点进行采样,参考信号产生电路用于提供时间采样电路所需的参考时间信号,编码电路用于将时间采样电路产生的多个采样结果信号编码为读出结果。

6、另一方面,还提供一种计算存储装置,包括忆阻器阵列和上述的忆阻器阵列列电流读出电路。

7、上述技术方案中的一个技术方案具有如下优点和有益效果:

8、上述忆阻器阵列列电流读出电路及装置,通过偏置电路为深度负反馈电路提供偏置电压,深度负反馈电路稳定列线端口的电压,电流补偿电路对列电流中由高阻态忆阻器产生的电流进行补偿,积分时间产生电路将经过稳定与补偿后的输入电流转换为时间跳变信号,时间采样电路对时间跳变信号的跳变点进行采样,参考信号产生电路提供时间采样电路所需的参考时间信号,编码电路将时间采样电路产生的多个采样结果信号编码为读出结果,实现支持高精确度读出的效果,尤其支持在低开关比的rram阵列中的精确读出。

9、相比于传统技术,实现了高速低功耗设计:与积分点火脉冲计数的方案相比,无需对积分电容多次充放电产生的脉冲进行计数,而是直接对积分时间进行采样,电容充放电一次即可实现读出,从而降低了功耗,提高了读出速度。上述设计的读出方案中列电流与积分时间之间有直接的数学对应关系,无需校准表,设计时可预先根据数学关系得到电路的初步设计方案,随后再仿真细调即可,设计难度低,满足了合适精度的高速低功耗面积小的读电路需求。而基于放电速率的电流-时间转换方案在电容放电、耦合和充电的过程中,缺少明确的理论指导以及信号之间的直接关系,需要在具体的电路仿真时逐个调整晶体管尺寸,设计复杂度高。

技术特征:

1.一种忆阻器阵列列电流读出电路,其特征在于,包括偏置电路、深度负反馈电路、电流补偿电路、积分时间产生电路、时间采样电路、参考信号产生电路和编码电路;

2.根据权利要求1所述的忆阻器阵列列电流读出电路,其特征在于,所述偏置电路包括mos管pm1、mos管pm2、mos管pm3、开关s01和偏置电流源ibias;

3.根据权利要求1或2所述的忆阻器阵列列电流读出电路,其特征在于,所述深度负反馈电路包括运算放大器ap和mos管nm8,所述运算放大器ap的正相输入端用于连接忆阻器阵列的列线输出端,所述运算放大器ap的反相输入端用于接入外接电压,所述运算放大器ap的输出端分别连接所述mos管nm8的栅极和所述积分时间产生电路的输入端,所述mos管nm8的漏极连接所述运算放大器ap的正相输入端,所述mos管nm8的源极连接所述积分时间产生电路的输入端。

4.根据权利要求3所述的忆阻器阵列列电流读出电路,其特征在于,所述电流补偿电路包括mos管pm0、mos管pm4、开关s1和补偿电流单元;所述补偿电流单元为忆阻器均为高阻态忆阻器的一列忆阻器阵列;

5.根据权利要求4所述的忆阻器阵列列电流读出电路,其特征在于,所述积分时间产生电路包括mos管pm5、mos管pm6、mos管nm7、mos管nm9、mos管nm10、mos管nm11、开关s2、积分电容cint和比较器cp;

6.根据权利要求1所述的忆阻器阵列列电流读出电路,其特征在于,所述时间采样电路包括n个相同的时间采样单元,其中,n=2r-1,r为量化输出的数字量bit位数;

7.根据权利要求6所述的忆阻器阵列列电流读出电路,其特征在于,所述参考信号产生电路包括多个依次级联且不同宽长比的反相器inv和参考电流单元,所述参考电流单元为忆阻器均为低阻态忆阻器的一列忆阻器阵列;首个反相器inv的输入端用于接入采样参考信号,各排在偶数位置处的反相器inv的输出端均用于输出一路参考时间信号到所述时间采样单元,所述参考电流单元用于产生采样参考信号outref。

8.根据权利要求7所述的忆阻器阵列列电流读出电路,其特征在于,所述时间采样单元包括7个,所述反相器inv包括14个。

9.一种计算存储装置,其特征在于,包括忆阻器阵列和权利要求1至8任一项所述的忆阻器阵列列电流读出电路。

技术总结

本申请涉及忆阻器阵列列电流读出电路及装置,提出了一种新颖的基于电流补偿和积分时间采样的列电流读出电路来量化RRAM阵列中的乘累加列电流。其核心构思是将列电流进行稳定、补偿和镜像后对一个小的积分电容充电,随后利用多个彼此之间的延时被精确设计过的时钟信号对积分跳变信号进行采样,最后将采样结果直接编码为数字量实现读出。并且,此电路采用了一个电流补偿机制来消除高阻值的RRAM单元对电流读出精度的影响,从而实现在低阻值开关比的RRAM阵列中的精确读出,满足了合适精度的高速低功耗面积小的读电路需求。

技术研发人员:陈长林,李清江,王义楠,杨为平,徐晖,刘森,刘海军,于红旗,王伟,李智炜,宋兵,步凯,王琴,曹荣荣,王玺,李楠,刁节涛

受保护的技术使用者:中国人民解放军国防科技大学

技术研发日:

技术公布日:2024/5/12

- 还没有人留言评论。精彩留言会获得点赞!