微装置匣体结构的制作方法

微装置匣体结构

1.相关申请案的交叉参考

2.本申请案主张以下美国临时专利申请案的优先权:在2019年11月12日申请的序列号为62/934,286的美国临时专利申请案、在2019年10月28日申请的序列号为62/926,980的美国临时专利申请案、及在2018年11月16日申请的序列号为62/768,812号美国临时专利申请案,所述美国专利申请案中的每一者特此以其全文引用方式并入本文中。

技术领域

3.本公开涉及将微装置集成到系统衬底中。此外,本公开还涉及用于增强微装置到衬底中的接合工艺的方法及结构。更具体来说,本公开涉及扩展微装置的面积或微装置的接合面积。

背景技术:

4.微装置的产生由几个主要步骤组成,例如多个层的外延生长、层的图案化及钝化、及剥离工艺。这些步骤可为昂贵的并因此迫切需要减小微装置的尺寸以在一个晶片衬底中生产更多微装置。如此,可降低每个微装置的成本。

5.然而,此装置的处理及接合可为具有挑战性的。例如,对于低于10微米装置,所述垫可小到几微米。将此类小垫接合到衬底需要显著对准,因为接合的质量将会受到重叠显著影响。此外,由于接合垫表面积小,此接合的特性可能受损。仍需要扩展微装置的装置面积或接合面积。

技术实现要素:

6.根据一个实施例,可提供一种将微装置集成在背板上的方法,所述方法包括:提供包括一或多个微装置的微装置衬底;通过连接一组选择性微装置上的垫及所述背板上的对应垫将所述一组选择性微装置从所述衬底接合到所述背板,通过分离所述微装置衬底让接合的所述一组选择性微装置留在所述背板上。

7.根据另一个实施例,倒装芯片装置上的垫经形成于或转移于装置的可接合到背板的适当侧上。

8.根据本公开的一个实施例,可提供一种光电子装置。所述光电子装置可包括:安置在衬底上从而形成顶表面及底表面的多个半导体层,其中所述多个半导体层具有形成至少一个侧表面的隔离区域;在顶表面或底表面中的至少一者上耦合到光电子装置的至少一个导电垫;及在所述至少一个侧表面围绕所述光电子装置形成的一或多个延伸层,其中所述至少一个导电垫延伸到所述一或多个延伸层。

附图说明

9.鉴于参考附图进行的对各种实施例及/或方面的详细描述,所属领域的一般技术人员将明白本公开的前述及其它优点,下面提供对附图的简要描述。

10.图1a展示具有到通孔的通路以将顶部连接传递到另一侧的微装置台面的截面图视图。

11.图1b展示具有通过通孔的通路的装置的俯视图。

12.图1c展示覆盖有牺牲层的微装置的横截面视图。

13.图1d展示根据本发明的一个实施例的接合到中间衬底的微装置的横截面视图。

14.图1e展示与第一衬底分离的微装置的横截面视图。

15.图1f展示至少一个垫形成于通过通孔的顶部上的微装置的横截面视图。

16.图2a展示在顶部具有保护层的微装置台面的横截面视图。

17.图2b展示具有保护层的装置的俯视图。

18.图2c展示覆盖有牺牲层的微装置的横截面视图。

19.图2d展示根据本发明的一个实施例的接合到中间衬底的微装置的横截面视图。

20.图2e展示与第一衬底分离的微装置的横截面视图。

21.图3a展示在顶侧上具有垫的倒装芯片微装置台面的横截面视图。

22.图3b展示在顶侧上具有垫的装置的俯视图。

23.图3c展示覆盖有牺牲层的微装置的横截面视图。

24.图3d展示根据本发明的一个实施例的接合到中间衬底的微装置的横截面视图。

25.图3e展示与第一衬底分离的微装置的横截面视图。

26.图3f展示接合到第三衬底的微装置的横截面视图。

27.图3g展示与第二衬底分离的微装置的横截面视图。

28.图4a展示具有覆盖微装置的顶部的电介质的微装置的横截面。

29.图4b展示具有凸块的微装置的顶部。

30.图4c展示具有覆盖具有牺牲层的微装置的顶部的电介质的微装置的横截面。

31.图4d展示在微装置衬底上具有平坦化层的微装置的横截面。

32.图4e展示与第一衬底分离的微装置的横截面视图。

33.图4f展示将导电层连接到底表面的另一层。

34.图5说明根据一个实施例的在其上沉积有层的堆叠的装置衬底的横截面视图。

35.图6a展示根据一个实施例的其中添加延伸层到装置110的结构。

36.图6b展示图2a中的结构的装置的示范性俯视图。

37.图7a展示根据一个实施例的其中延伸层用作平坦化层的装置。

38.图7b展示图3a中的结构的示范性俯视图。

39.图8a展示根据一个实施例的其中延伸层也用作平坦化层的另一装置实施例。

40.图8b展示图4a中的结构的示范性俯视图。

41.图9a展示根据一个实施例的其中顶部接触件延伸到微装置的底侧的实施例。

42.图9b展示根据一个实施例的其中垫延伸到延伸层的实施例。

43.图10展示根据一个实施例的装置衬底的横截面视图。

44.尽管本公开易于进行各种修改及替代形式,但特定实施例或实施方案已通过实例方式在附图中展示并将在本文中详细描述。然而,应理解,本公开不希望受限于所揭示的特定形式。而是,本揭示内容希望涵盖落在如由所附权利要求书所限定的本发明精神及范围内的所有修改、等效物及替代物。

具体实施方式

45.在本描述中,术语“装置”、“光电子装置”及“微装置”可互换使用。然而,所属领域的一般技术人员清楚,本文所述的实施例与装置尺寸无关。如本说明书及权利要求书中所使用,除非上下文清楚地另作指明,否则单数形式“一(a/an)”、及“所述”包括多个参考物。以下详细描述根据所提供的本发明结构及工艺的各种实施例。

46.本描述的一些实施例涉及将微装置集成到接纳衬底中。系统衬底可包括微型发光二极管(led)、有机led、传感器、固态装置、集成电路、(微机电系统)mems及/或其它电子组件。

47.此外,一些实施例涉及用于增强微装置到衬底(例如系统衬底)中的接合工艺的方法及结构。更具体来说,本公开涉及扩展微装置的装置面积或接合面积。本文描述一种光电子装置,其包括围绕光电子装置形成的一或多个延伸层及延伸到延伸层的至少一个接触层。

48.接纳衬底可为(但不限于)印刷电路板(pcb)、薄膜晶体管背板、集成电路衬底、或在光学微装置(例如led)的一种情况下,显示器的组件,例如驱动电路系统背板。可将微装置供体衬底及接纳衬底的图案化与不同转移技术结合使用,包括(但不限于)利用不同机构(例如静电转移头、弹性体转移头)、或直接转移机构(例如双功能垫等)进行取放。

49.在一个实施例中,微装置结构包括顶部及底部掺杂层、位于顶层与底层之间的有源层或功能层、从顶部掺杂层到底部掺杂层的通孔,其中所述通孔用电介质钝化并由导电材料部分或完全填充且所述通孔通过所述通孔的顶部上的导电层的延伸耦合到顶部掺杂层。

50.在另一个实施例中,微装置结构包括顶部及底部掺杂层、位于顶层与底层之间的有源层或功能层、从顶部掺杂层到底部掺杂层的通孔,其中所述通孔用电介质钝化并由导电材料部分或完全填充,所述通孔通过电介质层与顶部掺杂层分离。

51.以下详细描述根据所提供的本发明结构及工艺的各种实施例。

52.参考图1a,提供微装置衬底102。可在微装置衬底102上产生微装置104的阵列。在一种情况下,微装置可为微型发光装置。在另一种情况下,微装置可为通常可以平面批次制造的任何微装置,包括(但不限于)led、oled、传感器、固态装置、集成电路、mems及/或其它电子组件。

53.在一种情况下,可在衬底102上形成一或多个平坦有源层。平坦有源层可包括第一底部导电层、功能层(例如,发光功能层)及第二顶部导电层。微装置可通过蚀刻平坦有源层来产生。在一种情况下,蚀刻可一直进行到微装置衬底。在另一种情况下,蚀刻可部分在平坦层上进行并在微装置衬底的表面上留下一些。其它层可在形成微装置之前或之后进行沉积及图案化。

54.在此实施例中,通孔108经形成以将顶部接触件传递到底侧。在此,沉积电介质110以覆盖侧壁。电介质110可覆盖通孔108的底部。电介质110可覆盖微装置的顶层或侧壁的部分。可用导电层112完全或部分填充通孔。导电层112至少部分地连接到微装置104的顶层。

55.参考图1b,导电层112在微装置104的顶部上在通孔108的外部延伸。导电层112的延伸区域的部分可连接到微装置104的顶层。

56.如图1c中展示,形成牺牲层114(或多个牺牲层)以至少覆盖微装置104表面的暴露

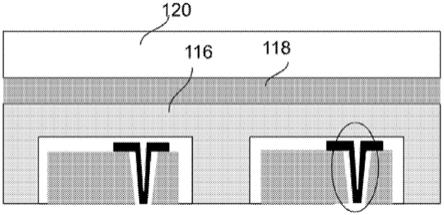

区域。牺牲层114可经图案化以具有通向装置104的开口以形成锚。在一种情况下,通孔108的顶部上的区域可在牺牲层114中具有开口。在图1d中,在微装置衬底102上形成平坦化层116以围绕微装置104。在牺牲层114中存在开口的情况下,所述开口将用平坦化层填充,从而形成锚。如图1d中展示,接合层118用于将新结构接合到第二衬底120中。在此,接合层118及平坦化层116可为相同的。在另一种情况下,平坦化层116在与接合层118接合之前产生并固化。

57.参考图1e,从微装置104分离第一衬底102。让所述结构接合到第二衬底。回蚀或移除额外层可暴露平坦化层116(或牺牲层114)的表面。此刻,可从底侧暴露导电层112,或可能需要进一步蚀刻来完成此。

58.如图1f中展示,凸块122、124(或垫)可形成在微装置上而通过通孔108及导电层112直接耦合到底表面及顶表面。底表面及顶表面可具有掺杂层或欧姆接触层。电介质层122

‑

2将凸块122与底表面分离。

59.参考图1a到1e,存在具有顶部及底部掺杂层的微装置。可存在部分或完全覆盖顶层或底层的欧姆层。在掺杂层之间是有源层或功能层,例如多量子阱、势垒、阻挡件、包层等。存在从顶部掺杂层一直到底部掺杂层的通孔108。其还可穿过顶部或底部上的欧姆层或其它导电层。通孔108用电介质110钝化并由导电112材料完全或部分覆盖。导电112材料部分或完全耦合到顶部欧姆或掺杂层。垫或凸块122经形成为与通孔108中的导电材料112耦合同时通过电介质122

‑

2与底部欧姆或掺杂层分离。形成另一凸块/垫124以与底部欧姆/掺杂层耦合。电介质层可为相同层。电介质可覆盖整个顶表面及底表面并具有开口以在需要时提供到顶层或底层的入口。

60.参考图2a,提供微装置衬底202。可在微装置衬底202上产生微装置204的阵列。在一种情况下,微装置可为微型发光装置。在另一种情况下,微装置204可为通常可以平面批次制造的任何微装置,包括(但不限于)led、oled、传感器、固态装置、集成电路、mems及/或其它电子组件。

61.在一种情况下,可在衬底202上形成一或多个平坦有源层。平坦有源层可包括第一底部导电层、掺杂层、功能层(例如,发光功能层)、另一顶部掺杂层及第二顶部导电层。微装置可通过蚀刻平坦有源层来产生。在一种情况下,蚀刻可一直进行到微装置衬底。在另一种情况下,蚀刻可部分在平坦层上进行并在微装置衬底的表面上留下一些。其它层可在形成微装置之前或之后进行沉积及图案化。

62.可在微装置204的顶部上形成保护层212。所述保护层可为导电的并耦合到顶部掺杂或欧姆层。保护层可为欧姆层的一部分。

63.参考图2b,导电层212是在微装置204的顶部上。导电层212的一部分可连接到微装置204的顶层。

64.如图2c中展示,形成牺牲层214(或多个牺牲层)以至少覆盖微装置204表面的暴露区域。牺牲层214可经图案化以具有通向装置204的开口以形成锚。在一种情况下,保护层212的顶部上的区域可在牺牲层214中具有开口。在图2d中,在微装置衬底202上形成平坦化层216以围绕微装置204。在牺牲层214中存在开口的情况下,所述开口将用平坦化层216填充,从而形成锚。如图2d中展示,接合层218用于将新结构接合到第二衬底220中。在此,接合层218及平坦化层216可为相同的。在另一种情况下,平坦化层216是在与接合层218接合之

前产生并固化。

65.参考图2e,从微装置204分离第一衬底202。让所述结构接合到第二衬底。回蚀或移除额外层可暴露平坦化层216(或牺牲层214)的表面。此刻,可从底侧暴露导电层212,或可能需要进一步蚀刻来完成此。

66.在此实施例中,通孔208经形成以将顶部接触件传递到底侧。在此,沉积电介质210以覆盖侧壁。通孔208从底部延伸到保护层(或到顶部导电层)并其可用导电层212完全或部分填充。可形成连接到导电层212的垫222。垫222以电介质222

‑

2与底层分离。电介质层222

‑

2可与210相同。形成连接到底层的另一垫224。这些垫222、224可用于将装置连接到背板。

67.参考图2a到2e,存在具有顶部及底部掺杂层的微装置204。可存在部分或完全覆盖顶层或底层的欧姆层。在掺杂层之间的是有源层或功能层,例如多量子阱、势垒、阻挡件、包层等。存在从顶部掺杂层一直到底部掺杂层的通孔208。其还可穿过顶部或底部上的欧姆层或其它导电层。通孔208用电介质210钝化。导电层212在通孔208的一端形成于微装置204的顶部上。导电212材料是部分或完全耦合到顶部欧姆或掺杂层。垫或凸块222经形成为与通孔208中的导电材料212耦合同时通过电介质222

‑

2与底部欧姆或掺杂层分离。形成另一凸块/垫224以与底部欧姆/掺杂层耦合。电介质层可为相同层。电介质可覆盖整个顶表面及底表面并具有开口以在需要时提供到顶层或底层的入口。

68.参考图3a,提供微装置衬底302。可在微装置衬底302上产生微装置304的阵列。在一种情况下,微装置可为微型发光装置。在另一种情况下,微装置304可为通常可以平面批次制造的任何微装置,包括(但不限于)led、oled、传感器、固态装置、集成电路、mems及/或其它电子组件。

69.在一种情况下,可在衬底302上形成一或多个平坦有源层。平坦有源层可包括第一底部导电层、掺杂层、功能层(例如,发光功能层)、另一顶部掺杂层及第二顶部导电层。微装置可通过蚀刻平坦有源层来产生。在一种情况下,蚀刻可一直进行到微装置衬底。在另一种情况下,蚀刻可部分在平坦层上进行并在微装置衬底的表面上留下一些。其它层可在形成微装置之前或之后进行沉积及图案化。

70.通孔308经形成以提供到底部掺杂或欧姆层的入口。通孔通过电介质层310钝化。通孔308是完全或部分地使用导电层312。凸块或垫322形成于耦合到导电层312的顶表面上而凸块322通过电介质320层与顶侧分离。形成另一凸块或垫324以连接到顶部欧姆或掺杂层。

71.参考图3b,凸块322、324是在微装置304的顶部上。导电层312的部分可连接到微装置304的顶层。

72.如图3c中展示,形成牺牲层314(或多个牺牲层)以至少覆盖微装置304表面的暴露区域。牺牲层314可经图案化以具有通向装置304的开口以形成锚。在一种情况下,保护层312的顶部上的区域可在牺牲层314中具有开口。在图3d中,在微装置衬底302上形成平坦化层316以围绕微装置304。在牺牲层314中存在开口的情况下,所述开口将用平坦化层填充,从而形成锚。如图3d中展示,接合层318用于将新结构接合到第二衬底320中。在此,接合层318及平坦化层316可为相同的。在另一种情况下,平坦化层316在与接合层318接合之前产生并固化。

73.参考图3e,从微装置304分离第一衬底302。让所述结构接合到第二衬底320。回蚀

或移除额外层可暴露平坦化层316(或牺牲层314)的表面。

74.如图3f中展示,在微装置304的底部上形成第二牺牲层326。在此,可通过由打开牺牲层326的一部分来形成锚。新接合或平坦化层328在表面上产生并接合到第三衬底330。如图3g中所展示,移除第二衬底320(释放层可位于第二衬底320与接合层318之间)。在此,牺牲层314的部分可经部分地移除以暴露垫322及324。新锚可经形成为具有将微装置304连接到平坦化316(外壳结构)的金属或电介质层。

75.参考图4a,提供微装置衬底402。可在微装置衬底402上产生微装置404的阵列。在一种情况下,微装置可为微型发光装置。在另一种情况下,微装置404可为通常可以平面批次制造的任何微装置,包括(但不限于)led、oled、传感器、固态装置、集成电路、mems及/或其它电子组件。

76.在一种情况下,可在衬底402上形成一或多个平坦有源层。平坦有源层可包括第一底部导电层、掺杂层、功能层(例如,发光功能层)、另一顶部掺杂层及第二顶部导电层。微装置可通过蚀刻平坦有源层来产生。在一种情况下,蚀刻可一直进行到微装置衬底。在另一种情况下,蚀刻可部分在平坦层上进行并在微装置衬底的表面上留下一些。其它层可在形成微装置之前或之后进行沉积及图案化。

77.通孔408是经形成以可提供到底部掺杂或欧姆层的入口。通孔408用电介质层410钝化。电介质可覆盖微装置的顶表面。通孔408使用导电层412完全或部分地填充。凸块或垫422形成于耦合到导电层412的顶表面上。如果电介质层(或钝化层)覆盖顶表面,那么电介质层(或钝化层)中可存在开口以提供到凸块422的顶表面的入口。凸块422通过电介质420层(其可与层410相同)与顶侧分离。形成另一凸块或垫424以连接到顶部欧姆或掺杂层。

78.参考图4b,凸块422及424是在微装置404的顶部上。导电层412的部分可连接到微装置404的顶层。

79.如图4c中展示,形成牺牲层414(或多个牺牲层)以至少覆盖微装置404表面的暴露区域。牺牲层414可经图案化以具有通向装置404的开口以形成锚。在一种情况下,保护层412的顶部上的区域可在牺牲层414中具有开口。在图4d中,在微装置衬底402上形成平坦化层416以围绕微装置404。在一种情况下,在牺牲层414中存在开口,所述开口将用平坦化层填充,从而形成锚。如图4d中展示,接合层418用于将新结构接合到第二衬底420中。在此,接合层418及平坦化层416可为相同的。在另一种情况下,平坦化层416在与接合层418接合之前产生并固化。

80.参考图4e,从微装置404分离第一衬底402。让所述结构接合到第二衬底420。回蚀或移除额外层可暴露平坦化层416(或牺牲层414)的表面。装置可回蚀到通孔408的敞开底部并提供到导电层412的入口。参考图4f,可在底表面上形成层460以将层412连接到底表面。

81.图5展示光电子装置衬底502,其中将不同导电层504及有源层506沉积于装置衬底502的顶部上,随后是其它导电层508。所述装置包括安置在装置衬底502上从而形成顶表面及底表面的多个半导体层,其中所述多个半导体层经隔离成形成至少一个侧表面的较小区域且至少一个导电垫经形成以在顶表面或底表面上中的任一表面上耦合到光电子装置。导电层504可包括缓冲层、p型掺杂层、n型掺杂层、电荷阻挡层及电极。有源层506可包括多量子阱(mqw)层及其它导电层508。mqw层可包括堆叠中的多个单量子层。导电层可为透明或不

透明的。透明导电层的实例为可形成于p掺杂半导体层(例如gan或gaas)上以实现更好的横向电流传导的薄ni/au或ito。导电层可具有不同层的堆叠。例如,接着在透明导电层上形成p型电极,例如pd/au、pt或ni/au。在此,欧姆接触件512由电介质层510围绕。垫514可沉积于欧姆接触件512上并可在电介质层上延伸。电介质层可避免装置与欧姆接触件之间的不想要的短路/耦合。

82.然而,对于具有多个垫的小装置或装置,所述区域可能不足以使所述垫变大。图6a展示形成于衬底502上的微装置506,其中多个延伸层610添加到装置506。听,所述一或多个延伸层在侧表面形成围绕所述光电子装置506且至少一个垫延伸到所述一或多个延伸层610。这些延伸层610中的一些可具有其它功能,例如反射、颜色转换等。电介质层510可在延伸层610上延伸。垫514还可在延伸层610上延伸。延伸层610还可通过使用不同反射指数进行优化以增强光提取。在一种情况下,延伸层610可形成于沉积在衬底502上的缓冲层上。

83.在一个实施例中,所述一或多个延伸层中的至少一者是聚合物且所述一或多个延伸层中的至少一者的宽度在100nm到几微米之间。

84.图6b展示如图6a中所展示的装置的示范性俯视图。在此,延伸层622覆盖微装置624的至少一个侧且连接到接触件/通孔512的垫620沿一个方向延伸到延伸层622的至少一部分。

85.图7a展示其中延伸层622也用作平坦化层的装置。在此,装置702具有多于一个接触件(706、704)且在延伸层622中存在开口以提供到所述接触件(706、704)中的至少一者的入口。延伸层622还可包括电介质层。垫(p、n)中的一者至少覆盖延伸层622的一部分。

86.图7b展示图7a中的结构的示范性俯视图。在此,延伸层622覆盖沟槽710的至少一个侧到低位接触件706。用于那个连接的垫712可延伸到延伸层622的至少一个区域。装置708的另一侧上的另一接触件308连接到另一垫714,所述另一垫可延伸到延伸层622的至少另一区域。

87.图8a展示其中延伸层622也用作平坦化层的另一装置实施例。在此,所述装置具有多于一个接触件(804、806)且在延伸层622中存在开口以提到到所述接触件(804、806)中的至少一者的入口。延伸层622还可包括电介质层。垫(p、n)中的一者至少覆盖延伸区域的部分。栅极接触件810还可提供到连接到栅极金属的延伸层622。

88.图8b展示图8a中的结构的示范性俯视图。在此,延伸层622覆盖沟槽810的至少一个侧到低位接触件808。用于那个连接的垫806延伸到延伸层622的至少一个区域。在此,其它接触件812、814通过其它接触垫820、840连接到装置308。装置708的另一侧上的另一接触件814连接到另一垫840,所述另一垫是延伸到延伸层622的至少另一区域。

89.图9a展示其中顶部接触件902延伸到装置624的底侧的实施例。迹线904由延伸层622覆盖。之后,穿过延伸层622或装置区域的一部分的通孔提供从装置的另一侧到所述装置的入口。顶部接触件902可通过通孔连接到迹线。

90.图9b展示其中顶部接触件916可通过迹线918延伸到微装置的另一侧的实施例。迹线918由延伸层622覆盖。延伸层622可为平坦化层。暂时性衬底920可经接合于微装置的顶表面上。延伸层622可形成于沉积在衬底920上的缓冲层922上。在一种情况下,可存在中间层906,其通过通孔930连接到垫914。在另一种情况下,其可直接连接到垫914。垫914可延伸到延伸层622。

91.图10展示根据本发明的一个实施例的具有连接到驱动器衬底的多个微装置的实施例。驱动器衬底可包括像素电路1018。通过接合垫1008或通过迹线1004耦合到像素电路的微装置1010经沉积以覆盖装置中的至少一个接触点及耦合到像素电路的驱动器衬底中的一个接触点。驱动器衬底可在不同于微装置1010所处侧的侧上具有接触垫1040。这些接触垫1040通过衬底中的通孔1020耦合到像素电路1018或耦合到微装置。可在微装置的一部分与驱动器衬底的一部分之间存在极化/电介质层1016。在将微装置1010集成于驱动器衬底中之后,可存在其它平坦化/封装层1012。接着,驱动器衬底通过驱动器衬底上的接合垫1040及系统衬底1000上的垫1002或通过经沉积以覆盖驱动器衬底中的至少一个接触点及系统衬底1000中的一个接触点的迹线1022耦合到系统衬底。系统衬底600可具有实现接近驱动器衬底的额外电路系统或接触层1042。接合剂1042提供机械可靠性并还可用作耦合剂。在一种情况下,接合剂1042可经图案化为仅在所选区域中。系统衬底1000与驱动器衬底之间可存在平坦化剂及接合剂640。在此,可提供多个微装置1010,例如红色、绿色及蓝色。可将多个微装置一起连接到驱动器衬底,从而形成电池。

92.根据一个实施例,提供一种光电子装置,多个半导体层安置在衬底上从而形成顶表面及底表面,其中所述多个半导体层具有形成至少一个侧表面的隔离区域、在顶表面或底表面中的至少一者上耦合到光电子装置的的至少一个导电垫;及在至少一个侧表面围绕光电子装置形成的一或多个延伸层,其中所述至少一个导电垫延伸到一或多个延伸层。

93.根据另一个实施例,一或多个延伸层覆盖光电子装置的至少一个侧及通过一或多个延伸层中的开口提供的至少一个接触件。

94.根据又一实施例,光电子装置进一步包括围绕至少一个接触件形成并在一或多个延伸层上延伸的电介质层。

95.根据一些实施例,至少一个垫沉积于至少一个接触层上并在电介质层上延伸。所述一或多个延伸层包括以下各者的至少一者:另一电介质层、反射层及颜色转换层。

96.根据另一个实施例,所述一或多个延伸层形成于缓冲层上。所述一或多个延伸层扩展光电子装置的面积。

97.根据另一个实施例,所述一或多个延伸层中的至少一者是聚合物且所述一或多个延伸层中的至少一者的宽度在100nm到几微米之间。

98.尽管已说明并描述本发明的特定实施例及应用,但应理解本发明并不受限于本文所揭示的精确构造及组成,且可从前述描述在不脱离如所附权利要求书中所限定的本发明精神及范围下明白各种修改、改变及变动。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1