芯片封装结构的制作方法

1.本发明有关于一种芯片封装结构,特别是有关于一种具有多芯片堆叠的芯片封装结构。

背景技术:

2.随着电子产品的微小化与多功能化,多芯片的封装结构在许多电子产品越来越常见,其系将两个或两个以上的芯片封装在单一封装结构中,以缩减整体体积。常见的多芯片封装结构系将两个以上的芯片彼此并排地设置于同一基板上,但并排设置芯片将使得封装结构的面积随着芯片数量的增加而加大。为解决此问题,目前发展出使用堆叠的方式来配置芯片。然而,堆叠芯片的方式仍存在缺点,例如垂直堆叠芯片会造成封装结构的厚度过高,以及堆叠在最上方的芯片电连接到电路板的电阻会变大,以致于增加功率消耗。

技术实现要素:

3.根据本发明的一实施例,提供一种芯片封装结构,其包括电路板、第一芯片、间隔件以及第二芯片。第一芯片设置于电路板上,间隔件设置于电路板上,其中间隔件包括间隔部以及至少一第一穿孔结构,且第一穿孔结构贯穿间隔部。第二芯片设置于第一芯片与间隔件上,且第二芯片通过间隔件电连接到电路板。

4.通过具有穿孔结构的间隔件,可有效地焊线的长度,以降低焊线的电阻值。藉此,可提升芯片封装结构的效能或降低芯片封装结构的功率消耗,还可降低芯片封装结构的整体宽度。

附图说明

5.图1绘示本发明第一实施例的芯片封装结构的俯视示意图。

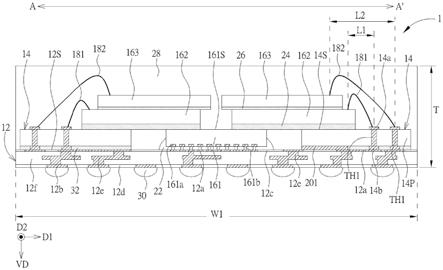

6.图2绘示沿着图1的剖线a-a’的剖视示意图。

7.图3绘示本发明第二实施例的芯片封装结构的剖视示意图。图4绘示本发明第三实施例的芯片封装结构的剖视示意图。图5绘示本发明第四实施例的芯片封装结构的剖视示意图。图6绘示本发明第五实施例的芯片封装结构的剖视示意图。图7绘示本发明第六实施例的芯片封装结构的剖视示意图。

8.附图标记:

9.1,2,3,4,5,6:芯片封装结构

10.12:电路板

11.12a,14a:上接垫

12.12b,14b:下接垫

13.12c:上保护层

14.12d:下保护层

15.12e:内连线

16.12f:绝缘层

17.12s,14s,161s,562s1,163s:上表面

18.14:间隔件

19.14p:间隔部

20.161:第一芯片

21.161a,162a,163a:输入/输出接垫

22.161b,50:导电凸块

23.162,462,562:第二芯片

24.163:第三芯片

25.181:第一焊线

26.182:第二焊线

27.183:第三焊线

28.201,202,542,642:连接件

29.22:底部填充胶

30.24,26,32:粘着层

31.28:封装胶体

32.30:导电球

33.34,36,44,46:介电层

34.38,48:导电层

35.562a:接垫

36.562d:元件

37.562m:芯片主体

38.562s2:下表面

39.d1,d2:方向

40.l1,l2:长度

41.t:厚度

42.th1:第一穿孔结构

43.th2:第二穿孔结构

44.vd:俯视方向

45.w1,w2,w3:宽度

具体实施方式

46.通过参考以下的详细描述并同时结合图式可以理解本发明,须注意的是,为了使读者能容易了解及图式的简洁,本发明的图式只绘出芯片封装结构的至少一部分,且图式中的特定元件并非依照实际比例绘图。此外,图式中各元件的数量及尺寸仅作为示意,并非用来限制本发明的范围。

47.本发明通篇说明书与所附的权利要求范围中会使用某些术语来指称特定元件。本领域技术人员应理解,电子设备制造商可能会以不同的名称来指称相同的元件。本文并不意在区分那些功能相同但名称不同的元件。在下文说明书与权利要求范围中,“含有”与“包

括”等词为开放式词语,因此其应被解释为“含有但不限定为

…”

之意。

48.应了解到,当元件或膜层被称为在另一个元件或膜层“上”或“连接到”另一个元件或膜层时,它可以直接在此另一元件或膜层上或直接连接到此另一元件或层,或者两者之间存在有插入的元件或膜层。相反地,当元件被称为“直接”在另一个元件或膜层“上”或“直接连接到”另一个元件或膜层时,两者之间不存在有插入的元件或膜层。

49.须知悉的是,以下所举实施例可以在不脱离本发明的精神下,将数个不同实施例中的技术特征进行替换、重组、混合以完成其他实施例。

50.图1绘示本发明第一实施例的芯片封装结构的俯视示意图,图2绘示沿着图1的剖线a-a’的剖视示意图。芯片封装结构1包括电路板12以及设置于电路板12上的至少一间隔件14与至少二芯片(例如第一芯片161与第二芯片162),其中一个芯片(例如第一芯片161)设置在间隔件14与另一个芯片(例如第二芯片162)上,且设置在间隔件14上的芯片可通过间隔件14电连接电路板12,藉此缩小水平方向上的芯片封装结构1的宽度w1及/或降低芯片封装结构1的厚度t。水平方向可例如为平行于电路板12上表面12s的方向d1、方向d2或平行于电路板12上表面12s且不同于方向d1与方向d2的方向。

51.电路板12可例如为印刷电路板(printed circuit board)或其他类型的电路板,但不限于此。在一些实施例中,电路板12可例如单层线路或多层线路的电路板。举例来说,图2所示的电路板12可包括多个上接垫12a、多个下接垫12b、上保护层12c、下保护层12d、多个内连线12e以及绝缘层12f,上保护层12c设置于绝缘层12f上并可具有开口曝露出上接垫12a,下保护层12d设置于绝缘层12f下并可具有开口曝露出下接垫12b,且内连线12e贯穿绝缘层12f,使得上接垫12a可通过对应的内连线12e电连接到对应的下接垫12b。电路板12的上表面12s可例如为上保护层12c的外表面,但不限于此。本发明的电路板12不以此为限,且可依据实际需求调整电路板12的结构。

52.如图1与图2所示,第一芯片161可例如通过芯片倒装焊方式与电路板12焊接并电连接。举例来说,第一芯片161可包括导电凸块161b,设置于第一芯片161的下表面,用以将第一芯片161焊接在电路板12的上接垫12a上。在一些实施例中,第一芯片161与电路板12的电连接方式不限为芯片倒装焊焊接,也可通过打线(wire bonding)方式达成。在一些实施例中,第一芯片161与电路板12之间例如还可设置有底部填充胶(underfill)22,用以增强第一芯片161与电路板12的焊接可靠度。在本实施例中,第二芯片162下可另设置有粘着层24,用以将第二芯片162粘贴于第一芯片161与间隔件14上。并且,第二芯片162可通过打线方式与间隔件14电连接。

53.本发明的芯片可例如为特殊应用集成电路(application specific integrated circuit,asic)芯片、存储器芯片或其他类型的芯片,但不限于此。存储器芯片可例如为快闪存储器(flash memory)芯片或其他类型的存储器芯片,但不限于此。不同的芯片可具有相同或不相同的功能。芯片也可被称为半导体芯片、芯片或集成电路芯片。在一实施例中,第一芯片161与第二芯片162可具有不同的功能。举例来说,第二芯片162可为存储器芯片,而第一芯片161可为asic芯片,用于控制或驱动存储器芯片。在此情况下,第一芯片161可具有较多的输入/输出接垫161a,因此可通过芯片倒装焊方式与电路板12焊接,而第二芯片162可具有较少的输入/输出接垫162a,因此第二芯片162可通过打线方式与间隔件14电连接。举例来说,第一芯片161的输入/输出接垫161a的数量可多于第二芯片162的输入/输出

接垫162a的数量,但不限于此。在一些实施例中,第一芯片161与第二芯片162也可具有相同功能,例如皆为存储器芯片。在此情况下,第一芯片161可通过打线方式与电路板12电连接,且第二芯片162可通过打线方式与间隔件14电连接。

54.间隔件14与第一芯片161并排设置于电路板12上,使得间隔件14与第一芯片161可用于支撑第二芯片162。举例来说,间隔件14可通过粘着层32粘贴在电路板12上。在本实施例中,间隔件14可包括间隔部14p以及至少一第一穿孔结构th1,且第一穿孔结构th1贯穿间隔部14p。间隔部14p可例如包括半导体材料、高分子材料或其他合适的支撑材料,但不限于此。半导体材料可例如包括硅,但不限于此。第一穿孔结构th1可包括导电材料。在图2所示的实施例中,间隔件14可包括多个第一穿孔结构th1,垂直贯穿间隔部14p,且间隔件14可另包括至少一个上接垫14a以及多个下接垫14b,上接垫14a设置于间隔部14p上并与对应的第一穿孔结构th1连接,下接垫14b设置于间隔部14p下并与对应的第一穿孔结构th1连接,使得上接垫14a可通过对应的第一穿孔结构th1电连接到对应的下接垫14b。下接垫14b可电连接至对应的电路板12的上接垫12a。举例来说,第一穿孔结构th1垂直贯穿间隔部14p,使得上接垫14a与下接垫14b在俯视方向vd上彼此重叠,且间隔件14可另包括连接件201,用以将下接垫14b电连接至电路板12的上接垫12a。在一实施例中,电路板12的上接垫12a与间隔件14的下接垫14b在俯视方向vd上可不重叠,因此电路板12的至少一上接垫12a可与至少一第一穿孔结构th1在芯片封装结构1的俯视方向vd上不重叠,但不以此为限。在图2所示的实施例中,连接件201可例如为单一导电层。导电层可例如包括金属或其他适合的导电材料。虽然图2中的连接件201与下接垫14b未连接,但实际上连接件201可在其他地方与下接垫14b连接,以将彼此对应的下接垫14b与上接垫12a电连接。下接垫14b与连接件201可由相同的导电层所形成或由不同的导电层所形成。所述导电层可例如包括金属或其他合适的导电材料,但不限于此。在一些实施例中,连接件201可例如包括重布线层,但不限于此。需说明的是,为了降低设置在间隔件14与第一芯片161上的第二芯片162的倾斜,间隔件14的间隔部14p的上表面14s的高度与第一芯片161的上表面161s可实质上位于同一水平面,举例来说,间隔部14p的上表面14s与电路板12的上表面12s之间的间距以及第一芯片161的上表面161s与电路板12的上表面12s之间的间距可大致上相同。

55.如图2所示,在一实施例中,芯片封装结构1可包括至少一条第一焊线181,从第二芯片162(例如第二芯片162的输入/输出接垫162a)延伸到间隔件14(例如间隔件14的上接垫14a),使得第二芯片162可通过第一焊线181电连接到间隔件14的上接垫14a、第一穿孔结构th1与下接垫14b,进而通过间隔件14电连接到电路板12。在一实施例中,第一焊线181的一端可直接与第二芯片162的输入/输出接垫162a焊接,另一端可直接与间隔件14的上接垫14a焊接,但本发明不限于此。值得一提的是,由于间隔件14的上接垫14a的高度高于电路板12的上接垫12a的高度,因此第一焊线181的长度可缩短,以降低第一焊线181的电阻值。并且,间隔件14的第一穿孔结构th1的电阻值可小于第一焊线181的电阻值,因此第二芯片162电连接到电路板12的电阻值可有效地降低,进而提升芯片封装结构1的效能或降低芯片封装结构1的功率消耗。此外,由于第一焊线181投影在水平方向上的长度l1可缩短,因此可缩减芯片封装结构1在水平方向上的整体宽度w1。

56.在一些实施例中,如图1与图2所示,芯片封装结构1还可包括第三芯片163、另一粘着层26以及至少一条第二焊线182。需说明的是,虽然图2同时显示第一焊线181与第二焊线

182,但第一焊线181与第二焊线182可位于不同的剖面上。第三芯片163通过粘着层26粘贴在第二芯片162上,且第二焊线182从第三芯片163的输入/输出接垫163a(第三芯片163的上表面)延伸到间隔件14的上接垫14a,用以将第三芯片163电连接到间隔件14中的第一穿孔结构th1,因此第三芯片163可通过第二焊线182与间隔件14电连接到电路板12。在一实施例中,第二焊线182的一端可直接与第三芯片163的输入/输出接垫163a焊接,另一端可直接与间隔件14对应的上接垫14a焊接,但本发明不限于此。需注意的是,第三芯片163与第二芯片162可分别电连接至不同且彼此绝缘的上接垫14a,以传送不同的信号。在一些实施例中,当第三芯片163的其中一输入/输出接垫163a与第二芯片162的其中一输入/输出接垫162a传送相同的信号时,所述输入/输出接垫163a与对应的输入/输出接垫162a可电连接至相同或彼此电连接的上接垫14a。值得说明的是,第二焊线182的长度可因间隔件14的设置而缩短,进而降低第二焊线182的电阻值,以提升芯片封装结构1的效能或降低芯片封装结构1的功率消耗。并且,由于间隔件14的设置降低了第二焊线182两端的高低落差,因此可降低第二焊线182高于第三芯片163的部分的高度,还可缩短第二焊线182投影在水平方向上的长度l2,进而缩减芯片封装结构1在水平方向上的整体宽度w1。在一些实施例中,第三芯片163可与第二芯片162具有相同的功能,例如皆为存储器芯片。粘着层24、26、32可例如分别包括芯片粘着膜(die attach film,daf)或其他适合的绝缘粘着材料。

57.在一些实施例中,芯片封装结构1可包括多个间隔件14、多个第二芯片162以及多个第三芯片163。在图1与图2所示的芯片封装结构1的实施例中,间隔件14的数量、第二芯片162的数量以及第三芯片163的数量以两个为例,但不限于此。在一些实施例中,间隔件14可分别设置于第一芯片161的两侧,举例来说,间隔件14的第一穿孔结构th1可位于堆叠芯片的外侧,但不限于此。第二芯片162除了设置于对应的间隔件14上之外可堆叠在同一第一芯片161上,且第三芯片163可分别设置在对应的第二芯片162上,使得第二芯片162与第三芯片163皆可通过间隔件14电连接到电路板12,以缩减第一焊线181与第二焊线182的电阻值。在一些实施例中,每个间隔件14可具有类似或相同的结构,每个第二芯片162可具有类似或相同的功能,每个第三芯片163可具有类似或相同的功能,但不以此为限。

58.在一些实施例中,芯片封装结构1还可包括封装胶体28,设置于第一芯片161、第二芯片162、第三芯片163、第一焊线181、第二焊线182与间隔件14上,并将其密封在电路板12上,因此可用以保护芯片、焊线与间隔件14。在一些实施例中,芯片封装结构1还可包括多个导电球30,分别设置在电路板12的下接垫12b上,使芯片封装结构1可进一步设置并电连接至其他元件、载板或电路板上。

59.本发明的芯片封装结构并不以上述实施例为限,且以下将进一步描述本揭露的其他实施例。为方便比较各实施例与简化说明,下文中将使用相同标号标注相同元件,且下文将详述不同实施例之间的差异,并不再对相同部分作赘述。

60.请参考图3,其绘示本发明第二实施例的芯片封装结构的剖视示意图。本实施例的芯片封装结构2与上述实施例的差异在于,连接件202可包括重布线层,形成于间隔部14p的下表面与下接垫14b上。在图3的实施例中,重布线层可包括两层介电层34、36以及一层导电层38,导电层38设置于介电层34、36之间,且介电层34可具有开口,使导电层38可通过介电层34的开口与下接垫14b电连接。另外,介电层36可具有开口,对应电路板12的上接垫12a,使得导电层38可通过导电凸块40电连接到电路板12。在一些实施例中,重布线层可包括三

层或更多的介电层以及两层或更多的导电层。

61.请参考图4,其绘示本发明第三实施例的芯片封装结构的剖视示意图。本实施例的芯片封装结构3与上述实施例的差异在于,芯片封装结构3可另包括至少一第三焊线183,从第一芯片161的上表面161s延伸到电路板12的其中一上接垫12a,使第一芯片161可通过第三焊线183电连接至电路板12。举例来说,第一芯片161可具有较少的接垫,因此接垫设置在第一芯片161的上表面161s。第一芯片161与第二芯片162可例如具有相同功能,例如均为存储器芯片。在一些实施例中,第三焊线183的数量不限如图3所示,且可为多条。需说明的是,用于将第二芯片162粘贴在第一芯片161上的粘着层24的厚度需大于第三焊线183位于第一芯片161的上表面161s上的部分的高度,以降低第二芯片162的设置对第三焊线183的损坏。在一些实施例中,芯片封装结构3可具有图2或图3所示的实施例或两者的组合的内容。

62.请参考图5,其绘示本发明第四实施例的芯片封装结构的剖视示意图。本实施例的芯片封装结构4与上述实施例的差异在于,在水平方向(例如方向d1)上,第二芯片462的宽度w2大于第一芯片161的宽度w3。在一些实施例中,第二芯片462的面积可大于第一芯片161的面积,但不限于此。在图5的实施例中,芯片封装结构4可仅包括单一第二芯片462,设置在第一芯片161与两间隔件14上,且第三芯片163设置在第二芯片462上,但本发明不以此为限。在一些实施例中,第二芯片462的范围可依据实际需求调整,而堆叠在第一芯片161与至少一间隔件14上。在一些实施例中,芯片封装结构4可具有图2、图3或图4所示的实施例或两者的组合的内容。

63.请参考图6,其绘示本发明第五实施例的芯片封装结构的剖视示意图。本实施例的芯片封装结构5与上述实施例的差异在于,至少一个第二芯片562可另包括芯片主体562m、至少一第二穿孔结构th2以及接垫562a,第二穿孔结构th2贯穿芯片主体562m从芯片主体562m的上表面562s1延伸到芯片主体562m的下表面562s2,且第二焊线182系从第三芯片163的上表面163s延伸到第二芯片562的接垫562a。在一实施例中,第二穿孔结构th2在俯视方向vd上可与接垫562a重叠。此外,第二芯片562还可包括连接件542,设置于芯片主体562m的下表面562s2上,并与第二穿孔结构th2电连接。通过连接件542,电连接第二焊线182的第二芯片562的接垫562a可电连接到间隔件14的上接垫14a。在一实施例中,间隔件14与第二穿孔结构th2电连接的第一穿孔结构th1可在俯视方向vd上可与第二芯片562重叠,使得连接件542可通过间隔件14的上接垫14a与第一穿孔结构th1电连接。在一实施例中,彼此电连接的第一穿孔结构th1与第二穿孔结构th2在俯视方向vd上可重叠或不重叠。需注意的是,接垫562a与芯片主体562m中的元件562d是电性绝缘,也就是说,接垫562a不同于第二芯片562中用于元件562d的信号输入或输出的输入/输出接垫162a(如图1所示)。并且,第二芯片562的输入/输出接垫162a(如图1所示)仍可通过第一焊线181电连接到间隔件14。在图6的实施例中,连接件542可例如为单层导电层,但不限于此。所述导电层可例如包括金属或其他合适的导电材料,但不限于此。在一些实施例中,芯片封装结构5可仅包括单一个第三芯片163,通过粘着层26设置于至少两个第二芯片562上。在一些实施例中,芯片封装结构5可具有图2、图3、图4或图5所示的实施例或上述实施例的任两者的组合的内容。

64.值得说明的是,通过第二穿孔结构th2的设置,第二焊线182仅需从第三芯片163的上表面163s延伸到第二芯片562的接垫562a,而不需延伸到位于第二芯片562下的间隔件14,因此可降低第二焊线182的长度。例如,缩短第二焊线182投影在水平方向(例如方向d1)

的长度l2,或降低第二焊线182位于第三芯片163的上表面163s上的部分的高度。因此,可提升芯片封装结构5的效能或降低芯片封装结构5的功率消耗,还可降低芯片封装结构5的整体宽度w1。

65.请参考图7,其绘示本发明第六实施例的芯片封装结构的剖视示意图。本实施例的芯片封装结构6与上述实施例的差异在于,第二芯片562的连接件642可包括重布线层,形成于芯片主体562m的下表面562s2上。在图7的实施例中,重布线层可包括两层介电层44、46以及一层导电层48,导电层48设置于介电层44、46之间,且介电层44可具有开口,使导电层48可通过介电层44的开口与第二穿孔结构th2电连接。另外,介电层46可具有开口,对应间隔件14的上接垫14a,使得导电层48可通过导电凸块50电连接到间隔件14,进而电连接到电路板12。在一些实施例中,重布线层可包括三层或更多的介电层以及两层或更多的导电层。所述导电层可例如包括金属或其他合适的导电材料,但不限于此。在一些实施例中,芯片封装结构6可具有图2、图3、图4或图5所示的实施例或上述实施例的任两者的组合的内容。

66.综合上述,在本发明的芯片封装结构中,通过具有穿孔结构的间隔件及/或具有穿孔结构的芯片,可有效地焊线的长度,以降低焊线的电阻值。藉此,可提升芯片封装结构的效能或降低芯片封装结构的功率消耗,还可降低芯片封装结构的整体宽度。

67.以上所述仅为本发明的较佳实施例,凡依本发明权利要求范围所做的均等变化与修饰,皆应属本发明的涵盖范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1