封装结构的制作方法

1.本发明涉及封装结构,特别是涉及包含阻气层的封装结构。

背景技术:

2.随着电子元件工业技术的进步,电子元件已自硬质不可挠曲特性朝向软性可挠曲特性发展,此发展过程伴随着电子元件所使用的材质的改变。举例而言,可挠性基板已在许多应用中取代了硬质玻璃基板,同时电子元件中的各项构件也逐渐发展出以可挠性材料,例如有机材料来制作。可挠性电子元件采用有机材料制作时,阻隔水气与氧气的能力一直是亟待解决的问题。为求有效延长可挠性电子元件的寿命,各种封装结构都着重于阻隔水气与氧气的技术手段。

3.若采用整面阻气层覆盖可挠基板上的所有电子元件,将会降低可挠基板的可挠性。另一方面,整面的阻气层若过薄则无法达到阻水阻气的效果,但整面的阻气层若过厚则会使基板不具可挠性,或可挠基板挠曲时造成整面阻气层破裂而劣化其阻气效果。综上所述,目前亟需新的结构设计以兼具可挠基板的可挠性与阻气层的阻气性。

技术实现要素:

4.本发明一实施例提供的封装结构,包括:可挠基板,具有元件区与非元件区;多个电子元件,位于可挠基板的元件区中;第一挡墙,围绕电子元件的一或多者;第二挡墙,围绕第一挡墙,且第一挡墙与第二挡墙之间具有沟槽;以及第一阻气层,覆盖电子元件与第一挡墙的表面,其中第一挡墙表面的表面能大于第二挡墙表面的表面能。

5.本发明一实施例提供的封装结构,包括:可挠基板;多个电子元件,位于可挠基板上;第一阻气层,覆盖电子元件的一或多者的侧壁与上表面;以及软性结构,位于可挠基板上,阻气层位于软性结构与电子元件之一或多者之间,且软性结构的杨氏系数大于或等于0.02gpa且小于2gpa。

附图说明

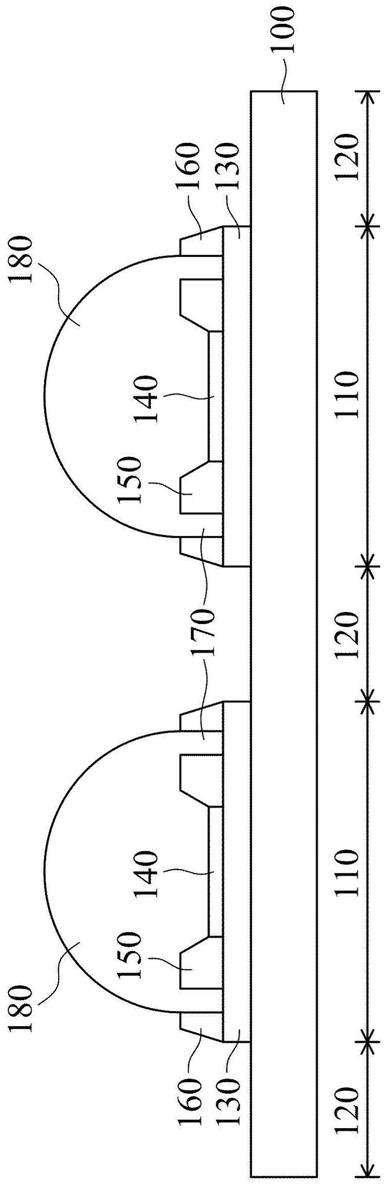

6.图1至图6为本发明实施例中,封装结构的剖视图;

7.图7a至图7e、图8a至图8e、图9a至图9e、图10a至图10e、图 11a至图11e、图12a至图12e、图13a至图13e、图14a至图14e、图 15a至图15e、图16a至图16e、图17a至图17e、与图18a至图18e为本发明实施例中,封装结构于制作工艺的中间阶段的剖视图。

8.符号说明

9.100 可挠基板

10.110 元件区

11.120 非元件区

12.130 装置

13.140 电子元件

14.150 第一挡墙

15.160 第二挡墙

16.170 沟槽

17.175 缓冲层

18.180 溶液

19.190、190’、195、195

’ꢀ

阻气层

20.200 软性结构

具体实施方式

21.本发明一实施例的封装结构如图1所示。在图1中,可挠基板100具有元件区110与非元件区120。在图1中,元件区110的装置130高于可挠基板100,但应理解装置130可嵌置于可挠基板100中,意即装置130的上表面可低于可挠基板100的上表面,或与可挠基板100的上表面等高。举例来说,可挠基板100的材质可为聚酰亚胺、硅胶或聚碳酸酯,其杨氏系数可介于0.1gpa至20gpa之间。一般而言,装置130可包含有源装置如晶体管、存储器或类似装置;无源装置如电容、电阻、电感、或类似装置或上述的组合。可挠基板100可具有内连线结构如线路或通孔,其电连接不同元件区110 中的装置130,以形成功能电路。

22.如图1所示,电子元件140位于装置130上,即位于可挠基板100的元件区110中。在本发明一实施例中,电子元件140可为电激发光元件 (electroluminescence,el)、量子点发光体(quantum dot,qd)。以三色发光装置为例,一个像素可至少具有红光二极管、绿光二极管与蓝光二极管等次像素,而电子元件140可视作像素中的一个次像素。

23.如图1所示,第一挡墙150围绕单一的电子元件140。值得注意的是,虽然图1中的第一挡墙150只围绕单一的电子元件140。但第一挡墙150可围绕一行或一列(比如1

×

n或n

×

1)的电子元件140。另一方面,第一挡墙150 可围绕一块区域(比如n

×

n)的电子元件140。举例来说,第一挡墙150可围绕一个像素区的电子元件140,比如三个次像素的电子元件140。

24.如图1所示,第二挡墙160围绕第一挡墙150,且第一挡墙150与第二挡墙160之间具有沟槽170。在一实施例中,沟槽170可不完全贯穿(如图1) 至暴露出装置130的表面,通过搭配具阻气特性的第一挡墙150与第二挡墙 160,可避免水气及/或氧气从侧面进入电子元件140。第一挡墙150的高度可等于第二挡墙160的高度。第一挡墙150表面的表面能可大于第二挡墙 160表面的表面能。在一实施例中,第一挡墙150表面的表面能,比第二挡墙160表面的表面能大5mn/m至40mn/m之间。若第一挡墙150表面的表面能与第二挡墙160表面的表面能差距过小,后述溶液180可能溢流出第二挡墙160至可挠基板100的非元件区120。若第一挡墙150表面的表面能与第二挡墙160表面的表面能的差距过大,则第一挡墙150不易被涂布覆盖。

25.在一实施例中,第一挡墙150与第二挡墙160形成方法可为喷墨涂布制作工艺或光刻蚀刻制作工艺等图案化制作工艺。在形成第一挡墙150与第二挡墙160之后,可利用荫罩(shadow mask)露出第一挡墙150的表面,以例如红外线直写或氧气等离子体进行表面处理,使第一挡墙150表面的表面能大于第二挡墙160表面的表面能。另一方面,可利用荫罩露出第二挡墙的表面并进行例如氩气或氮气等离子体处理,使第一挡墙的150表面的表面能大于第二挡墙160表面的表面能。此外,可先形成第一挡墙150,再以紫外线、等离子体、红外

线或化学改质第一挡墙150的表面,之后再形成第二挡墙160,使第一挡墙150表面的表面能大于第二挡墙160表面的表面能。另一方面,可由不同材质分别形成第一挡墙150与第二挡墙160,且第一挡墙150表面的表面能大于第二挡墙160表面的表面能。举例来说,第一挡墙150的组成可为聚硅氮氧烷、环氧树脂或酚醛树脂等;而第二挡墙160的组成可为氮氧化硅、压克力、聚胺酯等。采用不同材质形成第一挡墙150与第二挡墙160 的作法,可进一步搭配紫外线、等离子体、红外线或化学改质第一挡墙150(或第二挡墙160)表面的步骤。

26.在一些实施例中,第一挡墙150的高度介于0.1μm至5μm之间。若第一挡墙150的高度过低,溶液180可能溢流出第二挡墙160至可挠基板100 的非元件区120。若第一挡墙150的高度过高,不易封装完整而导致侧向阻气失效。在一些实施例中,沟槽170的宽度介于0.1μm至500μm之间。若沟槽170的宽度过小,难以阻挡溶液180的溢流。若沟槽170的宽度过大,容易形成元件脆弱区。

27.如图1所示,溶液180覆盖电子元件140与第一挡墙150,且溶液180 可能填入沟槽170。溶液180的施加方法可例如为涂布等方式制作,涂布方式可以为旋转涂布、刮刀涂布、狭缝式涂布、浸泡涂布、喷墨式涂布、网印涂布等。在一实施例中,溶液180的组成可为聚硅氮氧烷、氮氧化硅或类似物。由于第一挡墙150表面的表面能大于第二挡墙160表面的表面能,可避免施加溶液180时溢流至第二挡墙160之外,覆盖第二挡墙160之外的可挠基板100的表面(如非元件区120的表面)而降低封装结构的可挠性。

28.接着如图2所示,使溶液180干燥并进行表面处理以形成阻气层190,阻气层190覆盖电子元件140与第一挡墙150的表面,其中表面处理包括照光、加热或等离子体等处理方式,对阻气层190的外露表面进行改质,经改质的阻气层190表面可具有较高的致密性,用于增进阻气层190的阻障特性。此外,经受等离子体处理的阻气层190的表面可还包括掺杂元素。掺杂元素可为等离子体使用气体的组成元素,其包括氩、氢、氮、氧、惰性气体或上述的组合等。在部分的实施例中,掺杂元素在阻气层190中占有含量可以为超过0at%至5at%,其中at%为原子百分比。上述阻气层190可完全密封第一挡墙150的表面与电子元件140的表面,可避免水气及/或氧气自第一挡墙150的侧部进入电子元件140。值得注意的是,阻气层190可以只覆盖第一挡墙150的部分表面,但阻气层190也可能会覆盖至沟槽170的底部,甚至沟槽170中的第二挡墙160的部分表面。在一实施例中,电子元件 140上的阻气层190的厚度与第一挡墙150的高度的比例可介于0.02:1至1:1之间。若阻气层190的厚度过小,则无法达到阻挡水气与氧气的效果。若阻气层190的厚度过大,则可能一开始使用的溶液180的量过大,其可能会超出第一挡墙150围绕的空间与沟槽170的容量,使溶液180溢流至第二挡墙160之外。

29.如图3所示,若溶液180会损伤电子元件140,可在形成溶液180之前,先形成缓冲层175于电子元件140上,缓冲层175同时兼具填补、覆盖缺陷的功用,以保护电子元件140免于溶液180的影响。在一实施例中,缓冲层 175的材料可例如是丙烯酸树脂、环氧树脂、酚醛树脂或类似物。在形成溶液180之后使之干燥,并进行表面处理以形成如图4所示的结构示意图。在图4中,缓冲层175位于该电子元件140与阻气层190之间。在一实施例中,缓冲层175的厚度与挡墙的高度的比例可介于0.5:1至0.98:1之间。若缓冲层175的厚度过大,则溶液180的用量减少,即溶液180干燥后所形成的阻气层190的厚度可能不足。若缓冲层175的厚度过小,可能无法避免溶液180损伤电子元件140。在一实施例中,缓冲层175与阻气层190的总厚

度与第一挡墙150的高度的比例可介于0.52:1至1:1之间。若缓冲层175与阻气层190的总厚度过小,则无法达到阻挡水气及/或氧气的效果。若缓冲层 175与阻气层190的总厚度过大,则可能一开始使用的溶液180的量过大而超出第一挡墙150围绕的空间与沟槽170的容量,使溶液180溢流至第二挡墙160之外。缓冲层175除了保护电子元件140不受溶液180损伤之外,也可进一步阻挡水气及/或氧气进入电子元件140。不过缓冲层175是作为辅助,仍无法省略阻气层190。

30.在一实施例中,第一挡墙150可高于第二挡墙160,如图5所示。在另一实施例中,第一挡墙150可低于第二挡墙160,如图6所示。值得注意的是,虽然图5与6中的电子元件140上具有缓冲层175,但可视情况省略缓冲层175,即溶液180可直接接触电子元件140。之后可使图5与6的溶液 180干燥并进行表面处理以形成阻气层190(未图示)。不论第二挡墙160高于或低于第一挡墙150,阻气层190均覆盖电子单元140(或视情况采用的缓冲层175)与第一挡墙150的表面。阻气层190可能覆盖沟槽170的底部,甚至覆盖沟槽170中第二挡墙160的表面。

31.在一实施例中,第二挡墙160可为软性结构。举例来说,第二挡墙160 的杨氏系数大于或等于0.2gpa且小于2gpa。软性结构有利于改善封装结构的可挠性。另一方面,此软性结构(即第二挡墙160)表面的表面能仍小于第一挡墙150表面的表面能,如上所述。在一些实施例中,软性结构的组成可为硅胶、压克力系列高分子、聚胺酯或环氧树脂等,其形成方法可为涂布、沉积或蒸镀。

32.在上述附图中,第一挡墙150可围绕单一的电子元件140。如此一来,阻气层190覆盖的上视面积与元件区110及非元件区120的总面积的比例,可大于0.01并小于0.32。值得注意的是,虽然图1中的第一挡墙150只围绕单一的电子元件140。但第一挡墙150可围绕一行或一列(比如1

×

n或n

×

1) 的电子元件140。另一方面,第一挡墙150可围绕一块区域(比如n

×

n)的电子元件140。举例来说,第一挡墙150可围绕一个像素区,比如三个次像素的电子元件140。在第一挡墙150围绕一个像素区的实施例中,阻气层190覆盖的上视面积与元件区110及非元件区120的总面积的比例,可大于0.45并小于0.97。在第一挡墙150围绕多个像素区的实施例中,阻气层190覆盖的上视面积与元件区110及非元件区120的总面积的比例,可大于0.7并小于等于0.97。可以理解的是,第一挡墙150并未围绕所有的电子元件140。若第一挡墙150围绕所有的电子元件140,则阻气层190覆盖的上视面积与元件区110及非元件区120的总面积的比例等于1,即无法避免现有技术中整面阻气层的缺点:降低封装结构的可挠性,且整面阻气层190在挠曲时可能破损而劣化其阻气性。

33.在一实施例中,封装结构包括可挠基板,以及多个电子元件位于可挠基板上。封装结构也包括阻气层覆盖电子元件的一或多者的侧壁与上表面。封装结构也包括软性结构位于可挠基板上,阻气层位于软性结构与电子元件之一或多者之间,且软性结构的杨氏系数大于或等于0.2gpa且小于2gpa。位于可挠基板上的软性结构可改善封装结构的可挠性,而覆盖不同像素或次像素的电子元件的阻气层未连接,即未覆盖可挠基板的所有表面,有助于避免现有技术中整面阻气层的缺点:降低封装结构的可挠性,且整面的阻气层在挠曲时可能破损而劣化其阻气性。在一实施例中,软性结构的高度介于0.1μm 至5μm间,而宽度介于0.1μm至5μm之间。若软性结构的高度或宽度过大,则不易完整封装而导致侧向阻气失效。若软性结构的高度或宽度过小,则不易制作。

34.在一实施例中,阻气层可包括氮氧化硅、氮化硅或上述的多层结构。

35.在一实施例中,封装结构更包括缓冲层配置于阻气层的多层结构之间或配置于阻气层与电子元件的一或多者之间。

36.在一实施例中,上述封装结构的形成方法如图7a至图7e所示。如图 7a所示,形成可挠基板100,其上具有装置130。虽然图7a中的装置130 为整层的结构,但也可为分开结构,如图1的装置130。电子元件140形成于装置130上。上述可挠基板100、装置130与电子元件140的细节与前述类似,在此不重述。如图7b所示,形成第一挡墙150以及第二挡墙160,并以表面处理第一挡墙150(或第二挡墙160)使两者的表面能不同。接着利用例如喷墨印刷形成缓冲层175以覆盖电子元件140。如图7c所示,接着喷涂溶液(如前述的溶液180)后使之干燥并进行表面处理,以形成阻气层190于缓冲层175与第一挡墙150的表面。如图7d所示,可选择性喷涂另一溶液 (如前述的溶液180)后使之干燥并进行表面处理,以形成另一阻气层190’于阻气层190的表面。覆盖各阻气层190的阻气层190’不相连,即不覆盖装置 130的所有表面。如图7e所示,接着形成软性结构200于不同像素或次像素的第二挡墙160之间,以增加封装结构的可挠性。可以理解的是,软性结构200的高度可大于、等于或小于开口的深度,只要能提高封装结构的可挠性即可。再者,软性结构200可接触或不接触第二挡墙160,本发明各实施例都可依需求调整之。虽然图7a至图7e的实施例中,一缓冲层175/阻气层190/阻气层190’只覆盖单一的电子元件140,但也可覆盖多个(而非所有) 电子元件140如前述。另一方面,可在表面处理第一挡墙150及/或第二挡墙 160之后即形成软性结构200,而不需在形成阻气层190’之后才形成软性结构200。此外,第二挡墙160本身也可为软性结构,因此可省略软性结构200。如此一来,通过省略软性结构200所占空间,可使电子元件140的排列更紧密。

37.本发明一实施例中,封装结构的形成方法如图8a至图8e所示。图8a 的可挠基板100、装置130与电子元件140的细节与前述类似,在此不重述。如图8b所示,形成第一挡墙150,并表面处理第一挡墙150的内侧表面,使内侧表面与外侧表面的表面能不同。接着利用例如喷墨印刷形成缓冲层 175以覆盖电子元件140。如图8c所示,接着涂布溶液(如前述的溶液180) 后使之干燥并进行表面处理,以形成阻气层190于上述结构的表面。如图8d 所示,可选择性涂布另一溶液(如前述的溶液180)后使之干燥并进行表面处理,以形成另一阻气层190’于阻气层190的表面。如图8e所示,接着移除第一挡墙150之间的阻气层190与另一阻气层190’以露出装置130的上表面,并形成软性结构200于不同像素或次像素的第一挡墙150之间,以增加封装结构的可挠性。在一实施例中,移除阻气层190与另一阻气层190’的制作工艺可为光刻搭配蚀刻制作工艺、激光制作工艺或其他可适用的图案化方法,且蚀刻制作工艺可为各向异性的干蚀刻。可以理解的是,软性结构200 的高度可大于、等于或小于第一挡墙150的高度,只要能提高封装结构的可挠性即可。再者,软性结构200可接触或不接触第一挡墙150及/或阻气层 190、190’,本发明各实施例都可依需求调整之。虽然图8a至图8e的实施例中,一缓冲层175/阻气层190/阻气层190’只覆盖单一的电子元件140,但也可覆盖多个(而非所有)电子元件140如前述。

38.在一实施例中,上述封装结构的形成方法如图9a至图9e所示。图9a 的可挠基板100、装置130与电子元件140的细节与前述类似,在此不重述。如图9b所示,形成第一挡墙150以及第二挡墙160,并以表面处理第一挡墙150(或第二挡墙160)使两者的表面能不同。

接着利用例如喷墨印刷形成缓冲层175以覆盖电子元件140。如图9c所示,接着喷涂溶液(如前述的溶液 180)后使之干燥并进行表面处理,以形成阻气层190于缓冲层175与第一挡墙150的表面。如图9d所示,可涂布另一溶液(如前述的溶液180)后使之干燥并进行表面处理,以形成另一阻气层190’于图9c所示的结构表面上。如图9e所示,接着移除第二挡墙160之间的阻气层190’以露出装置130的上表面,并形成软性结构200于不同像素或次像素的第二挡墙160之间,以增加封装结构的可挠性。在一实施例中,移除阻气层190’的制作工艺可为光刻搭配蚀刻制作工艺、激光制作工艺或其他可适用的图案化方法,且蚀刻制作工艺可为各向异性的干蚀刻。可以理解的是,软性结构200的高度可大于、等于或小于第二挡墙160的高度,只要能提高封装结构的可挠性即可。再者,软性结构200可接触或不接触第二挡墙160及/或阻气层190’,本发明各实施例都可依需求调整之。虽然图9a至9e的实施例中,一缓冲层175/阻气层190/阻气层190’只覆盖单一的电子元件140,但也可覆盖多个(而非所有) 电子元件140如前述。此外,第二挡墙160本身也可为软性结构,因此可省略软性结构200。如此一来,通过省略软性结构200所占空间,可使电子元件140的排列更紧密。

39.在一实施例中,上述封装结构的形成方法如图10a至图10e所示。图 10a的可挠基板100、装置130与电子元件140的细节与前述类似,在此不重述。如图10b所示,形成第一挡墙150以及第二挡墙160,并以表面处理第一挡墙150(或第二挡墙160)使两者的表面能不同。接着利用例如喷墨印刷形成缓冲层175以覆盖电子元件140。如图10c所示,接着喷涂溶液(如前述的溶液180)后使之干燥并进行表面处理,以形成阻气层190于缓冲层175与第一挡墙150的表面。如图10d所示,例如以化学气相沉积方式、物理气相沉积、蒸镀或溅镀等形成阻气层195于图10c所示的结构表面上。在一些实施例中,阻气层195可为氮化硅、氧化硅或氮氧化硅等。如图10e所示,接着移除第二挡墙150之间的阻气层195以露出装置130的上表面,并形成软性结构200于不同像素或次像素的第二挡墙160之间,以增加封装结构的可挠性。在一实施例中,移除阻气层190与阻气层195的制作工艺可为光刻搭配蚀刻制作工艺、激光制作工艺或其他可适用的图案化方法,且蚀刻制作工艺可为各向异性的干蚀刻。可以理解的是,软性结构200的高度可大于、等于或小于第二挡墙160的高度,只要能提高封装结构的可挠性即可。再者,软性结构200可接触或不接触第二挡墙160及/或阻气层195,本发明各实施例都可依需求调整之。虽然图9a至图9e的实施例中,一缓冲层175/阻气层190/阻气层195只覆盖单一的电子元件140,但也可覆盖多个(而非所有) 电子元件140如前述。此外,第二挡墙160本身也可为软性结构,因此可省略软性结构200。如此一来,通过省略软性结构200所占空间,可使电子元件140的排列更紧密。

40.本发明一实施例中,封装结构的形成方法如图11a至图11e所示。图 11a的可挠基板100、装置130与电子元件140的细节与前述类似,在此不重述。如图11b所示,形成第一挡墙150,并表面处理第一挡墙150的内侧表面,使内侧表面与外侧表面的表面能不同。接着利用例如喷墨印刷形成缓冲层175以覆盖电子元件140。如图11c所示,例如以化学气相沉积方式、物理气相沉积、蒸镀或溅镀等形成阻气层195于缓冲层175、第一挡墙150 及装置130的表面上。如图11d所示,接着涂布溶液(如前述的溶液180)后使之干燥并进行表面处理,以形成阻气层190于阻气层195上。如图11e所示,接着移除第一挡墙150之间的阻气层195与阻气层190以露出装置130 的上表面,并形成软性结构200于不同像素或次像素的第一挡墙150之间,以增加封装结构的可挠性。在一实施例中,移除阻气层195与阻气层190的制作工艺可

为光刻搭配蚀刻制作工艺、激光制作工艺或其他可适用的图案化方法,且蚀刻制作工艺可为各向异性的干蚀刻。可以理解的是,软性结构200 的高度可大于、等于或小于第一挡墙150的高度,只要能提高封装结构的可挠性即可。再者,软性结构200可接触或不接触第一挡墙150及/或阻气层 190、195,本发明各实施例都可依需求调整之。虽然图11a至图11e的实施例中,一缓冲层175/阻气层195/阻气层190只覆盖单一的电子元件140,但也可覆盖多个(而非所有)电子元件140如前述。

41.本发明一实施例中,封装结构的形成方法如图12a至图12e所示。图 12a的可挠基板100、装置130与电子元件140的细节与前述类似,在此不重述。如图12b所示,形成第一挡墙150,并表面处理第一挡墙150的内侧表面,使内侧表面与外侧表面的表面能不同。接着利用例如喷墨印刷形成缓冲层175以覆盖电子元件140。如图12c所示,接着涂布溶液(如前述的溶液 180)后使之干燥并进行表面处理,以形成阻气层190于上述结构上。如图12d 所示,例如以化学气相沉积方式、物理气相沉积、蒸镀或溅镀等形成阻气层 195于阻气层190的表面上。如图11e所示,接着移除第一挡墙150之间的阻气层190与阻气层195以露出装置130的上表面,并形成软性结构200于不同像素或次像素的第一挡墙150之间,以增加封装结构的可挠性。在一实施例中,移除阻气层190与阻气层195的制作工艺可为光刻搭配蚀刻制作工艺、激光制作工艺或其他可适用的图案化方法,且蚀刻制作工艺可为各向异性的干蚀刻。可以理解的是,软性结构200的高度可大于、等于或小于第一挡墙150的高度,只要能提高封装结构的可挠性即可。再者,软性结构200 可接触或不接触第一挡墙150及/或阻气层190、195,本发明各实施例都可依需求调整之。虽然图12a至图12e的实施例中,一缓冲层175/阻气层190/ 阻气层195只覆盖单一的电子元件140,但也可覆盖多个(而非所有)电子元件140如前述。

42.本发明一实施例中,封装结构的形成方法如图13a至图13e所示。图 13a的可挠基板100、装置130与电子元件140的细节与前述类似,在此不重述。如图13b所示,利用例如喷墨印刷形成缓冲层175以覆盖电子元件 140。如图13c所示,例如以化学气相沉积方式、物理气相沉积、蒸镀或溅镀等形成阻气层195于缓冲层175、第一挡墙150及装置130的表面上。接着利用例如光刻搭配蚀刻制作工艺、激光制作工艺或其他可适用的图案化方法移除缓冲层175与第一挡墙150上以外的阻气层195。如图13d所示,阻气层195’于阻气层195及装置130的表面上。在一实施例中,阻气层195’的材料选择与前述的阻气层195类似。阻气层195’与阻气层195的组成可相同或不同。在一些实施例中,阻气层195与195’可各自为氮化硅、氧化硅或氮氧化硅等。接着移除阻气层195上以外的其他阻气层195’,使覆盖各阻气层 195的阻气层195’不相连,即不覆盖装置130的所有表面。如图13e所示,形成软性结构200于不同像素或次像素的阻气层195’之间,以增加封装结构的可挠性。可以理解的是,软性结构200的高度可大于、等于或小于开口的深度,只要能提高封装结构的可挠性即可。虽然图13a至图13e的实施例中,一缓冲层175/阻气层195/阻气层195'只覆盖单一的电子元件140,但也可覆盖多个(而非所有)电子元件140如前述。另一方面,可在形成缓冲层175 之后即形成软性结构200,而不需在形成阻气层195’之后才形成软性结构200。

43.在一实施例中,上述封装结构的形成方法如图14a至图14e所示。图 14a的可挠基板100、装置130与电子元件140的细节与前述类似,在此不重述。如图14b所示,形成第一挡墙150以及第二挡墙160,并以表面处理第一挡墙150(或第二挡墙160)使两者的表面能不

同。接着喷涂溶液(如前述的溶液180)后使之干燥并进行表面处理,以形成阻气层190于电子元件140 与第一挡墙150的表面上。如图14c所示,接着利用例如喷墨印刷形成缓冲层175于阻气层190的表面上。如图14d所示,喷涂溶液(如前述的溶液180) 后使之干燥并进行表面处理,以形成阻气层190’于缓冲层175的表面上。覆盖各缓冲层175的阻气层190’不相连,即不覆盖装置130的所有表面。如图 14e所示,接着形成软性结构200于不同像素或次像素的第二挡墙160之间,以增加封装结构的可挠性。可以理解的是,软性结构200的高度可大于、等于或小于开口的深度,只要能提高封装结构的可挠性即可。虽然图14a至图 14e的实施例中,一阻气层190/缓冲层175/阻气层190’只覆盖单一的电子元件140,但也可覆盖多个(而非所有)电子元件140如前述。另一方面,可在表面处理第一挡墙150及/或第二挡墙160之后即形成软性结构200,而不需在形成阻气层190’之后才形成软性结构200。此外,第二挡墙160本身也可为软性结构,因此可省略软性结构200。如此一来,通过省略软性结构200所占空间,可使电子元件140的排列更紧密。

44.本发明一实施例中,封装结构的形成方法如图15a至图15e所示。图15a的可挠基板100、装置130与电子元件140的细节与前述类似,在此不重述。如图15b所示,形成第一挡墙150以及第二挡墙160,并以表面处理第一挡墙150(或第二挡墙160)使两者的表面能不同。接着喷涂溶液(如前述的溶液180)后使之干燥并进行表面处理,形成阻气层190覆盖电子元件140。此步骤覆盖各电子元件140的阻气层190不相连,即不覆盖装置130的所有表面。如图15c所示,接着形成缓冲层175于阻气层190的表面。覆盖各阻气层190的缓冲层175不相连,即不覆盖装置130的所有表面。如图15d所示,接着涂布另一溶液(如前述的溶液180)后使之干燥并进行表面处理,形成另一阻气层190’于上述结构上。如图15e所示,移除第二挡墙160之间的阻气层190’以露出装置130的上表面,并形成软性结构200于不同像素或次像素的第二挡墙160之间,以增加封装结构的可挠性。在一实施例中,移除阻气层190’的制作工艺可为光刻搭配蚀刻制作工艺、激光制作工艺或其他可适用的图案化方法,且蚀刻制作工艺可为各向异性的干蚀刻。可以理解的是,软性结构200的高度可大于、等于或小于开口的深度,只要能提高封装结构的可挠性即可。虽然图15a至15e的实施例中,一阻气层190/缓冲层175/ 阻气层190’只覆盖单一的电子元件140,但也可覆盖多个(而非所有)电子元件140如前述。此外,第二挡墙160本身也可为软性结构,因此可省略软性结构200。如此一来,通过省略软性结构200所占空间,可使电子元件140 的排列更紧密。

45.本发明一实施例中,封装结构的形成方法如图16a至图16e所示。图 16a的可挠基板100、装置130与电子元件140的细节与前述类似,在此不重述。如图16b所示,形成第一挡墙150以及第二挡墙160,并以表面处理第一挡墙150(或第二挡墙160)使两者的表面能不同。接着喷涂溶液(如前述的溶液180)后使之干燥并进行表面处理,形成阻气层190覆盖电子元件140。此步骤覆盖各电子元件140的阻气层190不相连,即不覆盖装置130的所有表面。如图16c所示,接着形成缓冲层175于阻气层190的表面。覆盖各阻气层190的缓冲层175不相连,即不覆盖装置130的所有表面。如图16d所示,例如以化学气相沉积方式、物理气相沉积、蒸镀或溅镀等形成阻气层195 于缓冲层175、第二挡墙160及装置130的表面上。如图16e所示,移除第二挡墙160之间的阻气层195以露出装置130的上表面,并形成软性结构200于不同像素或次像素的第二挡墙160之间,以增加封装结构的可挠性。在一实施例中,移除阻气层195的制作工艺可为光刻搭配蚀刻制作工艺、激光制作工艺或其他可适用的图案化方法,

且蚀刻制作工艺可为各向异性的干蚀刻。可以理解的是,软性结构200的高度可大于、等于或小于开口的深度,只要能提高封装结构的可挠性即可。虽然图16a至16e的实施例中,一阻气层190/缓冲层175/阻气层195只覆盖单一的电子元件140,但也可覆盖多个(而非所有)电子元件140如前述。此外,第二挡墙160本身也可为软性结构,因此可省略软性结构200。如此一来,通过省略软性结构200所占空间,可使电子元件140的排列更紧密。

46.本发明一实施例中,封装结构的形成方法如图17a至图17e所示。图 17a的可挠基板100、装置130与电子元件140的细节与前述类似,在此不重述。如图17b所示,形成第一挡墙150与第二挡墙160,接着以例如化学气相沉积方式、物理气相沉积、蒸镀或溅镀等形成阻气层195于电子元件 140、第一挡墙150、第二挡墙160及装置130的表面上。接着可利用光刻搭配蚀刻制作工艺、激光制作工艺或其他可适用的图案化方法移除电子元件 140与第一挡墙150上以外的阻气层195。如图17c所示,表面处理第一挡墙150(或第二挡墙160)使两者的表面能不同。接着利用例如喷墨印刷形成缓冲层175于阻气层195的表面上。如图17d所示,以例如化学气相沉积方式、物理气相沉积、蒸镀或溅镀等形成阻气层195’形成于缓冲层175、第二挡墙160及装置130的表面上。接着移除缓冲层175上以外的阻气层195’,使覆盖各缓冲层175的阻气层195’不相连,即不覆盖装置130的所有表面。如图17e所示,接着形成软性结构200于不同像素或次像素的第二挡墙160 之间,以增加封装结构的可挠性。可以理解的是,软性结构200的高度可大于、等于或小于开口的深度,只要能提高封装结构的可挠性即可。虽然图17a 至图17e的实施例中,一阻气层195/缓冲层175/阻气层195'只覆盖单一的电子元件140,但也可覆盖多个(而非所有)电子元件140如前述。另一方面,也可在形成缓冲层175之后即形成软性结构200,而不需在形成阻气层195’之后才形成软性结构200。

47.在另一实施例中,可类似如图8b的做法,仅形成第一挡墙150,并表面处理第一挡墙150的内侧表面,使内侧表面与外侧表面的表面能不同。接着利用例如喷墨印刷形成缓冲层175以覆盖电子元件140,可由此省略第二挡墙160的制作。

48.本发明一实施例中,封装结构的形成方法如图18a至图18e所示。图 18a的可挠基板100、装置130与电子元件140的细节与前述类似,在此不重述。如图18b所示,形成第一挡墙150与第二挡墙160,接着以例如化学气相沉积方式、物理气相沉积、蒸镀或溅镀等形成阻气层195于电子元件 140、第一挡墙150、第二挡墙160及装置130的表面上。接着移除电子元件 140与第一挡墙150上以外的阻气层195。如图18c所示,表面处理第一挡墙150(或第二挡墙160)使两者的表面能不同。接着利用例如喷墨印刷形成缓冲层175于阻气层195的表面上。如图18d所示,涂布溶液(如前述的溶液180)于缓冲层175上,之后将溶液干燥并进行表面处理,以形成阻气层 190于图18c所示的结构表面上。接着移除第二挡墙160之间的阻气层190,使阻气层190不相连,即不覆盖装置130的所有表面。如图18e所示,接着形成软性结构200于不同像素或次像素的第二挡墙160之间,以增加封装结构的可挠性。可以理解的是,软性结构200的高度可大于、等于或小于开口的深度,只要能提高封装结构的可挠性即可。虽然图18a至图18e的实施例中,一阻气层195/缓冲层175/阻气层190只覆盖单一的电子元件140,但也可覆盖多个(而非所有)电子元件140如前述。另一方面,可在形成缓冲层 175之后即形成软性结构200,而不需在形成阻气层190之后才形成软性结构200。

49.在另一实施例中,可类似如图8b的做法,仅形成第一挡墙150,并表面处理第一挡墙150的内侧表面,使内侧表面与外侧表面的表面能不同。接着利用例如喷墨印刷形成缓冲

层175以覆盖电子元件140,可由此省略第二挡墙160的制作。

50.本发明各实施例的阻气层190、190’、195、195’或其组合而成的多层结构可概括为本发明的第一阻气层。在其他实施例中,图1至图18可选择性在制作电子元件140之前于元件区110先形成第二阻气层,第二阻气层的材料可与阻气层190、190’、195、195’相似,且位于元件区110的可挠基板100 与电子元件140之间,由此可强化保护电子元件140的特性并兼具可挠性。

51.本发明一实施例提供的封装结构,其内侧挡墙表面的表面能不同(例如: 大于)外侧挡墙表面的表面能,可让阻气层覆盖电子元件与内侧挡墙的表面,以避免水气及/或氧气侵入而劣化电子元件。另一方面,内侧挡墙表面的表面能不同(例如:大于)外侧挡墙表面的表面能,也可减少阻气层的溶液在涂布时溢出外侧挡墙的可能。另一方面,本发明一实施例的阻气层可位于软性结构与电子元件之间,可有效改善封装结构的可挠性。

52.虽然结合以上数个实施例公开了本发明,然而其并非用以限定本发明,任何所属技术领域中具有通常知识者,在不脱离本发明的精神和范围内,可作任意的更动与润饰,因此本发明的保护范围应当以附上的权利要求及其均等范围所界定的为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1