一种芯片和电子设备的制作方法

1.本发明涉及集成电路领域,特别是涉及一种芯片和电子设备。

背景技术:

2.随着集成电路的发展,芯片的功能越来越复杂,导致芯片中信号输入输出单元的数量越来越多。在芯片的面积越来越小的情况下,需要充分考虑信号输入输出单元的布局,使芯片能容纳更多的信号输入输出单元。在信号输入输出单元的布局中,除布局一定数量的信号输入输出单元外,同时需要布局一定数量的供电输入输出单元,为信号输入输出单元提供足够的电源,防止信号输入输出单元在动作过程中产生较大的电压降和噪声,导致芯片内部逻辑错误。同时,需要将供电输入输出单元的电源轨道与信号输入输出单元的电源轨道连接,以及将供电输入输出单元的地轨道与信号输入输出单元的地轨道连接,以避免发生静电放电时,产生较大的瞬间电流,烧毁芯片。

3.现有技术中,信号输入输出单元与供电输入输出单元交替设置在同一个区域,这种结构使得需要保证信号输入输出单元与供电输入输出单元的高度相同,才能使信号输入输出单元的电源轨道和供电输入输出单元的电源轨道连接,以及使信号输入输出单元的地轨道和供电输入输出单元的地轨道连接到一起。由于需要保证供电输入输出单元和信号输入输出单元的高度相同,导致无法灵活选择信号输入输出单元和供电输入输出单元,无法灵活布局信号输入输出单元和供电输入输出单元。

技术实现要素:

4.鉴于上述问题,本发明实施例提供一种芯片和电子设备,以解决芯片布局中,信号输入输出单元和供电输入输出单元相互影响,无法灵活布局的问题。

5.本发明实施例公开了一种芯片,包括:芯片本体,所述芯片本体包括至少一个第一输入输出区和至少一个第一输入输出电源区;

6.所述第一输入输出区为以所述芯片本体的中心点为中心、且由多个信号输入输出单元围绕所述中心依次排列组成的封闭区,所述第一输入输出电源区为以所述中心点为中心、且由多个供电输入输出单元围绕所述中心依次排列组成的封闭区;

7.所述第一输入输出区和所述第一输入输出电源区嵌套设置,所述供电输入输出单元用于为所述信号输入输出单元提供电源。

8.可选的,所述第一输入输出区与至少一个所述第一输入输出电源区相邻。

9.可选的,所述第一输入输出电源区的个数为多个,至少一个所述第一输入输出区靠近所述中心点的一侧与多个所述第一输入输出电源区中的一个第一输入输出电源区相邻,且至少一个所述第一输入输出区远离所述中心点的一侧与多个所述第一输入输出电源区中的另一个第一输入输出电源区相邻。

10.可选的,所述芯片本体还包括至少一个目标区,所述目标区为所述芯片本体中除所述第一输入输出电源区和所述第一输入输出区之外的区域,所述目标区由至少一个所述

信号输入输出单元和至少一个所述供电输入输出单元组成。

11.可选的,所述目标区包括至少一个第二输入输出区和至少一个第二输入输出电源区,所述第二输入输出区包括至少一个所述信号输入输出单元,所述第二输入输出电源区包括至少一个所述供电输入输出单元。

12.可选的,所述第二输入输出区与至少一个所述第二输入输出电源区相邻。

13.可选的,所述第二输入输出电源区的个数为多个,至少一个所述第二输入输出区的第一侧与多个所述第二输入输出电源区中的一个第二输入输出电源区相邻,且至少一个所述第二输入输出区的第二侧与多个所述第二输入输出电源区中的另一个第二输入输出电源区相邻,第一侧和第二侧为所述至少一个所述第二输入输出区相对的两侧。

14.可选的,还包括连接单元,所述连接单元位于最靠近所述中心点的第一输入输出电源区或第一输入输出区内,所述目标区通过所述连接单元接入最靠近所述中心点的第一输入输出电源区或第一输入输出区。

15.可选的,所述第二输入输出电源区和/或所述第二输入输出区通过所述连接单元接入所述第一输入输出电源区;或者,

16.所述第二输入输出电源区和/或所述第二输入输出区通过所述连接单元接入所述第一输入输出区。

17.本发明还提供一种电子设备,包括如上所述的芯片。

18.本发明实施例包括以下优点:

19.芯片包括芯片本体,芯片本体包括至少一个第一输入输出区和至少一个第一输入输出电源区,第一输入输出区为以芯片本体的中心点为中心、且由多个信号输入输出单元围绕中心依次排列组成的封闭区,第一输入输出电源区为以中心点为中心、且由多个供电输入输出单元围绕中心依次排列组成的封闭区,第一输入输出区和第一输入输出电源区嵌套设置,供电输入输出单元用于为信号输入输出单元提供电源。本发明实施例中,通过设置不同的区域分别布局供电输入输出单元和信号输入输出单元,信号输入输出单元组成的第一输入输出区对应的地轨道和电源轨道形成封闭结构,且供电输入输出单元组成的第一输入输出电源区对应的地轨道和电源轨道形成封闭结构,单独的封闭结构本身保持高度一致即可,而不同的封闭结构之间,可以对应不同的高度;信号输入输出单元的电源轨道可以与相邻区域中的供电输入输出单元的电源轨道连接,以及信号输入输出单元的地轨道可以与相邻区域中的供电输入输出单元的地轨道连接,因此信号输入输出单元与供电输入输出单元可以分别选择不同的尺寸规格,进而灵活的布局芯片外围的供电输入输出单元和信号输入输出单元。

附图说明

20.图1示出了本发明的一种芯片的结构示意图;

21.图2示出了图1中a位置的电路连接示意图;

22.图3示出了本发明的另一种芯片的结构示意图;

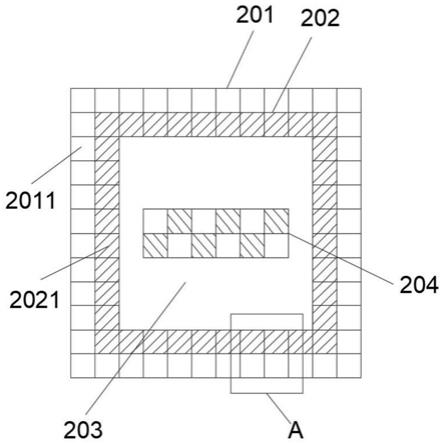

23.图4示出了本发明的又一种芯片的结构示意图;

24.图5示出了图4中b位置的电路连接示意图;

25.图6示出了图4中c位置的电路连接示意图。

具体实施方式

26.为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合附图和具体实施方式对本发明作进一步详细的说明。

27.参照图1,示出了本发明的一种芯片的结构示意图。如图1所示,芯片包括芯片本体,芯片本体包括至少一个第一输入输出区201和至少一个第一输入输出电源区202,第一输入输出区201为由多个小方格组成的矩形区域,第一输入输出电源区202即图1所示的斜线覆盖的矩形区域。

28.第一输入输出区201为以芯片本体203的中心点为中心、且由多个信号输入输出单元2011(signal io)围绕该中心依次排列组成的封闭区。第一输入输出电源区202为以芯片本体203的中心点为中心、且由多个供电输入输出单元2021(supply io)围绕该中心依次排列组成的封闭区。第一输入输出电源区202和第一输入输出区201嵌套设置,供电输入输出单元2021用于为信号输入输出单元2011提供电源。其中,一个斜线覆盖的小方格区域表示一个供电输入输出单元2021,一个白色小方格区域表示一个信号输入输出单元2011。

29.可选的,上述芯片本体203的中心点可以为标准中心点,也可以为指定中心点,还可以为估算中心点。当芯片本体203为规则形状时,如芯片本体203为正方形,芯片本体203的中心点为标准中心点,即是指该正方形两条对角线的交点,即标准中心点通常指芯片本体203的几何中心点;当芯片本体203为不规则形状时,芯片本体203的中心点可以为估算的大致中心点;此外,无论芯片本体203是否是规则形状,都可以人为设定一个中心点,该设定的中心点可以为芯片本体203上的任意指定位置,即该设定的中心点为指定中心点。

30.本实施例中,芯片本体203例如可以为处理器(cpu,central processing unit)等用于处理指令、执行操作、控制时间和处理数据的最终执行单元。芯片本体203中除第一输入输出区201和第一输入输出电源区202之外的区域用于布局逻辑部件,芯片本体203的内部结构可参考现有技术,本实施例对此不做赘述。信号输入输出单元2011为设置在芯片本体的四周,用于连接芯片本体与芯片本体外部的其他器件,以实现芯片本体与外部环境的信息交互。供电输入输出单元2021与信号输入输出单元2011连接,用于为信号输入输出单元2011提供电源,信号输入输出单元2011和供电输入输出单元2021的具体结构和功能可参考现有技术,本实施对此不做赘述。

31.本实施例中,第一输入输出电源区202用于布局多个供电输入输出单元2021,第一输入输出区201用于布局多个信号输入输出单元2011。第一输入输出区201和第一输入输出电源区202均为以芯片本体203的中心点为中心,环绕芯片本体203形成的环形封闭区。

32.示例的,如图1所示,芯片本体203包括一个第一输入输出区201和一个第一输入输出电源区202。芯片本体203为矩形,第一输入输出电源区202中,多个供电输入输出单元2021围绕芯片本体203依次排列,形成闭合的矩形供电输入输出环。其中,第一输入输出电源区202中,供电输入输出单元2021的数量可以根据供电输入输出单元2021的尺寸规格,以及第一输入输出电源区202的尺寸规格设置,本实施例对此不做限制。第一输入输出区201嵌套在第一输入输出电源区202远离芯片本体203的一侧,第一输入输出区201中,多个信号输入输出单元2011围绕第一输入输出电源区202依次排列,形成闭合的矩形输入输出环。其中,每个第一输入输出区201中,信号输入输出单元2011的数量可以根据信号输入输出单元2011的尺寸规格,以及第一输入输出区201的尺寸规格设置,本实施例对此不做限制。

33.需要说明的是,芯片本体的形状可以根据需求设置,例如芯片本体可以为圆形或椭圆形,或者三角形和五边形等多边形。相应的,以芯片本体的中心点为中心,围绕芯片本体形成的第一输入输出电源区和第一输入输出区的形状根据芯片本体的形状确定,例如若芯片本体为五边形,则形成的第一输入输出电源区和第一输入输出区为五边形的环状封闭区。

34.实际应用中,第一输入输出区201和第一输入输出电源区202的数量可以根据需求设置,例如可以包括2个第一输入输出区201和一个第一输入输出电源区202,或者2个第一输入输出区201和3个第一输入输出电源区202,本实施例对第一输入输出区201和第一输入输出电源区202的数量不做限制。同时,图1中的第一输入输出区201嵌套在第一输入输出电源区202的外侧(远离芯片本体中心点的一侧),第一输入输出电源区202嵌套在第一输入输出区201的内侧(靠近芯片本体中心点的一侧),而实际应用中,第一输入输出区201和第一输入输出电源区202的位置可以相互交换,如第一输入输出电源区202可以位于第一输入输出区201的外侧,本实施例对第一输入输出区201和第一输入输出电源区202的相对位置关系不做限制。

35.本实施例中,供电输入输出单元2021用于为信号输入输出单元2011供电。如图2所示,示出了图1中a位置的电路连接示意图,供电输入输出单元2021与相邻的信号输入输出单元2011邻接,用于为相邻的信号输入输出单元2011供电。即供电输入输出单元2021中的前驱动地轨道(vss)与相邻的信号输入输出单元2011中的前驱动地轨道(vss)短接,供电输入输出单元2021中的前驱动电源轨道(vdd)与相邻的信号输入输出单元2011中的前驱动电源轨道(vdd)短接,供电输入输出单元2021中的后驱动地轨道(vsspst)与相邻的信号输入输出单元2011中的后驱动地轨道(vsspst)短接,供电输入输出单元2021中的后驱动电源轨道(vddpst)与相邻的信号输入输出单元2011中的后驱动电源轨道(vddpst)短接,以实现对信号输入输出单元的供电。并且,为了保证芯片本体的静电放电(esd,electro-static discharge)保护特性,如图2所示,每个第一输入输出电源区202中,相邻供电输入输出单元2021之间邻接,即相邻供电输入输出单元2021的前驱动电源轨道(vdd)短接,前驱动地轨道(vss)短接,后驱动地轨道(vsspst)短接,后驱动电源轨道(vddpst)短接,以将每个第一输入输出电源区202中的多个供电输入输出单元2011构成完整的供电输入输出环,提高芯片的esd保护特性。同时,可以在每个第一输入输出区201中,使相邻的信号输入输出单元2011之间邻接,即相邻信号输入输出单元2011的前驱动电源轨道(vdd)短接,前驱动地轨道(vss)短接,后驱动地轨道(vsspst)短接,后驱动电源轨道(vddpst)短接。

36.实际使用时,由于相邻的供电输入输出单元与信号输入输出单元之间邻接,因此可以只在每个第一输入输出电源区202中,使相邻的供电输入输出单元2021之间邻接,或者在每个第一输入输出区201中,使相邻的信号输入输出单元之间邻接。供电输入输出单元与信号输入输出单元之间的邻接方式,信号输入输出单元之间的邻接方式,以及供电输入输出单元之间的邻接方式可参考现有技术,本实施例对此不做限制。

37.本实施例中,由于第一输入输出区中只包括信号输入输出单元,因此,只需保证第一输入输出区中的信号输入输出单元的高度相同即可。同理,第一输入输出电源区中只包括供电输入输出单元,只需保证第一输入输出电源区中的供电输入输出单元的高度相同即可,信号输入输出单元和供电输入输出单元的高度可以相同或不同。在芯片布局过程中,由

于供电输入输出单元与信号输入输出单元分别位于不同的区域,供电输入输出单元与信号输入输出单元的尺寸规格可以不同,供电输入输出单元的尺寸规格不受信号输入输出单元的尺寸规格的限制,可以灵活选择供电输入输出单元的尺寸规格,以灵活的调整第一输入输出电源区中供电输入输出单元的数量。同理,信号输入输出单元的尺寸规格不受供电输入输出单元的尺寸规格的限制,可以灵活选择第一信号输入输出单元的尺寸规格,以灵活调整第一输入输出区中信号输入输出单元的数量。

38.综上所述,芯片包括芯片本体,芯片本体包括至少一个第一输入输出区和至少一个第一输入输出电源区,第一输入输出区为以芯片本体的中心点为中心、且由多个信号输入输出单元围绕中心依次排列组成的封闭区,第一输入输出电源区为以芯片本体的中心点为中心、且由多个供电输入输出单元围绕中心依次排列组成的封闭区,第一输入输出区和第一输入输出电源区嵌套设置,供电输入输出单元用于为信号输入输出单元提供电源。通过设置不同的区域分别布局供电输入输出单元和信号输入输出单元,信号输入输出单元的电源轨道可以与相邻区域中的供电输入输出单元的电源轨道连接,以及信号输入输出单元的地轨道可以与相邻区域中的供电输入输出单元的地轨道连接,因此信号输入输出单元与供电输入输出单元可以分别选择不同的尺寸规格,进而灵活的布局芯片外围的供电输入输出单元和信号输入输出单元。

39.参照图3,示出了本发明的另一种芯片的结构示意图,如图3所示,芯片包括芯片本体,芯片本体包括至少一个第一输入输出区201和至少一个第一输入输出电源区202。

40.示例的,如图3所示,芯片本体可以包括两个第一输入输出电源区202和两个第一输入输出区201。

41.可选的,第一输入输出区201与至少一个第一输入输出电源区202相邻。

42.本实施例中,可以使每个第一输入输出区201与至少一个第一输入输出电源区202相邻,即第一输入输出区201的内侧或外侧至少设置一个与第一输入输出区201相邻的第一输入输出电源区202。如图3所示,可以使第一输入输出区201和第一输入输出电源区202交替设置,以使每个第一输入输出区201都与其中的至少一个第一输入输出电源区202相邻。实际使用时,可以根据需求调整第一输入输出区和第一输入输出电源区的布局方式,使每个第一输入输出区与至少一个输入输出电源区相邻。

43.实际应用中,第一输入输出电源区202中的供电输入输出单元2021用于为第一输入输出区201中的信号输入输出单元2011供电,当供电输入输出单元2021与信号输入输出单元2011之间距离较远时,会导致供电输入输出单元2021与信号输入输出单元2011之间的电压降增加,导致信号输入输出单元2011的供电不足,影响信号输入输出单元2011的性能。因此,设置每个第一输入输出区201与至少一个第一输入输出电源区202相邻,可以避免由于距离原因,导致信号输入输出单元2011的供电不足的问题。

44.可选的,第一输入输出电源区的个数为多个,至少一个第一输入输出区靠近芯片本体中心点的一侧与多个第一输入输出电源区中的一个第一输入输出电源区相邻,且该至少一个第一输入输出区远离芯片本体中心点的一侧与多个第一输入输出电源区中的另一个第一输入输出电源区相邻。

45.示例的,参照图4,示出了本发明的又一种芯片的结构示意图,芯片本体中可以包括一个第一输入输出区201和两个第一输入输出电源区202。其中,第一输入输出区201位于

两个第一输入输出电源区202之间,即第一输入输出区201靠近芯片本体的一侧(第一输入输出区的内侧)设置有相邻的一个第一输入输出电源区202,第一输入输出区201远离芯片本体的一侧(第一输入输出区的外侧)同样设置有相邻的另一个第一输入输出电源区202。实际使用中,可以根据需求调整第一输入输出区和第一输入输出电源区的布局方式,使第一输入输出区的内侧和外侧均布局有相邻的一个第一输入输出电源区。

46.本实施例中,当第一输入输出区的内侧和外侧均布局有第一输入输出电源区时,可以通过内侧和外侧的第一输入输出电源区中的供电输入输出单元同时为第一输入输出区中的信号输入输出单元供电。如图5所示,示出了图4中b位置的电路连接示意图,第一输入输出区中的信号输入输出单元可以通过两侧的供电输入输出单元同时提供电源,保证第一输入输出区中的信号输入输出单元可以得到充足的电源,提高信号输入输出单元的性能。

47.需要说明的是,实际应用中,当第一输入输出区的数量较少时,可以在每个第一输入输出区的至少一侧设置有一个相邻的第一输入输出电源区,以保证每个信号输入输出单元的电源需求。而当第一输入输出电源区的数量较多时,可以在部分或全部第一输入输出区的两侧分别设置一个相邻的第一输入输出电源区,以给每个信号输入输出单元提供充足的电源,提高信号输入输出单元的性能。

48.可选的,芯片本体还可以包括至少一个目标区,目标区为芯片本体中除第一输入输出电源区和第一输入输出区之外的区域,目标区由至少一个信号输入输出单元和至少一个供电输入输出单元组成。

49.示例的,如图1所示,芯片本体203中可以设置有目标区204,目标区204用于布局至少一个信号输入输出单元2011,以及至少一个为目标区204中的信号输入输出单元2011提供电源的供电输入输出单元2021。

50.实际应用中,目标区204的数量可以是一个或多个,目标区204可以设置在芯片本体中除第一输入输出区201和第一输入输出电源区202之外的任意位置,如图1所示的中间位置。目标区204中信号输入输出单元和供电输入输出单元的数量,以及目标区在芯片本体中的具体位置可以根据需求设置,本实施例对此不做限制。

51.本实施例中,如图1所示,当目标区204中的信号输入输出单元2011和供电输入输出单元2021的数量分别为多个的时候,目标区204可以由信号输入输出单元2011和供电输入输出单元2021交替排列组成。目标区204由信号输入输出单元2011和供电输入输出单元2021交替排列组成时,供电输入输出单元与信号输入输出单元之间的连接方法可参考现有技术,本实施例对此不做赘述。

52.当芯片本体203中存在空白区域时(未布局其他部件的区域)时,可以在空白区域设置目标区204,在目标区204中布局一定数量的信号输入输出单元和供电输入输出单元,可以在不增加芯片面积的情况下,增加一定数量的信号输入输出单元,为芯片提供更加丰富的芯片接口。

53.可选的,目标区可以包括至少一个第二输入输出区和至少一个第二输入输出电源区,第二输入输出区包括至少一个信号输入输出单元,第二输入输出电源区包括至少一个供电输入输出单元。

54.示例的,如图3所示,在目标区204中,可以设置有一个第二输入输出区2041和一个

第二输入输出电源区2042,第二输入输出区2041和第二输入输出电源区2042并排设置。其中,第二输入输出区2041可以由多个信号输入输出单元2011依次排列组成,第二输入输出电源区2042可以由多个供电输入输出单元2021依次排列组成。第二输入输出电源区中的供电输入输出单元与第二输入输出区中的信号输入输出单元之间的连接方式可参考图2,本实施例对此不做赘述。

55.本实施例中,目标区204由至少一个第二输入输出区2041和至少一个第二输入输出电源区2042组成时,在目标区204的布局过程中,可以分别选择不同尺寸规格的信号输入输出单元和供电输入输出单元,实现目标区的灵活布局。

56.可选的,第二输入输出区与至少一个第二输入输出电源区相邻。

57.本实施例中,在目标区204的布局中,可以设置每个第二输入输出区2041与至少一个第二电源输入输出区2042相邻。如图3和图4所示,可以在第二输入输出区2041的一侧和/或两侧布局相邻的第二输入输出区2042,以为第二输入输出区2041中的信号输入输出单元提供足够的电源。为第二输入输出区布局相邻的第二输入输出电源区的原理和方法,可参考为第一输入输出区布局相邻的第一输入输出电源区,本实施例对此不做赘述。

58.可选的,第二输入输出电源区的个数为多个,至少一个第二输入输出区的第一侧与多个第二输入输出电源区中的一个第二输入输出电源区相邻,且至少一个第二输入输出区的第二侧与多个第二输入输出电源区中的另一个第二输入输出电源区相邻。

59.示例的,如图4所示,在目标区204的布局中,当第二输入输出电源区2042的数量较多时,可以在每个第二输入输出区2041的两侧分别布局相邻的第二输入输出电源区2042,以为第二输入输出区2041中的信号输入输出单元提供充足的电源。为每个第二输入输出区的两侧分别布局相邻的第二输入输出电源区的原理和方法,可参考为每个第一输入输出区的两侧分别布局相邻的第一输入输出电源区,本实施例对此不做赘述。

60.可选的,还可以包括连接单元,连接单元位于靠近芯片本体中心点的第一输入输出电源区或第一输入输出区内,目标区通过连接单元接入靠近芯片本体中心点的第一输入输出电源区或第一输入输出区。

61.可选的,当第一输入输出区(输入输出区a)是最靠近芯片本体中心点的区域时,连接单元位于该输入输出区a内,即目标区通过该连接单元接入输入输出区a;同理,当第一输入输出电源区(输入输出电源区a)是最靠近芯片本体中心点的区域时,连接单元位于该输入输出电源区a内,即目标区通过该连接单元接入输入输出电源区a中。此外,当第一输入输出区(输入输出区a)是最靠近芯片本体中心点的区域时,连接单元还可以位于与该输入输出区a最近的相邻第一输入输出电源区内;同理,当第一输入输出电源区(输入输出电源区a)是最靠近芯片本体中心点的区域时,连接单元还可以位于与该输入输出电源区a最近的相邻第一输入输出区内,在此不再赘述。

62.本实施例中,当目标区中包括第二输入输出区和第二输入输出电源区时,第二输入输出电源区和/或第二输入输出区通过连接单元接入第一输入输出电源区;或者,第二输入输出电源区和/或第二输入输出区通过连接单元接入第一输入输出区。

63.示例的,如图4所示,连接单元205可以为三通输入输出单元(triple io),三通输入输出单元可以设置在第一输入输出电源区202中。参照6,示出了图4中c位置的电路连接示意图,结合图4和图5,三通输入输出单元可以选择与第一输入输出电源区202中的供电输

入输出单元2021相同的尺寸规格,以将三通输入输出单元布局在第一输入输出电源区202中,三通输入输出单元的两个连接端位于第一输入输出电源区202内,另一个连接端与目标区204中的供电输入输出单元连接。三通输入输出单元位于第一输入输出电源区202的两个连接端分别与第一输入输出电源区202中相邻的供电输入输出单元邻接。同时,三通输入输出单元的另一端与第二输入输出电源区2042一端的供电输入输出单元邻接。通过三通输入输出单元,可以简单方便的将第二输入输出电源区中的供电输入输出单元接入第一输入输出电源区。同理,可以将第二输入输出区中的信号输入输出单元接入第一输入输出电源区。

64.实际应用中,当目标区由多个信号输入输出单元和多个供电输入输出单元交替排列组成时,将目标区接入第一输入输出区或第一输入输出电源区的方法与将第二输入输出电源区接入第一输入输出电源区的方法相同,本实施例对此不做赘述。

65.第一输入输出区和第一输入输出电源区的位置可以互换,第二输入输出电源区和/或第二输入输出区也可以接入第一输入输出区。将第二输入输出电源区和第二输入输出区接入第一输入输出区的原理与接入第一输入输出电源区相同,本实施例对此不做赘述。

66.本实施例中,将第二输入输出电源区和/或第二输入输出区接入第一输入输出区或第一输入输出电源区,可以将更多的信号输入输出单元和供电输入输出单元接入供电网络,可以进一步提高芯片的esd保护特性。同时,可以通过第一输入输出电源区中的供电输入输出单元给目标区的信号输入输出单元供电,或者通过目标区的供电输入输出单元给第一输入输出区的信号输入输出单元供电,提高芯片的供电性能。

67.可选的,当目标区204与芯片本体203的一侧平行时,目标区204中的第二输入输出电源区2042和/或第二输入输出区2041的两端可以分别接入第一输入输出电源区(如图4所示),或者接入第一输入输出区。第二输入输出电源区和/或第二输入输出区的两端分别接入第一输入输出电源区或接入第一输入输出区,可以进一步提高芯片的esd保护特性。

68.可选的,连接单元中可以设置有esd保护电路。连接单元中设置esd保护电路,可以进一步提高芯片的esd保护特性。esd保护电路的具体结构可参考现有技术,本实施例对此不做限制。

69.综上所述,芯片包括芯片本体,芯片本体包括至少一个第一输入输出区和至少一个第一输入输出电源区,第一输入输出区为以芯片本体的中心点为中心、且由多个信号输入输出单元围绕中心依次排列组成的封闭区,第一输入输出电源区为以芯片本体的中心点为中心、且由多个供电输入输出单元围绕中心依次排列组成的封闭区,第一输入输出电源区和第一输入输出区嵌套设置,供电输入输出单元用于为信号输入输出单元提供电源。通过设置不同的区域分别布局供电输入输出单元和信号输入输出单元,信号输入输出单元组成的第一输入输出区对应的地轨道和电源轨道形成封闭结构,且供电输入输出单元组成的第一输入输出电源区对应的地轨道和电源轨道形成封闭结构,单独的封闭结构本身保持高度一致即可,而不同的封闭结构之间,可以对应不同的高度;信号输入输出单元的电源轨道可以与相邻区域中的供电输入输出单元的电源轨道连接,以及信号输入输出单元的地轨道可以与相邻区域中的供电输入输出单元的地轨道连接,因此信号输入输出单元与供电输入输出单元可以分别选择不同的尺寸规格,进而灵活的布局芯片外围的供电输入输出单元和信号输入输出单元。

70.本实施例中,还提供一种电子设备,包括如前述任一实施例所述的芯片。

71.以上对本发明所提供的一种芯片和电子设备,进行了详细介绍,本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本发明的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1