电路架构及其制作方法与流程

1.本揭露涉及一种电路架构及其制作方法,尤其涉及一种提高可靠性的电路架构及其制作方法。

背景技术:

2.随电子产品蓬勃发展,电子产品的制作方法(例如测试技术、处理技术等)也不断地改良。因此,要如何提高电子装置的产量或降低成本已成为需要不断改进的项目。

技术实现要素:

3.本揭露是提供一种电路架构的制作方法,其可监控电路架构的电路质量或提高可靠度。

4.本揭露是提供一种电路架构,其可提高可靠性。

5.根据本揭露的实施例,电路架构的制作方法包括以下步骤。首先,提供基板。接着,制作测试电路组件于基板上。再者,制作焊垫于测试电路组件上。而后,制作绝缘层。绝缘层的第二表面覆盖测试电路组件与焊垫。然后,制作导电垫于绝缘层上。导电垫与焊垫耦接。

6.根据本揭露的实施例,电路架构包括绝缘层、导电垫以及焊垫。绝缘层具有第一表面以及与第一表面相对的第二表面。导电垫设置在绝缘层的第一表面。焊垫设置在绝缘层的第二表面。焊垫与导电垫耦接。绝缘层在第二表面具有凹陷区。

附图说明

7.包含附图以便进一步理解本揭露,且附图并入本说明书中并构成本说明书的一部分。附图说明本揭露的实施例,并与描述一起用于解释本揭露的原理。

8.图1为本揭露一实施例的电路架构的制作方法的流程图;

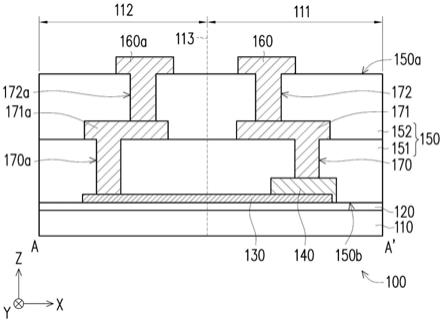

9.图2a至图2e为本揭露一实施例的电路架构的制作方法的剖面示意图;

10.图3为图2b的电路架构的下视示意图;

11.图4为图2d的电路架构的上视示意图;

12.图5为本揭露另一实施例的电路架构于移除基板前的剖面示意图;

13.附图标号说明

14.100、100a:电路架构;

15.110:基板;

16.111:主体区;

17.112:周边区;

18.113:切割线;

19.120:离型层;

20.130:测试电路组件;

21.131、131a:开口;

22.132、133:侧边;

23.134:接垫;

24.140:焊垫;

25.141:下表面;

26.150:绝缘层;

27.150a:第一表面;

28.150b:第二表面;

29.150c:侧面;

30.150e:开口;

31.151:第一层绝缘层;

32.151e:第一开口;

33.152:第二层绝缘层;

34.152e:第二开口;

35.160:导电垫;

36.160a:测试垫;

37.170、170a:第一通孔;

38.171、171a:接垫;

39.172、172a:第二通孔;

40.180:凹陷区;

41.s1、s2、s3、s4、s5、s6、s7:步骤;

42.t1、t2:厚度;

43.x、y、z:方向。

具体实施方式

44.通过参考以下的详细描述并同时结合附图可以理解本揭露,须注意的是,为了使读者能容易了解及为了附图的简洁,本揭露中的多张附图只绘出电子装置的一部分,且附图中的特定组件并非依照实际比例绘图。此外,图中各组件的数量及尺寸仅作为示意,并非用来限制本揭露的范围。

45.除非另外定义,在此使用的全部用语(包含技术及科学用语)具有与本揭露所属技术领域的技术人员通常理解的相同涵义。能理解的是,这些用语例如在通常使用的字典中定义用语,应被解读成具有与相关技术及本揭露的背景或上下文一致的意思,而不应以一理想化或过度正式的方式解读,除非在本揭露实施例有特别定义。

46.在下文说明书与权利要求中,“含有”与“包括”等词为开放式词语,因此其应被解释为“含有但不限定为

…”

之意。

47.应了解到,当组件或膜层被称为在另一个组件或膜层“上”或“连接到”另一个组件或膜层时,它可以直接在此另一组件或膜层上或直接连接到此另一组件或层,或者两者之间存在有插入的组件或膜层(非直接情况)。相反地,当组件被称为“直接”在另一个组件或膜层“上”或“直接连接到”另一个组件或膜层时,两者之间不存在有插入的组件或膜层。

48.说明书与权利要求中所使用的序数例如“第一”、“第二”等之用词用以修饰组件,

其本身并不意含及代表该(或该些)组件有任何之前的序数,也不代表某一组件与另一组件的顺序、或是制造方法上的顺序,该些序数的使用仅用来使具有某命名的组件得以和另一具有相同命名的组件能作出清楚区分。权利要求与说明书中可不使用相同用词,据此,说明书中的第一构件在权利要求中可能为第二构件。

49.术语“大约”、“等于”、“相等”或“相同”、“实质上”或“大致上”一般解释为在所给定的值或范围的20%以内,或解释为在所给定的值或范围的10%、5%、3%、2%、1%或0.5%以内。

50.在本揭露中,厚度、长度与宽度的测量方式可以是采用光学显微镜测量而得,厚度则可以由电子显微镜中的剖面影像测量而得,但不以此为限。另外,任两个用来比较的数值或方向,可存在着一定的误差。若第一值等于第二值,其隐含着第一值与第二值之间可存在着约10%的误差;若第一方向垂直于第二方向,则第一方向与第二方向之间的角度可介于80度至100度之间;若第一方向平行于第二方向,则第一方向与第二方向之间的角度可介于0度至10度之间。

51.在本揭露一些实施例中,关于接合、连接的用语例如“连接”、“互连”等,除非特别定义,否则可指两个结构系直接接触,或者亦可指两个结构并非直接接触,其中有其它结构设于此两个结构之间。且此关于接合、连接的用语亦可包括两个结构都可移动,或者两个结构都固定的情况。此外,用语“耦接”包含任何直接及间接的电性连接手段。

52.须知悉的是,以下所举实施例可以在不脱离本揭露的精神下,可将数个不同实施例中的特征进行替换、重组、混合以完成其他实施例。各实施例间特征只要不违背发明精神或相冲突,均可任意混合搭配使用。

53.本揭露的电子装置可包括显示设备、天线装置(例如液晶天线)、感测装置、发光装置、触控装置或拼接装置,但不以此为限。电子装置可包括可弯折、可挠式电子装置。电子装置的外型可为矩形、圆形、多边形、具有弯曲边缘的形状或其他适合的形状。电子装置可例如包括发光二极管、液晶(liquid crystal)、荧光(fluorescence)、磷光(phosphor)、量子点(quantum dot,qd)、其它合适的材料或前述的组合,但不以此为限。发光二极管可例如包括有机发光二极管(organic light emitting diode,oled)、无机发光二极管(inorganic light-emitting diode,led)、次毫米发光二极管(mini led)、微发光二极管(micro led)或量子点发光二极管(可例如为qled、qdled)、其他适合的材料或上述的任意排列组合,但不以此为限。需注意的是,电子装置可为前述的任意排列组合,但不以此为限。

54.本揭露的电路架构可包括重布线路层(redistribution layer,rdl),但不以此为限。

55.现将详细地参考本揭露的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同组件符号在附图和描述中用来表示相同或相似部分。

56.图1为本揭露一实施例的电路架构的制作方法的流程图。图2a至图2e为本揭露一实施例的电路架构的制作方法的剖面示意图。图3为图2b的电路架构的下视(仰视)示意图。图4为图2d的电路架构的上视(俯视)示意图。其中,图2b可为图3的电路架构沿剖面线a-a’的剖面示意图,图2d可为图4的电路架构沿剖面线b-b’的剖面示意图。此外,为了附图清楚及方便说明,图3及图4省略示出了电路架构中的若干组件。

57.首先,请同时参照图1以及图2a。在本实施例的电路架构100的制作方法中,先进行

步骤s1、步骤s2以及步骤s3。在步骤s1中,提供基板110。基板110包括主体区111、周边区112以及切割线113。其中,切割线113位于主体区111与周边区112之间的交界处。周边区112可在后续的切割步骤中被移除,而主体区111则在后续的切割步骤中被保留下来。在本实施例中,基板110可包括硬性基板或软性基板。举例来说,基板110为硬性基板时,材料可包括玻璃(glass)、石英(quartz)、蓝宝石(sapphire)、陶瓷(ceramic)、其它合适的基板材料、或前述的组合,但不以此为限。当基板110为软性基板时,材料可包括聚酰亚胺(polyimide,pi)、聚对苯二甲酸(polyethylene terephthalate,pet)、其它合适的基板材料、或前述的组合,但不以此为限。

58.接着,在本实施例中,可选择地在基板110上形成离型层(release layer)120,但不以此为限。也就是说,在其他实施例中,也可以选择地不设置离型层120。在本实施例中,离型层120可与基板110一起在后续的步骤中被分离。离型层120可例如是由聚合物系材料形成,但不以此为限。举例来说,在一些实施例中,离型层120可以是会在受热时失去其粘着特性的环氧树脂系热释放材料,例如光热转换(light-to-heat-conversion,lthc)释放涂层。在其他实施例中,离型层120也可以是会在被暴露至紫外光(ultra-violet,uv)时失去其粘着特性的紫外光胶。

59.在步骤s2中,制作测试电路组件130于基板110上,以使测试电路组件130与基板110分别位于离型层120的相对两侧。在本实施例中,测试电路组件130未完全覆盖离型层120,测试电路组件130具有多个开口131、131a,且开口131、131a暴露出部分的离型层120。详细来说,在本实施例中,例如是以下述步骤制作测试电路组件130,但不以此为限:先以例如是物理气相沉积(physical vapor deposition,pvd)等的方法在离型层120上形成晶种层(seed layer,未示出),以使晶种层设置在基板110的主体区111与周边区112;接着,以例如是蚀刻的方法,移除部分晶种层,剩余的晶种层形成测试电路组件130,并使测试电路组件130设置在基板110的主体区111与周边区112,且使测试电路组件130可从基板110的主体区111延伸至周边区112。在本实施例中,晶种层可为导电材料,且所述导电材料可为单层或包括由不同导电材料形成的多层的复合层。晶种层的材料例如包括钛、铜、铝、钼、银、其它合适材料或上述组合,但不限于此。在一些实施例中,晶种层可包括钛层及位于所述钛层之上的铜层。在本实施例中,测试电路组件130可为导电材料,例如金属或金属合金。测试电路组件130的材料例如包括钛、铜、铝、钼、银、其它合适材料或上述组合,但不限于此。

60.在步骤s3中,制作焊垫140于测试电路组件130上,并使焊垫140与测试电路组件130耦接。请同时参照图2a,焊垫140可超出测试电路组件130并与离型层120接触;在其他实施例中,焊垫140可与测试电路组件130接触而未与离型层120接触;在其他实施例中,焊垫140可小于测试电路组件130,但本揭露不限于此。详细来说,在本实施例中,例如是以下述步骤制作焊垫140,但不以此为限:首先在测试电路组件130以及由测试电路组件130暴露出的离型层120上形成图案化的光致抗蚀剂(未示出)。其中,图案化的光致抗蚀剂具有多个开口(未示出),并且所述开口暴露出一部分的测试电路组件130和/或一部分的离型层120。接着,以镀覆工艺(例如电镀,但不以此为限)在图案化的光致抗蚀剂的开口中形成焊垫140。然后,去除图案化的光致抗蚀剂,并暴露出其他部分的测试电路组件130和/或其他部分的离型层120。至此,已制作完成焊垫140。在本实施例中,焊垫140可为金属或金属合金。焊垫140的材料例如包括钛、铜、铝、钼、银、其它合适材料或上述组合,但不限于此。在本实施例

中,焊垫140可与测试电路组件130选用相同材料,但亦可选用不同材料,本揭露并无限制。

61.更详细来说,在本实施例中,焊垫140设置在基板110的主体区111的测试电路组件130上。焊垫140设置在测试电路组件130远离基板110的表面上,以覆盖主体区111中的部分的测试电路组件130和/或所述部分的测试电路组件130的侧边132。焊垫140可耦接测试电路组件130。此外,在本实施例中,方向z举例来说可为测试电路组件130的厚度方向,方向x、方向y与方向z为不同方向,举例来说,方向x与方向y分别垂直于方向z,且方向x垂直于方向y。此外,于方向z上,测试电路组件130的厚度t1可以小于焊垫140的厚度t2,但不以此为限。请同时参照图3,在方向z上,焊垫140未完全与测试电路组件130重叠,但本揭露不限于此。在其他实施例中,焊垫140也可设置在基板110的周边区112(未示出)。测试电路组件130的厚度t1与焊垫140的厚度t2都是以方向z上的最大厚度。

62.然后,请同时参照图1、图2b以及图3,进行步骤s4以及步骤s5。在步骤s4中,制作绝缘层150,其中绝缘层150覆盖测试电路组件130与焊垫140。在步骤s5中,并制作导电垫160于绝缘层150上。在本实施例中,绝缘层150可包括第一层绝缘层151以及设置在第一层绝缘层151上的第二层绝缘层152,但本揭露并不对绝缘层150的层数加以限制。也就是说,在一些实施例中,绝缘层150的层数也可以是一层或是二层以上。在本实施例中,绝缘层150具有第一表面150a以及与第一表面150a相对的第二表面150b。绝缘层150的第一表面150a可为绝缘层150远离基板110的表面,且绝缘层150的第二表面150b可为绝缘层150邻近基板110的表面。此外,于方向z上,绝缘层150的最大厚度可以大于或等于30微米(μm)且小于或等于40微米,但不以此为限。

63.详细来说,在本实施例中,例如是以下述步骤制作绝缘层150以及导电垫160,但不以此为限:先于基板110的主体区111与周边区112形成第一层绝缘层151,以使第一层绝缘层151覆盖测试电路组件130、焊垫140以及未被测试电路组件130与焊垫140覆盖的离型层120。接着,在主体区111的第一层绝缘层151中形成第一通孔170,并在周边区112的第一层绝缘层151中形成第一通孔170a。第一通孔170可暴露出焊垫140,且第一通孔170a可暴露出周边区112的测试电路组件130。接着,在主体区111的第一层绝缘层151上形成接垫171并延伸入第一通孔170,并在周边区112的第一层绝缘层151上形成接垫171a并延伸入第一通孔170a。接垫171可耦接主体区111的焊垫140,且接垫171a可耦接周边区112的测试电路组件130。接着,于基板110的主体区111与周边区112形成第二层绝缘层152,以使第二层绝缘层152覆盖接垫171、接垫171a以及部分的第一层绝缘层151。接着,在主体区111的第二层绝缘层152中形成第二通孔172,并在周边区112的第二层绝缘层152中形成第二通孔172a。第二通孔172可暴露出主体区111的接垫171,且第二通孔172a可暴露出周边区112的接垫171a。然后,在主体区111的第二层绝缘层152上形成导电垫160并延伸入第二通孔172,并在周边区112的第二层绝缘层152上形成测试垫160a并延伸入第二通孔172a。导电垫160可耦接主体区111的接垫171,且测试垫160a可耦接周边区112的接垫171a。在本实施例中,绝缘层150的材料可包括有机材料、无机材料或上述之组合,但不以此为限。在本实施例中,导电垫160以及测试垫160a的材料可例如包括银、铜、铝、钼、钨、金、铬、镍、铂、钛、铱、铑、铟、铋、上述的合金、上述的组合或其它导电性较佳的金属材料,但不以此为限。在一些实施例中,导电垫160与测试垫160a的材料可以相同或不相同。至此,已制作完成绝缘层150以及导电垫160。

64.在本实施例中,以绝缘层150包含第一层绝缘层151及第二层绝缘层152为例,第一层绝缘层151邻近基板110的表面可视为是绝缘层150的第二表面150b,且绝缘层150的第二表面150b可覆盖测试电路组件130、焊垫140与离型层120。第二层绝缘层152远离基板110的表面可视为是绝缘层150的第一表面150a,且导电垫160位在绝缘层150的第一表面150a上。此外,由于导电垫160通过第二通孔172耦接接垫171、接垫171通过第一通孔170耦接焊垫140,因而使得导电垫160与焊垫140耦接。由于测试垫160a通过第二通孔172a耦接接垫171a、接垫171a通过第一通孔170a耦接测试电路组件130,因而使得测试垫160a与测试电路组件130耦接。此外,由于焊垫140耦接测试电路组件130,且测试电路组件130可从基板110的主体区111延伸至周边区112,因此,使得导电垫160可通过接垫171、焊垫140、测试电路组件130、以及接垫171a而与测试垫160a耦接。

65.接着,可进行一电路测试步骤来监控电路架构100的电路质量,以确认导电垫160与焊垫140之间没有开路(open circuit)的情况。具体来说,在本实施例中,由于导电垫160可通过接垫171、焊垫140、测试电路组件130以及接垫171a而与测试垫160a耦接,因此,可通过在导电垫160与测试垫160a上分别设置探针(未示出),以使探针以接触或不接触的方式来检测导电垫160与测试垫160a之间的耦接情形,进而可得知导电垫160与焊垫140之间的电路质量。

66.然后,请同时参照图1、图2b以及图2c,进行步骤s6:分离基板110。在本实施例中,例如是以激光的方式移除离型层120以及基板110,但不以此为限。因此,如图2c所示,在使用适当的方式移除离型层120以及基板110后,使得测试电路组件130以及绝缘层150都与基板110分离,并暴露出测试电路组件130、部分的焊垫140以及部分的第一层绝缘层151。

67.然后,请同时参照图1、图2c、图2d、图2e以及图4,进行步骤s7。在步骤s7中,在分离基板110之后,移除测试电路组件130。详细来说,请先参照图2c、图2d以及图4,在本实施例中,在基板110与绝缘层150分离之后以及移除测试电路组件130之前,先使用例如是轮刀或其他适合的方式沿着切割线113进行切割,以移除周边区112并暴露出绝缘层150的侧面150c以及测试电路组件130的侧边133。其中,绝缘层150的侧面150c可与测试电路组件130的侧边133实质上切齐。

68.接着,再参照图2d与图2e,在移除周边区112之后,利用例如是蚀刻工艺的方式移除测试电路组件130,以暴露出绝缘层150的第二表面150b以及焊垫140的下表面141。

69.详细来说,在本实施例中,由于测试电路组件130的厚度t1可以小于焊垫140的厚度t2,因此,当测试电路组件130与焊垫140使用相同材料时,在进行蚀刻工艺时,可以确保测试电路组件130可完全被移除并仍可保留焊垫140。在一些实施例中,参照图2e,当测试电路组件130与焊垫140使用不同材料时,可选择测试电路组件130蚀刻速率大于焊垫140的蚀刻速率(即测试电路组件130与焊垫140的蚀刻速率比大于1),因此,在进行蚀刻工艺时,可以确保测试电路组件130先完全被移除并仍可保留焊垫140。此外,再参照图2e,在移除测试电路组件130之后,可使绝缘层150的第二表面150b具有凹陷区180,且凹陷区180可从焊垫140延伸到绝缘层150的侧面150c。至此,已制作完成电路架构100。

70.简言之,本实施例的电路架构100可包括绝缘层150、导电垫160以及焊垫140。绝缘层150具有第一表面150a以及与第一表面150a相对的第二表面150b。导电垫160设置在绝缘层150的第一表面150a。焊垫140邻近设置在绝缘层150的第二表面150b。焊垫140与导电垫

160耦接。绝缘层150在第二表面150b具有凹陷区180。

71.此外,本实施例的电路架构100可在后续的应用中,作为电子装置的一部分。具体来说,可利用电路架构100的导电垫160与芯片(未示出)耦接的方式,将芯片设置于电路架构100的导电垫160上。接着,利用电路架构100的焊垫140与电子装置(未示出)耦接的方式,将电路架构100的焊垫140设置于电子装置上,焊垫140与电子装置间可加入电连接剂,例如焊锡、异方性导电胶(anisotropic conductive film,acf)或其他适合的材料,本揭露不限于此。藉此,使得在包含有电路架构100的电子装置中,其芯片与电子装置可以通过电路架构100电性连接。

72.基于上述,在本揭露实施例的电路架构100及其制作方法中,由于焊垫140可与测试电路组件130耦接,导电垫160可与焊垫140耦接,且导电垫160可通过焊垫140与测试电路组件130耦接,因此,可通过电路测试来检测导电垫160与测试电路组件130之间(或是导电垫160与测试垫160a之间)的耦接情形,进而得知导电垫160与焊垫140之间的电路质量。藉此,可提高本揭露实施例的电路架构100的可靠性。另外,在包含有本揭露实施例的电路架构100的电子装置中,由于其是在设置芯片(未示出)之前就已经制作完成导电垫160与焊垫140之间有电性连接的电路架构100,因此,相较于现有的电子装置是在设置芯片之后才能确定电路架构的电路可靠度,本揭露实施例的电路架构的制作方法还可降低因电路架构的制作不良而造成芯片浪费的问题。

73.以下将列举其他实施例以作为说明。在此必须说明的是,下述实施例沿用前述实施例的组件标号与部分内容,其中采用相同的标号来表示相同或近似的组件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,下述实施例不再重复赘述。

74.图5为本揭露另一实施例的电路架构100a于移除基板前的剖面示意图。请同时参照图2b与图5,本实施例的电路架构100a大致相似于图2b的电路架构100,因此两实施例中相同与相似的构件于此不再重述。本实施例的电路架构100a不同于电路架构100之处主要在于,本实施例的电路架构100a中的绝缘层150于周边区112具有开口150e。

75.详细来说,绝缘层150的开口150e可包括第一层绝缘层151的第一开口151e以及第二层绝缘层152的第二开口152e。第一层绝缘层151的第一开口151e设置在周边区112,以暴露出部分测试电路组件130并作为接垫134。第二层绝缘层152的第二开口152e设置在周边区112,以暴露出接垫134。第一层绝缘层151的第一开口151e与第二层绝缘层152的第二开口152e互相连通。第二层绝缘层152的第二开口152e于方向z的投影可大于第一层绝缘层151的第一开口151e于方向z的投影,但不以此为限。

76.此外,由于本实施例的电路架构100a没有测试垫,因此,在本实施例进行电路测试来监控导电垫160与焊垫140之间的电连耦接状况时,可通过在导电垫160与接垫134上分别设置探针(未示出),使探针以接触方式来检测导电垫160与接垫134之间的耦接情形,进而可得知导电垫160与焊垫140之间的电路质量,以确认导电垫160与焊垫140之间的耦接没有发生开路的情况。

77.综上所述,在本揭露实施例的电路架构及其制作方法中,由于焊垫可与测试电路组件耦接,导电垫可与焊垫耦接,且导电垫可通过焊垫与测试电路组件耦接,因此,可通过电路测试来检测导电垫与测试电路组件之间的耦接情形,进而得知导电垫与焊垫之间的电路质量。藉此,可提高本揭露实施例的电路架构的可靠性。另外,在包含有本揭露实施例的

电路架构的电子装置中,由于其是在设置芯片之前就已经制作完成导电垫与焊垫之间有电性连接的电路架构,因此,相较于现有的电子装置是在设置芯片之后才能确定电路架构的电路可靠度,本揭露实施例的电路架构的制作方法还可降低因电路架构的制作不良而造成芯片浪费的问题。

78.最后应说明的是:以上各实施例仅用以说明本揭露的技术方案,而非对其限制;尽管参照前述各实施例对本揭露进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本揭露各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1