封装结构及其制作方法与流程

1.本发明涉及一种封装结构及其制作方法,且特别是涉及一种晶片级(wafer level)的封装结构及其制作方法。

背景技术:

2.一般来说,开窗型球格阵列(window-type bga,wbga)封装结构的基板具有贯穿上、下表面的窗口,其中芯片通过粘晶层设置在基板上且覆盖窗口,芯片通过设置在窗口内的打线(如金线)而与基板电连接。由于芯片的尺寸较大,因此封装胶体无法经由基板的窗口流至下模具,且于下模具中也易产生胶体气泡/孔洞/未完全填满的现象。再者,封装程序时,因结构而导致模流不稳定,也容易使金线倒塌,进而导致短路的问题产生。此外,也因为芯片的尺寸较大,因此易导致整体封装结构产生翘曲(warpage)。

技术实现要素:

3.本发明提供一种封装结构,无基板、窗口及粘晶层的设计,可具有较薄的封装厚度及较佳的结构可靠度。

4.本发明还提供一种封装结构的制作方法,用以制作上述的封装结构。

5.本发明的封装结构,其包括一芯片、一重配置线路层、多个导电体、一封装胶体以及多个焊球。芯片具有相对的一主动面与一背面及连接主动面与背面的一周围表面且包括多个接垫。主动面区分为一中央区及位于中央区两侧旁的两周边区,而接垫位于中央区。重配置线路层配置于芯片的主动面上且包括多条线路及多个连接垫。连接垫位于芯片的周边区上。线路连接于接垫与部分连接垫。导电体分别配置于连接垫上。封装胶体覆盖重配置线路层并填充于导电体之间,且至少暴露出每一导电体的一下表面。焊球配置于封装胶体外,且与导电体电连接。

6.在本发明的一实施例中,上述的每一导电体包括一金属柱或一金属球。

7.在本发明的一实施例中,上述的金属柱的材质包括铜、银、锡或其他高导电性材料。

8.在本发明的一实施例中,上述的金属球的材料包括锡(sn)、无铅焊锡、锡铟(sn-in)、锡铅(sn-pb)、锡铋(sn-bi)或锡银铜(sn-ag-cu)。

9.在本发明的一实施例中,上述的封装胶体覆盖芯片的周围表面。封装胶体具有相对的一顶面以及一底面。封装胶体的顶面切齐于芯片的背面。封装胶体的底面切齐于每一导电体的下表面。

10.在本发明的一实施例中,上述的封装结构还包括一附加封装胶体以及一附加重配置线路层。附加封装胶体覆盖芯片的背面以及封装胶体。附加封装胶体的一附加底面切齐于封装胶体的底面。附加重配置线路层配置于封装胶体的底面以及附加封装胶体的附加底面上,且位于焊球与导电体之间。附加重配置线路层电连接导电体与焊球。

11.在本发明的一实施例中,上述的封装结构还包括一附加封装胶体,具有相对的一

附加顶面以及一附加底面。附加封装胶体覆盖芯片的周围表面。部分重配置线路层延伸出芯片的主动面,并且配置于附加封装胶体的附加底面上。

12.在本发明的一实施例中,上述的封装胶体覆盖附加封装胶体的附加顶面以及芯片的背面。

13.在本发明的一实施例中,上述的芯片包括一动态随机存取存储器。

14.在本发明的一实施例中,上述的封装胶体具有多个侧面,而芯片的周围表面至封装胶体的每一侧面之间的一水平间距相同。此水平间距为阻挡水气的最短距离。

15.本发明的封装结构的制作方法,其包括以下步骤。提供一晶片,且晶片包括多个芯片。每一芯片具有相对的一主动面与一背面及连接主动面与背面的一周围表面且包括多个接垫。主动面区分为一中央区及位于中央区两侧旁的两周边区,而接垫位于中央区。形成一重配置线路层于晶片上。重配置线路层位于每一芯片的主动面上且包括多条线路及多个连接垫。连接垫位于每一芯片的周边区上。线路连接于接垫与部分连接垫。形成多个导电体分别于连接垫上。对晶片进行一第一次单体化程序,以形成多个芯片单元。每一芯片单元包括每一芯片、位于每一芯片的主动面上的重配置线路层以及导电体。对芯片单元进行一封装程序,以使一封装胶体覆盖每一芯片的周围表面及重配置线路层,且至少暴露出每一导电体的一下表面。形成多个焊球于封装胶体外,其中焊球与导电体电连接。对封装胶体进行一第二次单体化程序,以形成具有焊球的多个封装结构。

16.在本发明的一实施例中,上述的形成导电体于连接垫上的方法包括电镀法或化学镀沉积法或金属贴合蚀刻法或回焊植球法。

17.在本发明的一实施例中,上述的每一导电体包括一金属柱或一金属球。

18.在本发明的一实施例中,上述的金属柱的材质包括一铜或其他高导电性材料。

19.在本发明的一实施例中,上述的金属球的材质包括一锡(sn)、无铅焊锡、锡铟(sn-in)、锡铅(sn-pb)、锡铋(sn-bi)或锡银铜(sn-ag-cu)。

20.在本发明的一实施例中,上述对芯片单元进行封装程序的步骤包括:提供具有一粘着层的一载板。将芯片单元通过粘着层而定位于载板上。粘着层位于每一芯片的背面与载板之间。形成一封装材料层于载板上。封装材料层覆盖芯片单元以及粘着层。对封装材料层进行一研磨程序,以暴露出每一导电体的下表面,而形成封装胶体。

21.在本发明的一实施例中,上述的于形成焊球于封装胶体外之后,且进行第二次单体化程序之前,移除粘着层与载板,而暴露出每一芯片的背面。

22.在本发明的一实施例中,上述的封装胶体填充于导电体之间。封装胶体具有相对的一顶面以及一底面。封装胶体的顶面切齐于芯片的背面。封装胶体的底面切齐于每一导电体的下表面。

23.在本发明的一实施例中,上述的芯片包括一动态随机存取存储器。

24.在本发明的一实施例中,上述的封装胶体具有多个侧面,而芯片的周围表面至封装胶体的每一侧面之间的一水平间距相同。

25.基于上述,在本发明的封装结构的设计中,导电体配置于重配置线路层的连接垫上,而芯片的接垫可通过重配置线路层及导电体与焊球电连接,且封装胶体覆盖重配置线路层并填充于导电体之间,且封装胶体至少暴露出导电体的下表面。由此,本发明的封装结构无需现有基板、窗口及粘晶层的设计,可通过封装胶体来取代基板,以保护及支撑芯片。

再者,因为本发明的封装结构无窗口的设计,因此单位面积封装可容许最大芯片,意即可有效利用空间最大化。此外,因为材料与界面的简化,因此本发明的封装结构除了可具有较佳的信号传递效果之外,也具有薄化设计,可具有较薄的封装厚度。

26.为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附的附图作详细说明如下。

附图说明

27.图1a至图1i是本发明的一实施例的一种封装结构的制作方法的示意图;

28.图1j为图1i的封装结构的俯视示意图;

29.图1k为图1i的封装结构的仰视示意图;

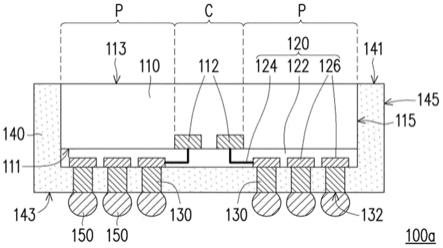

30.图2是本发明的一实施例的一种封装结构的剖面示意图;

31.图3是本发明的另一实施例的一种封装结构的剖面示意图;

32.图4是本发明的另一实施例的一种封装结构的剖面示意图;

33.图5是本发明的另一实施例的一种封装结构的剖面示意图。

34.符号说明

35.10:晶片

36.20:载板

37.30:粘着层

38.100a、100b、100c、100d、100e:封装结构

39.110:芯片

40.111:主动(有源)面

41.112:接垫

42.113:背面

43.115:周围表面

44.120:重配置线路层

45.122:绝缘层

46.124:线路

47.126:连接垫

48.130、135:导电体

49.132、137:下表面

50.140、140e:封装胶体

51.140a:封装材料层

52.141:顶面

53.143:底面

54.145:侧面

55.150、150c:焊球

56.160c、160d、160e:附加封装胶体

57.161d、161e:附加顶面

58.163c、163d、163e:附加底面

59.170:附加重配置线路层

60.c:中央区

61.h1、h2:水平间距

62.p:周边区

63.u:芯片单元

具体实施方式

64.图1a至图1i是依照本发明的一实施例的一种封装结构的制作方法的示意图。为了方便说明起见,图1a中绘示有局部放大的俯视图,而图1b中绘示有局部放大的立体图,且图1c至图1i中以剖面图来表示。

65.关于本实施例的封装结构的制作方法,首先,请参考图1a,提供一晶片10,其中晶片10包括多个芯片110。详细来说,每一芯片110具有相对的一主动面111与一背面113及连接主动面111与背面113的一周围表面115且包括多个接垫112。主动面111区分为一中央区c及位于中央区c两侧旁的两周边区p,而接垫112位于中央区c。此处,每一芯片110例如是一动态随机存取存储器(dynamic random access memory,dram),但不以此为限。

66.接着,请再参考图1a,形成一重配置线路层120于晶片10上。详细来说,重配置线路层120位于每一芯片110的主动面111上且包括至少一绝缘层122、多条线路124及多个连接垫126。绝缘层122覆盖芯片110的主动面111,而线路124内埋于绝缘层122内且电连接芯片110的接垫112与部分连接垫126。连接垫126阵列排列且切齐于绝缘层122的相对远离芯片110的表面。特别是,连接垫126位于芯片110的周边区p上。也就是说,通过重配置线路层120的设置,可将芯片110的接垫112的信号从中央区c拉至位于周边区p的连接垫126。

67.接着,请参考图1b,形成多个导电体130分别于连接垫126上且呈阵列排列。在本实施例中,形成导电体130于连接垫126上的方法例如是电镀法或化学镀沉积法或金属贴合蚀刻法或回焊植球法,但不以此为限。此处,导电体130可作为信号垂直连接通道,其中导电体130例如是一金属柱或一金属球。此处,以金属柱作为举例说明,其中金属柱的材质例如是铜、银、锡或其他高导电性材料,但不以此为限。

68.接着,请同时参考图1b与图1c,对晶片10进行一第一次单体化程序,以形成多个芯片单元u(图1c中仅示意地绘示一个)。意即,对晶片10进行研磨及切割程序,而形成单个芯片单元u。此处,每一芯片单元u包括每一芯片110、位于每一芯片110的主动面111上的重配置线路层120以及导电体130。

69.接着,请先参考图1f,对芯片单元u进行一封装程序,以使一封装胶体140覆盖每一芯片110的周围表面115及重配置线路层120,且至少暴露出每一导电体130的一下表面132。详细来说,对芯片单元u进行封装程序的步骤,首先,请参考图1d,提供具有一粘着层30的一载板20。紧接着,将挑选过为良品的多个芯片单元u通过粘着层30而定位于载板20上。此处,粘着层30位于每一芯片110的背面113与载板20之间,意即将芯片110以主动面111朝上(face up)的方式粘贴于载板20上。此处,载板20例如是具有定位点设计的玻璃基板,便宜且透明,可确认晶面粘贴状态(如有无粘结剂气泡、异物等),且于清洗后可重复使用。在一实施例中,粘着层30也可为胶带(tape)型式(如daf tape)贴于芯片110的背面113,使芯片110可直接对位于载板20上的定位点对位粘贴。

70.接着,请参考图1e,形成一封装材料层140a于载板20上,其中封装材料层140a覆盖芯片单元u以及粘着层30。

71.之后,请同时参考图1e与图1f,对封装材料层140a进行一研磨程序,以暴露出每一导电体130的下表面132,而形成封装胶体140。此处,封装胶体140填充于导电体130之间。封装胶体140具有相对的一顶面141以及一底面143。封装胶体140的顶面141切齐于芯片110的背面113,而封装胶体140的底面143切齐于每一导电体130的下表面132。

72.接着,请参考图1g,形成多个焊球150于封装胶体140外,其中焊球150与导电体130电连接。此处,焊球150直接与导电体130结构性且电连接,但不以此为限。

73.之后,请同时参考图1g与图1h,移除粘着层30与载板20,而暴露出每一芯片110的背面113。

74.最后,请同时参考图1h与图1i,对封装胶体140进行一第二次单体化程序,以切割封装胶体140,而形成具有焊球150的多个封装结构100a。至此,已完成晶片级(wafer level)且为球格阵列(ball grid array,bga)的封装结构100a的制作。

75.在结构上,请同时参考图1i、图1j以及图1k,封装结构100a包括芯片110、重配置线路层120、导电体130、封装胶体140以及焊球150。芯片110具有相对的主动面111与背面113及连接主动面111与背面113的周围表面115且包括接垫112。主动面111区分为中央区c及位于中央区c两侧旁的周边区p,而接垫112位于中央区c。此处,芯片110例如是一动态随机存取存储器,但不以此为限。重配置线路层120配置于芯片110的主动面111上且包括绝缘层122、线路124及多个连接垫126。绝缘层122覆盖芯片110的主动面111,而线路124内埋于绝缘层122内且电连接芯片110的接垫112与部分连接垫126。特别是,连接垫126于芯片110的主动面111上的周边区p,意即本实施例的重配置线路层120的设计属于rdlre-layout结构。此外,本实施例的重配置线路层120可为扇入(fan in)设计或扇出(fan-out)设计,于此不加以限制。

76.再者,本实施例的导电体130分别配置于连接垫126上,可作为信号的垂直连接通道。此处,导电体130例如是一金属柱,其中金属柱的材质例如是铜、银、锡或其他高导电性材料,但不以此为限。封装胶体140覆盖芯片110的周围表面115及重配置线路层120,且暴露出芯片110的背面113与导电体130的下表面132。更进一步来说,封装胶体140填充于导电体130之间。封装胶体140具有相对的顶面141以及底面143。封装胶体140的顶面141切齐于芯片110的背面113,而封装胶体140的底面143切齐于每一导电体130的下表面132。封装胶体140还具有多个侧面145,而芯片110的周围表面115至封装胶体140的每一侧面145之间的一水平间距h1、h2相同。此水平间距h1、h2可使视为是阻挡水气的最短距离,封装体厚度可依照国际规格去设计,可极小化规格总厚度。焊球150配置于封装胶体140外,其中焊球150与导电体130结构性且电连接。

77.由于本实施例的芯片110的背面113切齐于封装胶体140的顶面141,意即封装胶体140没有覆盖芯片110的背面113,因此本实施例的芯片110除了可通过导电体130来导电及传热之外,也可通过芯片110的背面113来散热。故,本实施例的封装结构100a可具有较佳的散热效果。再者,本实施例的导电体130可视为线路而与焊球150电连接。此外,本实施例的封装结构100a无需现有基板、窗口及粘晶层的设计,可通过封装胶体140来取代基板,以保护及支撑芯片110。由于本实施例的封装结构100a无窗口的设计,因此单位面积封装可容许

最大芯片,意即可有效利用空间最大化。另外,因为材料与界面的简化,因此本实施例的封装结构100a除了可具有较佳的信号传递效果之外,也具有薄化设计,可具有较薄的封装厚度。

78.在此必须说明的是,下述实施例沿用前述实施例的元件标号与部分内容,其中采用相同的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,下述实施例不再重复赘述。

79.图2是依照本发明的一实施例的一种封装结构的剖面示意图。请同时参考图1i以及图2,本实施例的封装结构100b与图1i的封装结构100a相似,两者的差异在于:在本实施例中,每一导电体135例如是一金属球,其中金属球的材质包括锡(sn)或其他低温的焊接材料,例如是无铅焊锡、锡铟(sn-in)、锡铅(sn-pb)、锡铋(sn-bi)或锡银铜(sn-ag-cu)。此处,封装胶体140的底面143切齐于每一导电体135的下表面137,而导电体135直接结构性且电连接焊球150。简言之,本发明并不限制导电体130、135的结构型态,其可为柱状、球状或其他适当的结构型态。

80.图3是依照本发明的另一实施例的一种封装结构的剖面示意图。请同时参考图1i以及图3,本实施例的封装结构100c与图1i的封装结构100a相似,两者的差异在于:在本实施例中,封装结构100c还包括一附加封装胶体160c以及一附加重配置线路层170。附加封装胶体160c覆盖芯片110的背面113以及封装胶体140的顶面141及侧面145。附加封装胶体160c的一附加底面163c切齐于封装胶体140的一底面143。附加重配置线路层170配置于封装胶体140的底面143以及附加封装胶体160c的附加底面163c上,且位于焊球150c与导电体130之间。附加重配置线路层170的属于扇出(fan-out)型结构,其中附加重配置线路层170的边缘切齐于附加封装胶体160c的边缘。附加重配置线路层170电连接导电体130与焊球150c。本实施例的封装结构100c可适用于小芯片但对外输入/输出接点(i/o)多的封装体。

81.图4是依照本发明的另一实施例的一种封装结构的剖面示意图。请同时参考图1i以及图4,本实施例的封装结构100d与图1i的封装结构100a相似,两者的差异在于:在本实施例中,封装结构100d还包括一附加封装胶体160d,具有相对的一附加顶面161d以及一附加底面163d,并且覆盖芯片110的周围表面115。部分重配置线路层120延伸出芯片110的主动面111,并且配置于附加封装胶体160d的附加底面163d上。芯片110的背面113切齐于封装胶体140的顶面141以及附加封装胶体160d的附加顶面161d,可使封装结构100d具有较佳的散热效果。芯片110的主动面111切齐于附加封装胶体160d的附加底面163d,而重配置线路层120的边缘切齐于附加封装胶体160d的边缘。举例来说,若是芯片110面积较小,但是封装规格(package spec)面积较大,就必须将外接的输入/出接点(i/o)延伸,如此才有足够空间容纳更多对外输入/出接点的需求。制作上,可先形成附加封装胶体160d,再形成重配置线路层120,之后在形成封装胶体140,以保护导电体130与芯片110及重配置线路层120,以避免封装后测试(final test,ft)时压伤。

82.图5是依照本发明的另一实施例的一种封装结构的剖面示意图。请同时参考图4以及图5,本实施例的封装结构100e与图4的封装结构100d相似,两者的差异在于:在本实施例中,封装结构100e的封装胶体140e覆盖附加封装胶体160d的附加顶面161d以及芯片110的背面113。由于本实施例的封装胶体140e将芯片110及附加封装胶体160d完全包覆起来,因此具有较佳的保护性。

83.综上所述,在本发明的封装结构的设计中,导电体配置于重配置线路层的连接垫上,而芯片的接垫可通过重配置线路层及导电体与焊球电连接,且封装胶体覆盖重配置线路层并填充于导电体之间,且封装胶体至少暴露出导电体的下表面。由此,本发明的封装结构无须现有基板、窗口及粘晶层的设计,可通过封装胶体来取代基板,以保护及支撑芯片。再者,因为本发明的封装结构无窗口的设计,因此单位面积封装可容许最大芯片,意即可有效利用空间最大化。此外,因为材料与界面的简化,因此本发明的封装结构除了可具有较佳的信号传递效果之外,也具有薄化设计,可具有较薄的封装厚度。

84.虽然结合以上实施例公开了本发明,然而其并非用以限定本发明,任何所属技术领域中具有通常知识者,在不脱离本发明的精神和范围内,可作些许的更动与润饰,故本发明的保护范围应当以附上的权利要求所界定的为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1