半导体装置的制作方法

半导体装置

1.关联申请

2.本技术享有以日本专利申请2020-45118号(申请日:2020年3月16日)作为基础申请的优先权。本技术通过参照该基础申请而包含基础申请的全部内容。

技术领域

3.本发明的实施方式涉及半导体装置。

背景技术:

4.进行了设计用于面向发电或送电、泵或鼓风机等的旋转机、通信系统或工厂等的电源装置、利用交流马达的铁道、电动汽车、家庭用电化制品等广泛领域的mosfet(metal-oxide-semiconductor field-effect-transistor,金属-氧化物半导体场效应晶体管)或igbt(insulated gate bipolar transistor,绝缘栅双极型晶体管)等的电力控制的功率半导体芯片的开发。

5.另外,进行了使用了所述功率半导体芯片的作为功率模块的半导体装置的开发。对于这样的半导体装置,要求高电流密度化、低损耗化、高放热化等技术条件。

技术实现要素:

6.本发明的实施方式提供可靠性高的半导体装置。

7.实施方式的半导体装置具备:半导体基板,所述半导体基板具有基板底面和基板上表面,在基板底面具有凹部;半导体元件,所述半导体元件设置于凹部之上;以及第1电极,所述第1电极设置于凹部内,凹部具有凹部侧面和凹部上表面,凹部侧面与凹部上表面所成的角为90度以上,第1电极的膜厚为凹部的深度的1/2以上。

附图说明

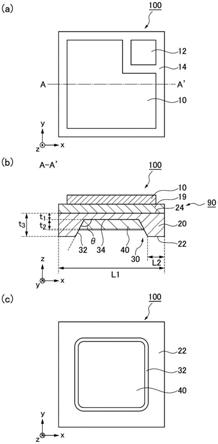

8.图1(a)~(c)是第1实施方式的半导体装置的示意俯视图、示意截面图及示意仰视图。

9.图2(a)~(f)是表示第1实施方式的半导体装置的制造方法中的制造中途的半导体装置的示意截面图。

10.图3是成为第1实施方式的比较方式的半导体装置的示意截面图。

11.图4是第2实施方式的半导体装置的示意截面图。

12.图5(a)、(b)是第3实施方式的半导体装置的示意截面图。

13.图6是第4实施方式的半导体装置的示意截面图。

具体实施方式

14.以下,参照附图且对本发明的实施方式进行说明。需要说明的是,在以下的说明中,有时对同一或类似的构件标注同一符号。另外,对于一度说明的构件等有时适当省略其

说明。

15.本说明书中,为了表示部件等的位置关系,将附图的上方记述为“上”,将附图的下方记述为“下”。本说明书中,“上”、“下”的概念未必是表示与重力的方向的关系的术语。

16.(第1实施方式)

17.本实施方式的半导体装置具备:具有基板底面和基板上表面且在基板底面具有凹部的半导体基板、设置于凹部之上的半导体元件以及设置于凹部内的第1电极,凹部具有凹部侧面和凹部上表面,凹部侧面与凹部上表面所成的角为90度以上,第1电极的膜厚为凹部的深度的1/2以上。

18.图1是本实施方式的半导体装置100的示意截面图。

19.图1(a)是本实施方式的半导体装置100的示意俯视图。图1(b)是本实施方式的半导体装置100的示意截面图。图1(c)是本实施方式的半导体装置100的示意仰视图。

20.使用图1,对本实施方式的半导体装置100进行说明。

21.半导体装置100具备半导体基板20、半导体元件90和第1电极40。

22.半导体基板20例如为si(硅)基板。但是,半导体基板20也可以是sic(碳化硅)基板、氮化物半导体基板其他的半导体基板。

23.半导体基板20具有基板底面22和基板上表面24。另外,半导体基板20具有设置于基板底面22的凹部30。其中,凹部30具有凹部侧面32和凹部上表面34。

24.需要说明的是,基板上表面24侧的半导体装置100的面被称为器件面或元件面。

25.如图1(c)中所示的那样,例如凹部30被设置于基板底面22的中央附近,但并不限定于此。另外,基板底面22被设置于凹部30的周围。

26.例如为了半导体装置100的制造容易性,凹部上表面34优选与基板上表面24平行。但是,凹部上表面34也可以不与基板上表面24平行。

27.凹部侧面32与凹部上表面34所成的角θ优选为90度以上。

28.半导体元件90的至少一部分被设置于凹部30之上。另外,半导体元件90的一部分被设置于元件区域19内。本实施方式的半导体元件90例如为n型的立式mosfet。源极电极10介由元件区域19而设置于基板上表面24上。若换而言之,则源极电极10被设置于元件区域19之上。在半导体元件90为mosfet的情况下,源极电极10作为所述半导体元件90的源极电极而发挥功能。

29.第1电极40被设置于凹部30内。在半导体元件90为mosfet的情况下,第1电极40例如作为所述半导体元件90的漏极电极而发挥功能。

30.需要说明的是,本实施方式的半导体元件90也可以为p型的mosfet、si-igbt、si-frd(fast recovery diode,快速恢复二极管)、使用了sic(碳化硅)的sic-igbt、sic-mosfet或sic-sbd(schottky barrier diode,肖特基势垒二极管)、或使用了iii-v族半导体中v族元素为氮的氮化物半导体的gan-mosfet等。例如作为mosfet,也可以为平面型的mosfet或沟槽型的mosfet。例如作为mosfet,也可以为卧式的mosfet。另外,半导体元件90也可以不为所谓的功率半导体元件。

31.第1电极40及源极电极10例如由cu(铜)、ag(银)、au(金)或al(铝)等形成,包含cu、ag、au或al。需要说明的是,第1电极40及源极电极10也可以包含pt(铂)、pd(钯)、sn(锡)或ni(镍)等其他的金属。

32.第1电极40的膜厚t2优选比设置有凹部30的部分的半导体基板20的基板厚t1厚(图1(b))。另外,设置有凹部30的部分的半导体基板20的基板厚t1优选为100μm以下(图1(b))。需要说明的是,设置有凹部30的部分的半导体基板20的基板厚t1也可以比100μm厚。另外,未设置凹部30的部分的基板底面22的长度l2优选为基板上表面24的长度l1的1/4以下(图1(b))。进而,未设置凹部30的部分的基板底面22的长度l2优选为基板上表面24的长度l1的1/10以下。进而,第1电极40的膜厚t2优选为凹部30的深度t

3-t1的1/2以上。需要说明的是,t3为半导体基板20的基板厚。

33.图2是表示本实施方式的半导体装置100的制造方法中的制造中途的半导体装置100的示意截面图。

34.首先,在半导体基板20上形成具有半导体元件90的一部分的元件区域19。接着,在元件区域19之上分别形成作为源极电极10的源极电极10a、10b、10c及10d(图2(a))。

35.接着,将形成有源极电极10a、10b、10c及10d的面使用粘接剂200固定于玻璃基板等支撑基板210之上(图2(b))。

36.接着,使用背面磨削等将半导体基板20薄膜化(图2(c))。

37.接着,通过光致抗蚀剂的涂布、曝光及显影、半导体基板20的蚀刻及光致抗蚀剂的除去,在半导体基板20上形成作为凹部30的凹部30a、凹部30b、凹部30c及凹部30d。接着,通过溅射或镀覆及cmp(chemical mechanical polishing,化学机械研磨)等,在凹部30a、凹部30b、凹部30c及凹部30d内形成作为第1电极40的第1电极40a、第1电极40b、第1电极40c及第1电极40d(图2(d))。需要说明的是,本实施方式中的镀覆也可以是电解镀覆,也可以是非电解镀覆。

38.接着,将半导体基板20从支撑基板210上剥离,粘贴于切割胶带220之上而固定(图2(e))。

39.接着,例如通过刀片切割进行单片化,获得作为半导体装置100的半导体装置100a、半导体装置100b、半导体装置100c及半导体装置100d(图2(f))。

40.需要说明的是,在图2中,设置有凹部30的部分的半导体基板20的基板厚按照比第1电极40的膜厚厚的方式图示。但是,如上所述,第1电极40的膜厚比设置有凹部30的部分的半导体基板20的基板厚厚。

41.接着,记载本实施方式的半导体装置100的作用效果。

42.图3是成为本实施方式的比较方式的半导体装置800的示意截面图。在半导体装置800中,未设置凹部30。而且,遍及基板底面22的整面而设置有第1电极40。

43.在如半导体装置800那样遍及基板底面22的整面而设置有第1电极40的情况下,在通过刀片切割而进行单片化时,难以产生第1电极40的切断中的刀片的自动磨锐。因此,在半导体装置800中产生裂纹(龟裂)或崩刃(微小的缺口),存在机械强度和可靠性降低的问题。

44.另外,在利用激光的切割的情况下,在半导体装置800的侧面,通过蒸镀而附着半导体基板20中所含的半导体材料、第1电极40中所含的金属材料。因此,存在半导体装置800的机械强度和可靠性降低的问题。

45.进而,在遍及基板底面22的整面而设置第1电极40的情况下,因半导体基板20与第1电极40的热膨胀系数之差而产生较大翘曲,存在操作变得困难的问题。

46.本实施方式的半导体装置100具备:具有基板底面和基板上表面且在基板底面具有凹部的半导体基板、设置于凹部之上的半导体元件以及设置于凹部内的第1电极,凹部具有凹部侧面和凹部上表面,凹部侧面与凹部上表面所成的角为90度以上,第1电极的膜厚为凹部的深度的1/2以上。

47.在基板底面22设置有凹部30,在凹部30内设置有第1电极40。因此,在刀片切割时,也可以不将第1电极40通过刀片而切断。因此,能够抑制裂纹的产生和崩刃的产生。因而,变得能够提供可靠性高的半导体装置。

48.另外,凹部侧面32与凹部上表面34所成的角为90度以上。若凹部侧面32与凹部上表面34所成的角低于90度,则在凹部侧面32与凹部上表面34的交线及其周边变得容易受到应力,机械强度和可靠性降低。通过凹部侧面32与凹部上表面34所成的角为90度以上,半导体基板20从应力被释放。因而,变得能够提供可靠性高的半导体装置。

49.第1电极40的膜厚t2优选比设置有凹部30的部分的半导体基板20的基板厚t1厚。这是由于,通过增厚第1电极40的膜厚t2,提高半导体装置100的机械强度。

50.设置有凹部30的部分的半导体基板20的基板厚t1优选为100μm以下。在这样的情况下,特别优选应用本实施方式的半导体装置100。

51.未设置凹部30的部分的基板底面22的长度l2优选为基板上表面24的长度l1的1/4以下。这是由于,尽可能增大设置第1电极40的部分而减小半导体元件90的电阻。

52.第1电极40的膜厚t2优选为凹部30的深度t

3-t1的1/2以上。这是由于,尽可能增厚第1电极40的膜厚而提高半导体装置的机械强度。

53.根据本实施方式的半导体装置100,变得能够提供可靠性高的半导体装置。

54.(第2实施方式)

55.在本实施方式的半导体装置120中,第1电极40遍及凹部上表面34、凹部侧面32及基板底面22而设置这一点,第1及第2实施方式的半导体装置不同。这里,省略第1及第2实施方式的半导体装置重复的内容的记载。

56.图4是本实施方式的半导体装置120的示意截面图。

57.也可以设置与基板底面22相接的第1电极40的部分42。但是,与基板底面22相接的第1电极40的部分42的膜厚t4优选不厚。具体而言,第1电极40的膜厚t2优选比与基板底面22相接的第1电极40的部分的膜厚t4的2倍大。这是由于,若与基板底面22相接的第1电极40的部分42的膜厚t4过厚,则在将与基板底面22相接的第1电极40的部分切断时,如上所述,有可能变得难以产生刀片的自动磨锐,可靠性降低。

58.第1电极的底面45例如优选相对于基板上表面24及基板底面22平行,但并不特别限定于此。

59.通过本实施方式的半导体装置120,也能够提供可靠性高的半导体装置。

60.(第3实施方式)

61.在本实施方式的半导体装置130及半导体装置140中,第1电极40具有含有第1元素的第1层44、和设置于第1层之上且含有与第1元素不同的第2元素的第2层46这一点,第1至第3实施方式的半导体装置不同。另外,第1电极40在与凹部侧面32及凹部上表面34相接的部分具有阻挡金属这一点,第1至第3实施方式的半导体装置不同。其中,省略第1至第3实施方式的半导体装置重复的内容的记载。

62.图5是本实施方式的半导体装置130及半导体装置140的示意截面图。图5(a)是本实施方式的半导体装置130的示意截面图,图5(b)是本实施方式的半导体装置140的示意截面图。

63.第1元素及第2元素没有特别限定,可以从cu、ag、au、al、pt、pd、sn或ni等元素中选择。

64.作为阻挡金属48,优选使用ti(钛)或tini,但并不限定于此。

65.在图5(a)的半导体装置130中,第2层46的膜厚大致恒定。另一方面,在图5(b)的半导体装置140中,第1层44与第2层46的边界与基板上表面24或基板底面22平行。任一者均可以优选使用。

66.通过本实施方式的半导体装置130,也能够提供可靠性高的半导体装置。

67.(第4实施方式)

68.在本实施方式的半导体装置150中,第1电极40进一步具有设置于第1层与上述第2层之间且含有ti(钛)或ta(钽)的第3层49这一点,第1至第4实施方式的半导体装置不同。这里,省略第1至第4实施方式的半导体装置重复的内容的记载。

69.图6是本实施方式的半导体装置150的示意截面图。

70.第3层49为防止扩散层。由此,能够抑制第1层44中所含的第1元素与第2层46中所含的第2元素相互扩散,因此变得能够提供可靠性更高的半导体装置。需要说明的是,作为第3层49,也可以优选使用snag合金或cusn合金等。

71.通过本实施方式的半导体装置150,也能够提供可靠性高的半导体装置。

72.对本发明的几个实施方式及实施例进行了说明,但这些实施方式及实施例是作为例子而提出的,并不意图限定发明的范围。这些新颖的实施方式可以以其他各种方式实施,在不脱离发明的主旨的范围内可以进行各种省略、置换、变更。这些实施方式和其变形包含于发明的范围和主旨中,同时包含于权利要求书中记载的发明和其同等的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1