半导体整合装置的制作方法

半导体整合装置

[0001]

本申请是中国发明专利申请(申请号:201310240289.x,申请日:2013年06月18日,发明名称:半导体整合装置)的分案申请。

技术领域

[0002]

本发明涉及一种半导体整合装置,尤其是涉及一种包含鳍式场效晶体管(fin field effect transistor,以下简称为finfet)元件与保护结构的半导体整合装置。

背景技术:

[0003]

当元件发展至65纳米技术世代后,使用传统平面式的金属氧化物半导体(metal-oxide-semiconductor,mos)晶体管制作工艺是难以持续微缩,因此,现有技术是提出以立体或非平面(non-planar)多栅极晶体管元件如finfet元件取代平面晶体管元件的解决途径。

[0004]

现有finfet元件是先利用蚀刻等方式图案化一基板表面的硅层,以在基板中形成一鳍片状的硅薄膜(图未示),并在硅薄膜上形成包覆部分硅薄膜的绝缘层,随后形成包覆部分绝缘层与部分硅薄膜的栅极,最后再通过离子注入制作工艺与回火制作工艺等步骤在未被栅极包覆的鳍片状的硅薄膜中形成源极/漏极。由于finfet元件的制作工艺能与传统的逻辑元件制作工艺整合,因此具有相当的制作工艺相容性。此外,当finfet元件设置于硅覆绝缘(silicon-on-insulator,soi)基底上时,传统隔离技术如浅沟隔离(shallow trench isolation)等可省却。更重要的是,由于finfet元件的立体结构增加了栅极与鳍片状的硅基体的接触面积,因此可增加栅极对于通道区域的载流子控制,从而降低小尺寸元件面临的由源极引发的能带降低(drain induced barrier lowering,dibl)效应以及短通道效应(short channel effect)。此外,由于finfet元件中同样长度的栅极具有更大的通道宽度,因此可获得加倍的漏极驱动电流。

[0005]

虽然finfet元件可获得较高的漏极驱动电流,但finfet元件仍然面对许多待解决的问题。举例来说,finfet元件的鳍片结构因具有纤长的轮廓特征,所以非常容易受到物理性或电性的外力影响,甚或因上述外力导致毁损。是以,finfet元件的鳍片结构一直都需要有效的保护结构。

技术实现要素:

[0006]

因此,本发明的一目的在于提供一包含半导体元件以及可有效保护该半导体元件的整合装置。

[0007]

为达上述目的,本发明提供了一种半导体整合装置,该半导体整合装置包含一基底,该基底上至少界定有一主动区域、多个主动鳍片(active fin),设置于该主动区域内,且该些主动鳍片沿着一第一方向延伸、多个条状第一保护鳍片(protecting fin),环绕该主动区域,且该些条状第一保护鳍片都沿着该第一方向延伸,且该些条状第一保护鳍片中的一部分分别与该些主动鳍片位于同一列且被空隙彼此分隔、多个条状强化结构,设置于

该些条状第一保护鳍片上、以及长形接触窗(slot contact),设置于该些主动鳍片上,其中该长形接触窗与该些条状强化结构同时形成。

[0008]

本发明另提供一种半导体整合装置,该半导体整合装置包含一基底,该基底上至少界定有一主动区域、多个主动鳍片(active fin),设置于该主动区域内,且该些主动鳍片沿着一第一方向延伸、多个条状第一保护鳍片(protecting fin)和多个条状第二保护鳍片,环绕该主动区域,其中该些条状第一保护鳍片沿着该第一方向延伸,且该些条状第一保护鳍片与该些主动鳍片位于同一列且被空隙彼此分隔,该些条状第二保护鳍片沿着一第二方向延伸,且该第二方向不同于该第一方向、以及框状强化结构,将该些条状第一保护鳍片和该些条状第二保护鳍片电连接在一起。

[0009]

本发明又提供一种半导体整合装置,该半导体整合装置包含一基底,该基底上至少界定有一主动区域、多个主动鳍片,设置于该主动区域内、多个保护鳍片框(protecting fin frame),环绕该主动区域、多个条状强化结构,设置于该些保护鳍片框上,将该些保护鳍片框电连接在一起、以及长形接触窗(slot contact),设置于该主动鳍片上,其中该长形接触窗与该些条状强化结构同时形成。

[0010]

根据本发明所提供的半导体整合装置,是在该主动区域内设置用以建构半导体元件的该等主动鳍片,同时于该主动区域外设置环绕该主动区域的该等第一保护鳍片或该等保护鳍片框。通过该等第一保护鳍片与该等保护鳍片框的设置,可避免该主动区域内纤长的该等主动鳍片受到物理性或电性的外力影响。

附图说明

[0011]

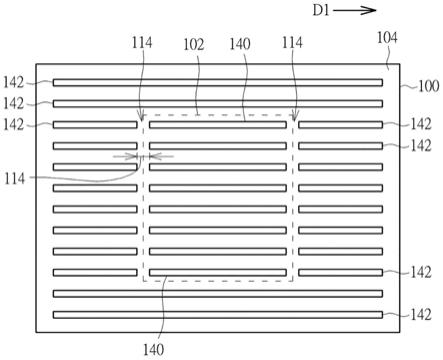

图1至图4为本发明所提供的一种半导体整合装置的第一优选实施例的示意图;

[0012]

图5为第一优选实施例的一变化型的示意图;

[0013]

图6为本发明所提供的一种半导体整合装置的第二优选实施例的示意图;

[0014]

图7为第二优选实施例的一变化型的示意图;

[0015]

图8至图9为本发明所提供的一种半导体整合装置的第三优选实施例的示意图;

[0016]

图10为第三优选实施例的一变化型的示意图;

[0017]

图11为本发明所提供的一种半导体整合装置的第四优选实施例的示意图;

[0018]

图12为第四优选实施例的一变化型的示意图。

[0019]

主要元件符号说明

[0020]

100、200、300、400

ꢀꢀꢀꢀꢀ

基底

[0021]

102、202、302、402

ꢀꢀꢀꢀꢀ

主动(有源)区域

[0022]

104、204、304、404

ꢀꢀꢀꢀꢀ

周边区域

[0023]

110、310a、310b

ꢀꢀꢀꢀꢀꢀꢀ

轴心图案

[0024]

112

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

间隙壁图案

[0025]

114、214、216、444

ꢀꢀꢀꢀꢀ

空隙

[0026]

140、240、340、440

ꢀꢀꢀꢀ

主动鳍片

[0027]

142、242

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一保护鳍片

[0028]

244

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二保护鳍片

[0029]

342、442

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

保护鳍片框

[0030]

442a

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

最内圈保护鳍片框

[0031]

444

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

空隙

[0032]

150、250、350、450

ꢀꢀꢀꢀꢀ

强化结构

[0033]

160、260、360、460

ꢀꢀꢀꢀꢀ

栅极层、接触插塞、或长形接触窗

[0034]

d1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一方向

[0035]

d2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二方向

具体实施方式

[0036]

请参阅图1至图4,图1至图4为本发明所提供的一种半导体整合装置的第一优选实施例的示意图。如图1所示,本优选实施例首先提供一基底100,基底100可包含一硅覆绝缘(silicon-on-insulator,soi)基底,如熟悉该项技术的人士所知,soi基底由下而上可依序包含一硅基底、一底部氧化(bottom oxide,box)层、以及形成于底部氧化层上的半导体层,如一具单晶结构的硅层。另外,本优选实施例提供的基底可包含一块硅(bulk silicon)基底。基底100上界定有一主动区域102与一环绕主动区域102的周边区域104。熟悉该项技术者应知,虽然本优选实施例中周边区域104是环绕主动区域102,但周边区域104与主动区域102的相对关系及大小是可根据不同的产品需求而变化,故不限于此。此外,基底100上形成一硬掩模层(图未示)。在本优选实施例中,硬掩模层包含一复合膜层,可以是一氧化硅层/氮化硅层/氧化硅层的复合膜层,但不限于此。请继续参阅图1。接下来,在硬掩模层上形成多个轴心图案110,轴心图案110可包含多晶硅材料,但不限于此。值得注意的是,某些轴心图案110可如图1所示,横跨周边区域104与主动区域102。

[0037]

请参阅图2。在基底100上形成轴心图案110之后,是在基底100上全面性地形成一材料层如一绝缘层(图未示),例如但不限于一利用原子层沉积方法(atomic layer deposition,ald)或化学气相沉积方法(chemical vapor deposition,cvd)形成的氮化硅(silicon nitride,sin)层。熟悉该项技术的人士应知,任何蚀刻率不同于轴心图案110的合适材料都可用以作为本优选实施例所提供的材料层。接下来,回蚀刻材料层,以于各轴心图案110的侧壁形成多个间隙壁图案112。

[0038]

请参阅图3。在形成间隙壁图案112之后,进行一蚀刻制作工艺,移除轴心图案110。值得注意的是,本优选实施例可在此蚀刻制作工艺之前、此蚀刻制作工艺之中或此蚀刻制作工艺之后,移除部分的间隙壁图案112,尤其是轴心图案110头尾两端的间隙壁图案112。更重要的是,本优选实施例在此蚀刻制作工艺之前、之中或之后切割横跨主动区域102与周边区域104的间隙壁图案112,而于部分间隙壁图案112之间形成空隙(gap)114。且如图3所示,空隙114形成于主动区域102与周边区域104之间,用以分离原本横跨主动区域102与周边区域104的间隙壁图案112。

[0039]

请参阅图4。在形成间隙壁图案112与空隙114之后,是利用间隙壁图案112作为掩模图案化硬掩模层,以定义出鳍片结构的位置与大小。随后再以图案化硬掩模作为一蚀刻掩模蚀刻基底100,而于基底100上形成多个鳍片结构。而在形成鳍片结构之后,可依产品所需保留或移除图案化硬掩模。值得注意的是,形成于主动区域102内的鳍片结构可作为finfet元件中源极/漏极的设置之处,故主动区域102内的鳍片结构即为主动鳍片140,且主动鳍片140如图4所示,沿一第一方向d1延伸。更值得注意的是,形成于周边区域104内的鳍

片结构可作为finfet元件甚或主动区域102的保护结构,故这些条状鳍片结构即为第一保护鳍片(protecting fin)142。第一保护鳍片142如图4所示环绕主动区域102,且第一保护鳍片142也沿第一方向d1延伸。更重要的是,原本形成于间隙壁图案112之间的空隙114也转移至鳍片结构之间。因此设置于同一列的主动鳍片140与第一保护鳍片142通过空隙114彼此分隔。更重要的是,空隙114是分离主动区域102内的主动鳍片140与周边区域104内的第一保护鳍片142,以避免第一保护鳍片142影响到主动鳍片140的特性以及元件的实际电性表现。而在形成主动鳍片140与第一保护鳍片142之后,可进行主动区域102内各组成元件的制作,例如栅极介电层、栅极层、轻掺杂漏极、栅极间隙壁、源极/漏极等的制作,以形成至少一finfet晶体管元件(图未示)。此外,熟悉该项技术的人士应知金属栅极制作工艺、选择性外延成长(selective epitaxial growth,seg)制作工艺、金属硅化物制作工艺、内层介电层、接触插塞、多层内连线制作工艺等,都可依需要整合于finfet晶体管元件制作工艺,在此并不多加赘述。

[0040]

请参阅图5,图5为本优选实施例的一变化型的示意图。根据本变化型,在制作前述主动区域102内各组成元件的同时,也可于周边区域104内的第一保护鳍片142上更设置多个条状强化结构150。如图5所示,在本变化型中,可在主动区域102内形成栅极层160的同时,在周边区域104内的第一保护鳍片142上形成强化结构150,故强化结构150可包含半导体材料如多晶硅。另外,熟悉该项技术的人士应知,主动区域102内栅极层160与主动鳍片140的关系仅为例示,栅极层160可依产品需求跨过较多或较少的主动鳍片140,且不同的栅极层160可跨越不同的主动鳍片140。或者,在本变化型中,可在主动区域102内形成金属栅极、接触插塞(contact plug)或长形接触窗(slot contact)160时,同时于周边区域104内的第一保护鳍片142上形成强化结构150,故强化结构150可包含金属材料。同理,金属栅极、接触插塞或长形接触窗160与主动鳍片140的关系也可依产品需求而不同于图5所示者。值得注意的是,强化结构150如图5所示,垂直于第一保护鳍片142,且电连接不同列的第一保护鳍片142,故第一保护鳍片142与强化结构150可构成一直交(orthogonal)格栅图案,更加强化第一保护鳍片142的结构强度。另外,在后续进行主动区域102内金属内连线制作工艺时,更可同时于周边区域104内强化结构150上方形成与其实体以及电连接的金属层(但与主动区域102内的金属内连线以及主动鳍片电性隔离),以更强化第一保护鳍片142的结构强度。

[0041]

根据本优选实施例及其变化型所提供的半导体整合装置,在主动区域102内设置用以建构半导体元件的主动鳍片140,同时于主动区域102外设置环绕主动区域102的第一保护鳍片142以及强化结构150。通过第一保护鳍片142与强化结构150的设置,作为提供电性隔离的保护环(guard ring)或提供应力隔离的密封环(seal ring),以避免主动区域102内纤长的主动鳍片142受到物理性或电性的外力影响。另外,由于第一保护鳍片142与主动鳍片140同时形成,而强化结构150可与其他元件如栅极层或接触插塞的金属层等同时形成,故本优选实施例可在不增加制作工艺复杂度的前提下,成功地提供主动鳍片140需要的保护结构。

[0042]

请参阅图6,图6为本发明所提供的一种半导体整合装置的第二优选实施例的示意图。首先需注意的是,第二优选实施例中,保护结构的制作步骤与第一优选实施例相同,故该等制作步骤此后不再绘示。如图6所示,本优选实施例提供一基底200,例如一soi基底或

块硅基底。基底200上定义有一主动区域202与一环绕主动区域202的周边区域204。如前所述,虽然本优选实施例中,周边区域204环绕主动区域202,但周边区域204与主动区域202的相对关系可根据不同的产品需求而变化,故不限于此。此外,基底200上形成一硬掩模层(图未示)。接下来,在硬掩模层上形成多个轴心图案(图未示),随后在各轴心图案的侧壁形成多个间隙壁图案(图未示)。

[0043]

请继续参阅图6。在形成间隙壁图案之后,进行一蚀刻制作工艺移除轴心图案。值得注意的是,本优选实施例可在此蚀刻制作工艺之前、之中或之后,移除部分的间隙壁图案,尤其是轴心图案头尾两端的间隙壁图案。此外本优选实施例于此蚀刻制作工艺之前、之中或之后切割横跨主动区域202与周边区域204的轴心图案与间隙壁图案,而在部分间隙壁图案之间形成空隙。

[0044]

请仍然参阅图6。在形成间隙壁图案与空隙之后,是利用间隙壁图案作为掩模图案化硬掩模层,以定义出鳍片结构的位置与大小。随后利用图案化硬掩模作为蚀刻掩模蚀刻基底200,而于基底200上形成多个鳍片结构。而在形成鳍片结构之后,可依产品所需保留或移除图案化硬掩模。如前所述,形成于主动区域202内的鳍片结构即为主动鳍片240,且主动鳍片240如图6所示,沿一第一方向d1延伸。更值得注意的是,本优选实施例在周边区域204内形成多个第一保护鳍片242与多个第二保护鳍片244。第一保护鳍片242沿第一方向d1延伸并沿一第二方向d2排列;而第二保护鳍片244沿第二方向d2延伸,并沿第一方向d1排列。第一方向d1与第二方向d2不同,在本优选实施例中第一方向d1与第二方向d2彼此垂直,但不限于此。是以,第一保护鳍片242如图6所示,设置于主动区域202的相对两侧,而第二保护鳍片244设置于主动区域202的另外相对两侧。也就说说,第一保护鳍片242与第二保护鳍片244环绕主动区域202而提供保护功能。另外如前所述,原本形成于间隙壁图案之间的空隙也转移至鳍片结构之间。因此设置于同一列的主动鳍片240与第一保护鳍片242分别通过一空隙214彼此分隔。另外,主动区域202内的主动鳍片240与第二保护鳍片也分别通过空隙216彼此分隔。换句话说,空隙214与空隙216是分离主动区域202内的主动鳍片240与周边区域204内的第一保护鳍片242/第二保护鳍片244,以避免第一保护鳍片242与第二保护鳍片244影响到主动鳍片240的特性以及元件的实际电性表现。接下来,可进行主动区域202内各组成元件的制作。

[0045]

请参阅图7,图7为本优选实施例的一变化型的示意图。根据本变化型,在制作主动区域202内各组成元件的同时,也可于周边区域204内的第一保护鳍片242与第二保护鳍片244上更设置至少一框形强化结构250。如图7所示,本变化型中,可在主动区域202内形成栅极层260的同时,在周边区域204内的第一保护鳍片242与第二保护鳍片244上形成框形强化结构250,故框形强化结构250可包含半导体材料如多晶硅。另外,熟悉该项技术的人士应知,主动区域202内栅极层260与主动鳍片240的关系仅为例示,栅极层260可依产品需求跨过较多或较少的主动鳍片240,且不同的栅极层260可跨越不同的主动鳍片240。或者,在本变化型中,可在主动区域202内形成金属栅极、接触插塞或长形接触窗260时,同时在周边区域204内的第一保护鳍片242与第二保护鳍片244上形成框形强化结构250,故框形强化结构250可包含金属材料。同理,金属栅极、接触插塞或长形接触窗260与主动鳍片240的关系也可依产品需求而不同于图7所示者。值得注意的是,强化结构250如图7所示,垂直于第一保护鳍片242与第二保护鳍片244,并且将周边区域204内所有的第一保护鳍片242与第二保护

鳍片244全部电连接在一起,并更强化第一保护鳍片242与第二保护鳍片244的结构强度,以提供主动鳍片240更好的保护。另外,在后续进行主动区域202内的金属内连线制作工艺时,更可同时于周边区域204内的强化结构250上方形成与其实体以及电连接的金属层(但与主动区域202内的金属内连线以及主动鳍片电性隔离),以更强化第一保护鳍片242与第二保护鳍片244的结构强度。

[0046]

根据本优选实施例及其变化型所提供的半导体整合装置,在主动区域202内设置用以建构半导体元件的主动鳍片240,同时于主动区域202外设置环绕主动区域202的第一保护鳍片242、第二保护鳍片244以及强化结构250。通过第一保护鳍片242、第二保护鳍片244与强化结构250的设置,可作为提供电性隔离的保护环或提供应力隔离的密封环,故可避免主动区域202内纤长的主动鳍片240受到物理性或电性的外力影响。如前所述,由于第一保护鳍片242、第二保护鳍片244与主动鳍片240同时形成,而强化结构250可与其他元件如栅极层或接触插塞的金属层等同时形成,故本优选实施例可在不增加制作工艺复杂度的前提下,成功地提供主动鳍片240需要的保护结构。

[0047]

请参阅图8至图9,图8至图9为本发明所提供的一种半导体整合装置的第三优选实施例。如图8所示,本优选实施例提供一基底300,基底300上也定义有一主动区域302与一环绕主动区域302的周边区域304。如前所述,虽然本优选实施例中,周边区域304环绕主动区域302,但周边区域304与主动区域302的相对关系可根据不同的产品需求而变化,故不限于此。此外,基底300上形成一硬掩模层(图未示)。请继续参阅图8。接下来,在硬掩模层上形成多个轴心图案310a/310b,轴心图案310a/310b可包含多晶硅材料,但不限于此。值得注意的是,在本优选实施例中,设置于主动区域302内的轴心图案310a与设置于周边区域304内的轴心图案310b的形态并不相同:如图8所示,主动区域302内的轴心图案310a可根据实际产品的需要形成于主动区域302内;但周边区域304内的轴心图案310b却是以环绕并且密封主动区域302的框状设置于周边区域304内。

[0048]

请参阅图9。在基底300上形成轴心图案310a/310b之后,在基底300上全面性地形成一蚀刻率异于轴心图案310a/310b的材料层。接下来,回蚀刻材料层,以于各轴心图案310a/310b的侧壁形成多个间隙壁图案(图未示)。并且,在形成间隙壁图案之后,进行一蚀刻制作工艺,移除轴心图案310a/310b。值得注意的是,本优选实施例可在此蚀刻制作工艺之前、之中或之后,移除部分的间隙壁图案,尤其是主动区域302内轴心图案310a头尾两端的间隙壁图案。随后利用间隙壁图案作为掩模图案化硬掩模层,以定义出鳍片结构的位置与大小。随后再以图案化硬掩模作为一蚀刻掩模蚀刻基底300,而于基底300上形成多个鳍片结构。并且在形成鳍片结构之后,可依产品所需保留或移除图案化硬掩模。值得注意的是,形成于主动区域302内的鳍片结构即为主动鳍片340,且主动鳍片340如图9所示,沿一第一方向d1延伸。更值得注意的是,形成于周边区域304内的鳍片结构可作为finfet元件甚或主动区域302的保护结构,且这些鳍片结构随着框状的轴心图案310a而成为保护鳍片框342。如图9所示,保护鳍片框342环绕且密封主动区域302,且各保护鳍片框342呈同心(concentric)排列。另外,保护鳍片框342与主动鳍片340实体上与电性上分离以避免影响主动区域302内主动鳍片140的特性以及元件的实际电性表现。接下来,可进行主动区域302内各组成元件的制作。

[0049]

请参阅图10,图10为本优选实施例的一变化型的示意图。根据本变化型,在制作主

动区域302内各组成元件的同时,也可于周边区域304内的保护鳍片框342上更设置多个条状强化结构350。如图10所示,本变化型中,可在主动区域302内形成栅极层360的同时,在周边区域304内的保护鳍片框342上形成强化结构350,故强化结构350可包含半导体材料如多晶硅。另外,熟悉该项技术的人士应知,主动区域302内栅极层360与主动鳍片340的关系仅为例示,栅极层360可依产品需求跨过较多或较少的主动鳍片340,且不同的栅极层360可跨越不同的主动鳍片340。或者,在本变化型中,可在主动区域302内形成金属栅极、接触插塞或长形接触窗360时,同时在周边区域304内的保护鳍片框342上形成强化结构350,故强化结构350可包含金属材料。同理,金属栅极、接触插塞或长形接触窗360与主动鳍片340的关系也可依产品需求而不同于图10所示者。值得注意的是,强化结构350如图10所示,垂直于保护鳍片框342的任一部分,并且将周边区域304内的同心设置的所有保护鳍片框342全部电连接在一起,并更强化保护鳍片框342的结构强度,以提供主动鳍片340更好的保护。另外,在进行后续主动区域302内的金属内连线制作工艺时,更可同时于周边区域204内的强化结构350上方形成与其实体以及电连接的金属层(但与主动区域202内的金属内连线以及主动鳍片电性隔离),以更强化保护鳍片框342的结构强度。

[0050]

根据本优选实施例及其变化型所提供的半导体整合装置,在主动区域302内设置用以建构半导体元件的主动鳍片340,同时于主动区域302外设置环绕且密封主动区域302的保护鳍片框342以及强化结构350。通过保护鳍片框342与强化结构350的设置,可作为提供电性隔离的保护环或提供应力隔离的密封环,以避免主动区域302内纤长的主动鳍片340受到物理性或电性的外力影响。另外如前所述,由于保护鳍片框342与主动鳍片340同时形成,而强化结构350可与其他元件如栅极层或接触插塞的金属层等同时形成,故本优选实施例可于不增加制作工艺复杂度的前提下,成功地提供主动鳍片340需要的保护结构。

[0051]

请参阅图11,图11为本发明所提供的一种半导体整合装置的第四优选实施例的示意图。首先需注意的是,第四优选实施例中,保护结构的制作步骤与第三优选实施例相同,故该等制作步骤此后不再绘示。如图11所示,本优选实施例提供一基底400,例如一soi基底或块硅基底。基底400上定义有一主动区域402与一环绕主动区域402的周边区域404。如前所述,虽然本优选实施例中,周边区域404环绕主动区域402,但周边区域404与主动区域402的相对关系可根据不同的产品需求而变化,故不限于此。此外,基底400上形成一硬掩模层(图未示)。接下来,在硬掩模层上形成多个轴心图案(图未示)。值得注意的是,在本优选实施例中,设置于主动区域402内的轴心图案与设置于周边区域404内的轴心图案的形态并不相同。本优选实施例与第三优选实施例相同,在主动区域402内的轴心图案可根据实际产品需要形成于主动区域402内;但周边区域404内的轴心图案却是以环绕并且密封主动区域402的框状设置于周边区域404内。

[0052]

请继续参阅图11。在基底400上形成轴心图案之后,在各轴心图案的侧壁形成多个间隙壁图案(图未示)。并且在形成间隙壁图案之后,进行一蚀刻制作工艺,移除轴心图案。值得注意的是,本优选实施例可在此蚀刻制作工艺之前、之中或之后,移除部分的间隙壁图案,尤其是主动区域402内轴心图案头尾两端的间隙壁图案,以及周边区域402内至少一间隙壁图案的部分。随后利用间隙壁图案作为掩模图案化硬掩模层,以定义出鳍片结构的位置与大小。再以图案化硬掩模作为一蚀刻掩模蚀刻基底400,而于基底400上形成多个鳍片结构。而在形成鳍片结构之后,可依产品所需保留或移除图案化硬掩模。

[0053]

值得注意的是,形成于主动区域402内的鳍片结构即为主动鳍片440,且主动鳍片440如图11所示,沿一第一方向d1延伸。更值得注意的是,形成于周边区域404内的鳍片结构可作为finfet元件甚或主动区域402的保护结构,且这些鳍片结构随着框状的轴心图案而成为保护鳍片框442。如图11所示,保护鳍片框442环绕主动区域402,且各保护鳍片框442呈同心(concentric)排列。另外,保护鳍片框442与主动鳍片440实体分离,以避免影响主动区域402内,以避免影响到主动鳍片440的特性以及元件的实际电性表现。更重要的是,本优选实施例中,除了最内圈的保护鳍片框442a之外,其他的保护鳍片框442还包含多个空隙444,形成于保护鳍片框442内,且切断保护鳍片框442。如图11所示,各空隙444对应相邻的保护鳍片框442的侧壁,而形成一迷宫图案。随后,可进行主动区域402内各组成元件的制作。

[0054]

请参阅图12,图12为本优选实施例的一变化型的示意图。根据本变化型,在制作主动区域402内各组成元件的同时,也可于周边区域404内的保护鳍片框442内更设置多个强化结构450。如图12所示,本变化型中,可在主动区域402内形成栅极层460的同时,在周边区域404内的保护鳍片框442内形成多个强化结构450,故强化结构450可包含半导体材料如多晶硅。另外,熟悉该项技术的人士应知,主动区域402内栅极层460与主动鳍片440的关系仅为例示,栅极层460可依产品需求跨过较多或较少的主动鳍片440,且不同的栅极层460可跨越不同的主动鳍片440。或者,在本变化型中,可在主动区域402内形成金属栅极、接触插塞或长形接触窗460时,同时于周边区域404内的保护鳍片框442内形成多个强化结构450,故强化结构450可包含金属材料。同理,金属栅极、接触插塞或长形接触窗460与主动鳍片440的关系也可依产品需求而不同于图12所示者。值得注意的是,强化结构450如图12所示,填满各保护鳍片框442的空隙444。另外强化结构450也可在填满空隙444的同时将周边区域404内的同心设置的各保护鳍片框442实体上与电性上全部电连接在一起,并更强化保护鳍片框442的结构强度,以提供主动鳍片440更好的保护。在进行主动区域402内金属内连线制作工艺时,更可同时于周边区域404内的强化结构450上方形成与其实体以及电连接的金属层(但与主动区域402内的金属内连线以及主动鳍片电性隔离),以更强化保护鳍片框442的结构强度。

[0055]

根据本优选实施例发明所提供的半导体整合装置,在主动区域402内设置用以建构半导体元件的主动鳍片440,同时于主动区域402外设置环绕主动区域402的保护鳍片框442以及强化结构450。通过保护鳍片框442与强化结构450的设置,可作为提供电性隔离的保护环或提供应力隔离的密封环,以避免主动区域402内纤长的主动鳍片440受到物理性或电性的外力影响。另外如前所述,由于保护鳍片框442与主动鳍片440同时形成,而强化结构450可与其他元件如栅极层或接触插塞的金属层等同时形成,故本优选实施例可于不增加制作工艺复杂度的前提下,成功地提供主动鳍片440需要的保护结构。

[0056]

根据本发明所提供的半导体整合装置,在主动区域内设置用以建构半导体元件的主动鳍片,同时于主动区域外设置环绕主动区域的保护鳍片或该等保护鳍片框,作为提供电性隔离的保护环或提供应力隔离的密封环。换句话说,通过保护鳍片与保护鳍片框的设置,可避免主动区域内纤长的主动鳍片以及具有实际功能的元件受到物理性或电性的外力影响。

[0057]

以上所述仅为本发明的优选实施例,凡依本发明权利要求所做的均等变化与修饰,都应属本发明的涵盖范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1