高速DreaMOS器件及其制作方法与流程

高速dreamos器件及其制作方法

技术领域

1.本发明涉及一种功率半导体器件,特别涉及一种高速dreamos器件及其制作方法,属于半导体技术领域。

背景技术:

2.图1示出了一种ldmos器件的结构,其中源区13、漏区延伸区14和漏区15的导电类型相同,栅极11下方的沟道区域的导电类型和体区相同、与源区13相反,漏区延伸区14提高了ldmos器件的击穿电压,从而提高器件的输出功率,在ldmos器件的制作工艺中,通过离子注入方式形成图1中的阱区17区域,并通过长时间的高温退火,以使体区横向扩散并与漏区延伸区14接触,从而形成器件的沟道。

3.然而,长时间的高温退火,增加了器件的热过程,降低了器件的一致性,同时导致器件的结深变深,进而增加了器件电容。如图1所示的ldmos器件,在高压大电流场景下容易产生热载流子注入效应,载流子进入到栅氧化层区域,会加剧器件导通电阻、饱和电流、阈值电压和击穿电压等参数的变化,降低器件的使用寿命;并且,随着漏区延伸区掺杂浓度增加,热载流子效应加剧。为了提高器件的效率,本领域技术人员希望增加漏区延伸区的掺杂浓度,传统的ldmos器件受困于热载流子注入效应,无法降低导通电阻,提高器件性能。

4.图2示出了一种dreamos器件的结构,该器件结构打破了热载流子注入效应可靠性的极限,相比传统的ldmos器件,该dreamos器件的导通电阻降低了40%,电流密度是传统ldmos器件的2.1倍,但与传统ldmos器件相比,dreamos器件在截止频率等性能上的优势并不是特别明显,而且电流密度也不能满足更高频率应用的需求。

5.综上,现有器件还存在诸如加工工艺热过程多、器件一致性差、器件结深不易控制且电容大,以及,现有器件受限于热载流子注入效应,无法降低导通电阻、提高器件效率和电流密度等缺陷。

技术实现要素:

6.本发明的主要目的在于提供一种高速dreamos器件及其制作方法,以克服现有技术中的不足。

7.为实现前述发明目的,本发明采用的技术方案包括:

8.本发明实施例提供了一种高速dreamos器件,包括半导体结构层和与半导体结构层配合的栅氧化层、栅极,所述半导体结构层包括外延层和形成在所述外延层内的阱区、阱区接触区、漏区延伸区及漏区,所述外延层内还形成有多个源区和多个沟道掺杂区,其中,所述多个沟道掺杂区分别形成在所述外延层的不同深度区域,其中至少两个源区具有不同的结深。

9.本发明实施例还提供了所述高速dreamos器件的制作方法,其包括:在制作形成栅极之前,采用离子注入方式在外延层内加工形成阱区,对所述外延层进行多次离子注入,以在所述外延层内的不同深度区域形成多个沟道掺杂区,以及,在制作形成栅极之后,采用离

子注入方式在所述外延层内形成多个源区。

10.与现有技术相比,本发明的优点包括:

11.1)本发明实施例提供的高速dreamos器件,减少了阱区的高温退火过程,简化了器件制作工艺,提高了器件一致性;

12.2)本发明实施例提供的高速dreamos器件的导通电阻降低了40%,电流密度是传统ldmos器件的2.1倍;在相同的击穿电压下,本发明实施例提供的高速dreamos器件的截止频率提高了2.5倍,功率密度提高了60%。

附图说明

13.图1是本发明人提供的一种现有功率ldmos器件的横截面示意图;

14.图2是本发明人提供的一种dreamos器件的横截面示意图;

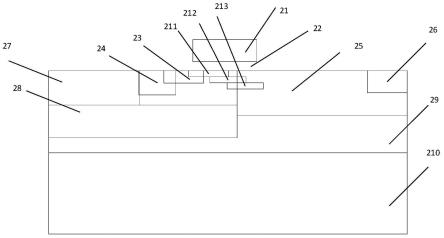

15.图3是本发明一典型实施案例中提供的一种高速dreamos器件的横截面示意图;

16.图4a-图f分别是本发明一典型实施案例中提供的一种高速dreamos器件的制作方法中各个工艺步骤后形成的器件结构示意图;

17.附图标记说明:11-栅极、12-栅氧化层、13-源区、14-漏区延伸区、15-漏区,16-阱区接触区、17-阱区、18-外延层、19-衬底、21-栅极、22-栅氧化层、23-第一源区、24-第二源区、25-漏区延伸区、26-漏区、27-阱区接触区、28-阱区、29-外延层、210-衬底、211-第一沟道掺杂区、212-第二沟道掺杂区、213-第三沟道掺杂区、31-栅极、32-栅氧化层、33-源区、34-漏区延伸区、35-漏区、36-阱区接触区、37-阱区、38-外延层、39-衬底、310-沟道掺杂区。

具体实施方式

18.鉴于现有技术中的不足,本案发明人经长期研究和大量实践,得以提出本发明的技术方案。如下将对该技术方案、其实施过程及原理等作进一步的解释说明。

19.ldmos:lateral double diffusion metal oxide semiconductor,横向双扩散金属氧化物半导体;

20.dreamos:drain extended advance metal oxide semiconductor,漏延伸的先进金属氧化物半导体。

21.针对漏极延伸的半导体金属氧化物晶体管器件所面临的热载流子注入效应约束器件导通电阻降低和电流密度提升问题,本发明实施例提供的一种高速dreamos器件采用了双沟道设计,有效抑制了热载流子注入效应,提高了漏区延伸区的掺杂浓度,将器件的电流密度提高至传统器件的2.1倍,导通电阻降低了40%。

22.本发明实施例提供的一种高速dreamos器件,通过离子注入方式形成阱区,减少了加工的热过程,简化了制作工艺,提高了器件一致性;并且,本发明实施例提供的一种高速dreamos器件,结合栅长缩短和设置多个源区提高器件截止频率,以及,本发明实施例提供的一种高速dreamos器件,在制作栅极之前,通过进行多次沟道掺杂形成多个沟道掺杂区,多个沟道掺杂区结合阱区,抑制了热载流子注入效应,在相同的热载流子注入寿命条件下,本发明实施例提供的一种高速dreamos器件的电流密度是dreamos器件的2.5倍,电流密度提高了60%。

23.本发明实施例提供了一种高速dreamos器件,包括半导体结构层和与半导体结构

层配合的栅氧化层、栅极,所述半导体结构层包括外延层和形成在所述外延层内的阱区、阱区接触区、漏区延伸区及漏区,所述外延层内还形成有多个源区和多个沟道掺杂区,其中,所述多个沟道掺杂区分别形成在所述外延层的不同深度区域,其中至少两个源区具有不同的结深。

24.进一步的,所述多个沟道掺杂区沿所述外延层的深度方向依次叠层设置,且所述多个沟道掺杂区沿自身长度方向错开。

25.进一步的,相邻两个沟道掺杂区的重叠区域长度为所述沟道掺杂区长度的1/3-1/6。

26.进一步的,所述沟道掺杂区的厚度为0.4-1μm,长度为0.1-0.8μm。

27.进一步的,所述多个沟道掺杂区位于所述栅极下方,多个源区沿指定方向依次分布在所述阱区延伸区和沟道掺杂区之间,其中至少一个源区与所述阱区延伸区连接,至少一个源区与沟道掺杂区连接,且,至少与所述阱区延伸区连接的源区的结深大于与沟道掺杂区连接的源区的结深。

28.进一步的,所述多个源区的结深沿靠近或趋向沟道掺杂区或栅极的方向依次减小。

29.进一步的,所述多个源区之间依次连接。

30.进一步的,所述源区的厚度为100-4000nm,长度为500-4000nm,其中两个源区之间的结深差值为50n-2000nm。

31.进一步的,位于最顶层的沟道掺杂区与所述源区连接,其中,所述沟道掺杂区、源区、漏区以及漏区延伸区的导电类型相同。

32.进一步的,所述阱区位于所述多个沟道掺杂区的下方,且所述阱区分别与所述阱区接触区、漏区延伸区连接,其中,所述阱区、阱区延伸区、外延层的导电类型相同。

33.进一步的,当栅极电压与阈值电压具有第一压差时,器件的有效沟道和载流子路径均位于所述半导体结构层内部,而当所述栅极电压大于所述阈值电压,且所述栅极电压与所述阈值电压具有第二压差时,器件的有效沟道位于所述半导体结构层表面。

34.进一步的,当栅极电压位于阈值电压附近时,器件的有效沟道位于所述多个沟道掺杂区和阱区之间。

35.进一步的,所述外延层设置在衬底上,所述衬底与外延层的导电类型相同。

36.进一步的,所述栅极的长度为50-250nm。

37.本发明实施例还提供了所述高速dreamos器件的制作方法,其包括:在制作形成栅极之前,采用离子注入方式在外延层内加工形成阱区,对所述外延层进行多次离子注入,以在所述外延层内的不同深度区域形成多个沟道掺杂区,以及,在制作形成栅极之后,采用离子注入方式在所述外延层内形成多个源区。

38.进一步的,所述的制作方法具体包括:

39.提供外延层,并采用离子注入方式在所述外延层内加工形成阱区,离子注入的能量为100-800kev,浓度为5e12-5e14cm-2

;

40.采用离子注入方式对所述外延层进行多次注入形成多个沟道掺杂区,离子注入的能量为15-250kev,浓度为1e11~5e12 cm-2

;

41.在所述外延层上形成栅氧化层并在所述栅氧化层上形成栅极;

42.采用离子注入方式在所述外延层内加工形成漏区延伸区,离子注入的能量为50-600kev,浓度范围是2e11-5e12cm-2

;

43.采用离子注入方式在所述外延层内加工形成多个源区,离子注入的能量为10-100kev,浓度为5e13~1e16 cm-2

;

44.采用离子注入方式在所述外延层内加工形成阱区接触区和漏区。

45.如下将结合附图对该技术方案、其实施过程及原理等作进一步的解释说明,如非特别说明,本发明实施例所采用的制作工艺和检测工艺均是本领域技术人员已知的。

46.实施例1

47.请参阅图3,一种高速dreamos器件,其包括半导体结构层和与半导体结构层配合的栅氧化层22、栅极21,所述半导体结构层包括衬底210、设置在衬底上的外延层29和形成在所述外延层19内的阱区28、阱区接触区27、第一源区23、第二源区24、漏区延伸区25、漏区26及多个沟道掺杂区;

48.所述多个沟道掺杂区位于所述栅极21下方,所述阱区28位于所述多个沟道掺杂区的下方,且所述阱区28分别与所述阱区接触区27、漏区延伸区25连接,所述多个沟道掺杂区包括沿外延层29的深度方向依次形成在所述外延层29内不同深度区域的第一沟道掺杂区211、第二沟道掺杂区212、第三沟道掺杂区213,所述第一源区23位于所述第二源区24靠近栅极21的一侧,所述第一源区23与所述第二源区24、第一沟道掺杂区211连接,且所述第二源区24的结深大于所述第一源区23的结深;

49.其中,所述第一沟道掺杂区211、第二沟道掺杂区212、第三沟道掺杂区213、第一源区23、第二源区24、漏区延伸区25、漏区26的导电类型相同,所述阱区28、阱区延伸区27、外延层29以及衬底210的导电类型相同。

50.当栅极电压略高于阈值电压时,所述高速dreamos器件的有效沟道位于半导体结构层内部,并远离半导体结构层表面,电流路径也远离半导体结构层表面,在最容易发生热载流子注入效应的栅压条件下,降低了热载流子注入发生的概率;

51.而当栅极电压进一步提升以后,所述高速dreamos器件的有效沟道和传统ldmos器件一样,位于半导体结构层表面,如此保证了高速dreamos器件在栅极电压较高时的跨导和器件性能。

52.具体的,本发明实施提供的一种高速dreamos器件为双沟道器件结构,当栅极电压略大于阈值电压时,栅极和沟道之间的电势差小于传统器件栅极和沟道之间的电势差,形成电子的势垒阻挡热电子进入氧化层,从而降低了器件发生热载流子注入效应的概率,使得器件的电流密度得以大幅度提升。

53.请参阅图3和图4a-图4f,一种高速dreamos器件的制作方法,包括如下过程:

54.1)在衬底210上生长外延层29,外延层29的厚度根据器件指标设定,厚度一般位于2-50μm之间;

55.2)采用离子注入工艺在外延层29内形成阱区28,离子注入的能量为100-800kev,浓度为5e12-5e14cm-2

,其中,阱区28的导电类型和外延层29相同;

56.3)通过离子注入工艺,采用多层光罩进行多次离子注入以在外延层29内形成多个沟道掺杂区,本发明实施例采用3层光罩进行3次离子注入,以在外延层29内形成叠层设置且依次连接的第一沟道掺杂区211、第二沟道掺杂区212、第三沟道掺杂区213,每次离子注

入的厚度为0.4-1μm,每层光罩重叠部分是注入区域长度的1/3-1/6,离子注入的能量为15kev-250kev,浓度为1e11-5e12 cm-2

,其中,第一沟道掺杂区211、第二沟道掺杂区212、第三沟道掺杂区213的导电类型和外延层28相反;

57.4)在外延层29的顶部表面淀积栅氧化层22,并在栅氧化层22上方淀积多晶硅栅,并刻蚀形成栅极21,其中,栅氧化层22的厚度为5-30nm,栅极21的长度和器件参数条件相关,例如,栅极21的长度为0.05-4μm,优选为50-250nm;

58.5)采用离子注入工艺在外延层29内形成漏极延伸区25,离子注入的能量为50kev-600kev,浓度为2e11-5e12 cm-2

;

59.6)采用离子注入工艺在外延层29内形成第一源区23,并使所述第一源区23与第一沟道掺杂区211连接,其中,第一源区的厚度为100-4000nm,长度为500-4000nm,离子注入的能量为10kev-100kev,浓度为5e13-1e16 cm-2

;

60.然后,在外延层29内形成多晶硅栅的侧墙,借助侧墙进行离子注入以形成第二源区24,并使所述第二源区24与所述第一源区23、阱区接触区27连接,第二源区24的结深大于第一源区23的结深,其中,所述第二源区的厚度为100-4000nm,长度为500-4000nm,离子注入的能量为10kev-100kev,浓度为5e13-1e16 cm-2

,所述第二源区24与第一源区23的结深差值为50n-2000nm,第一源区23和第二源区24的导电类型和衬底相反;

61.7)通过离子注入工艺形成器件的阱区接触区27和漏区26,其中阱区接触区27的导电类型和阱区28相同,漏区延伸区25、漏区26和第一源区23、第二源区24的导电类型相同。

62.具体的,当过栅极电压(或者称之为驱动电压,下同)和阈值电压的差值小于栅极电压的三分之一时,器件的有效沟道位于多个沟道掺杂区和阱区之间,并主要位于多个沟道掺杂区下方,此时,电流路径位于半导体结构层内部,进而远离半导体结构层表面,尤其是远离漏区延伸区和阱区的交接处最容易发生热载流子注入效应的区域;多个沟道掺杂区使载流子路径远离半导体结构层表面,从而降低了器件发生热载流子注入效应的概率;而当栅极电压和阈值电压的差值大于栅极电压的三分之一时,器件的有效沟道位于半导体结构层表面,由于热载流子注入效应得到了改善,可以对漏区延伸区采用浓度更高的掺杂,从而降低了器件的导通电阻,提高了电流密度。

63.通过对本发明实施例提供的高速dreamos器件以及如图1、图2的现有器件进行仿真测试,根据器件仿真测试结果显示,在相同的热载流子效应寿命条件下,本发明实施例提供的高速dreamos器件的电流密度比图2中的dreamos器件提高了60%。

64.另外,直接采用离子注入方式加工形成阱区,较之传统ldmos器件制作工艺中在离子注入以后长时间的高温退火过程,本发明减少了在芯片加工的热过程,提高了器件的一致性,能够更好的控制器件的结深,更重要的是,本发明通过设置多个源区和多个沟道掺杂区,有利于减小栅极尺寸,进而实现缩短栅长目的,同时,本发明还形成了多个源区,其中,与沟道掺杂区连接的第一源区的浅结结构提高了器件的截止频率,测试结果显示,本发明实施例提供的高速dreamos器件的截止频率是现有dreamos器件(如图2)的2.5倍。

65.本发明实施例提供的高速dreamos器件,相比传统ldmos器件,减少了阱区的高温退火过程,简化了器件制作工艺,提高了器件一致性;较之传统ldmos器件,本发明实施例提供的高速dreamos器件的导通电阻降低了40%,电流密度是传统ldmos器件的2.1倍;较之现有dreamos器件,在相同的击穿电压下,本发明实施例提供的高速dreamos器件的截止频率

提高了2.5倍,功率密度提高了60%。

66.应当理解,上述实施例仅为说明本发明的技术构思及特点,其目的在于让熟悉此项技术的人士能够了解本发明的内容并据以实施,并不能以此限制本发明的保护范围。凡根据本发明精神实质所作的等效变化或修饰,都应涵盖在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1