一种着陆焊盘和DRAM的形成方法与流程

一种着陆焊盘和dram的形成方法

技术领域

1.本发明涉及半导体技术领域,尤其涉及一种着陆焊盘和dram的形成方法。

背景技术:

2.存储器是数字系统中用以存储大量信息的设备或部件,是计算机和数字设备中的重要组成部分。存储器可分为随机存取存储器(ram)和只读存储器(rom)两大类。ram包括dram、pram、mram等,晶体管和电容器是制造这些ram的关键部件。

3.着陆焊盘(lp,landing pad)工艺是电容器形成过程的一部分。优化现有的着陆焊盘(landing pad)工艺以改善由于现有dram器件越来越小而导致的设计裕度不足。在目前dram设计上,将电容器(sn,存储节点)与浅沟槽隔离件(sti)间的连接端子直接连接在snc(存储节点接触件)上具有空间不足的缺陷。所以为了连接sn与snc需要焊盘,形成该焊盘的工艺称作snc2或lp。目前的lp工艺非常复杂,最后阶段则是acp工艺,其中,acp工艺也包含很多工艺步骤。

技术实现要素:

4.鉴于上述的分析,本发明实施例旨在提供一种着陆焊盘和dram的形成方法,用以解决现有连接sn与snc的着陆焊盘形成工艺复杂、消耗时间长、成本高的问题。

5.一方面,本发明实施例提供了一种着陆焊盘的形成方法,包括:提供半导体衬底,所述半导体衬底上形成有位线结构和位于相邻位线结构之间的存储节点接触部;在所述位线结构上方顺序形成阻挡金属层、着陆焊盘层、底部掩模层和焊盘图案掩模层;通过蚀刻工艺将所述焊盘图案掩模层形成为焊盘图案掩模,其中,所述焊盘图案掩模包括多个第一凸起和位于所述多个第一凸起中的任意两个相邻第一凸起之间的第一开口,其中,所述多个第一凸起与待形成的着陆焊盘相对应;在多个第一开口中继续向下蚀刻所述底部掩模层、所述着陆焊盘层和所述阻挡金属层,以暴露所述位线结构的顶面;以及去除剩余的所述多个第一凸起和所述底部掩模层以形成着陆焊盘。

6.上述技术方案的有益效果如下:将acp(array close photo)光刻转换为acp蚀刻工艺,省略了焊盘图案掩模层的回蚀刻和清洁工艺和侧壁清洁工艺等,从而简化了连接sn与snc的着陆焊盘形成工艺。

7.基于上述方法的进一步改进,在相同的工艺室中对所述阻挡金属层、所述着陆焊盘层、所述底部掩模层和所述焊盘图案掩模层实施原位蚀刻工艺。

8.基于上述方法的进一步改进,所述位线结构的形成方法包括:在半导体衬底上方顺序形成氮化物层、阻挡层、金属层和盖层;对所述盖层、所述金属层、所述阻挡层和所述氮化物层进行顺序蚀刻以形成多条位线;在所述多条位线上方沉积绝缘材料层;将所述绝缘材料层蚀刻为位于所述多条位线的相对侧壁上的位线侧墙以形成所述位线结构,其中,所述位线结构包括所述多条位线和所述位线侧墙。

9.基于上述方法的进一步改进,在形成所述阻挡层之前还包括:在所述多个位线结

构之间形成绝缘材料层;以及将所述绝缘材料层形成为sti,以通过所述sti将所述多个位线结构间隔开。

10.基于上述方法的进一步改进,所述底部掩模层包括非晶碳硬掩模层和位于所述非晶碳硬掩模层上方的氮氧化硅掩模层。

11.基于上述方法的进一步改进,形成焊盘图案掩模层进一步包括:在所述氮氧化硅掩模层上方形成第一旋涂硬掩模层;将所述第一旋涂硬掩模层形成为多个第二凸起,其中,所述多个第二凸起在垂直方向上与待形成的多个着陆焊盘相对应;在所述多个第二凸起的侧壁上沉积氧化物层;以及在所述氧化物层上方形成具有流动性的第二旋涂硬掩模层以自动填充所述氧化物层中的缝隙。

12.基于上述方法的进一步改进,通过蚀刻工艺将所述焊盘图案掩模层形成为焊盘图案掩模进一步包括:通过第一蚀刻工艺蚀刻所述第二旋涂硬掩模层并过蚀刻所述第二旋涂硬掩模层下面的所述氧化物层;通过第二蚀刻工艺蚀刻暴露的所述氧化物层并过蚀刻所述氧化物层下面的所述第一旋涂硬掩模层,而保持未暴露的所述氧化物层未被蚀刻,以形成所述多个第一开口和位于每个第一开口相对侧的所述多个第一凸起,其中,所述第一凸起包括所述第一旋涂硬掩模层和氧化物掩模的组合,或者所述第一旋涂硬掩模层。

13.基于上述方法的进一步改进,在所述第一蚀刻工艺中,大气压力为4mtorr至6mtorr,射频功率为440w,偏置射频电压为400v,工艺时间为48s至72s,过蚀刻为16%至24%,o2为32sccm至48sccm,ar为120sccm至180sccm。

14.基于上述方法的进一步改进,在所述第二蚀刻工艺中,大气压力为8mtorr至12mtorr,射频功率为550w,偏置射频电压为100v,工艺时间为18.4s至27.6s,过蚀刻为24%至36%,cf4为80sccm至120sccm。

15.基于上述方法的进一步改进,在多个第一开口中向下蚀刻所述底部掩模层进一步包括:在多个第一开口中继续向下蚀刻所述氮氧化硅掩模层;以及在多个第一开口中继续向下蚀刻所述非晶碳硬掩模层。

16.基于上述方法的进一步改进,在所述氮氧化硅掩模层的蚀刻过程中,大气压力为4mtorr至6mtorr,射频功率为400w,偏置射频电压为600v,工艺时间为44.8s至67.2s,过蚀刻时间为4.8s至7.2s,o2为4sccm至6sccm,ar为120sccm至180sccm、c4f8为5.6sccm至8.4sccm以及c4f6为6.4sccm至9.6sccm。

17.基于上述方法的进一步改进,在所述非晶碳硬掩模层的蚀刻过程中,大气压力为4mtorr至6mtorr,射频功率为440w,偏置射频电压为300v,工艺时间为40s至60s,过蚀刻时间为8s至12s,过蚀刻为16%至24%,o2为32sccm至48sccm,n2为64sccm至96sccm,ar为120sccm至180sccm以及cf4为12sccm至18sccm。

18.基于上述方法的进一步改进,在所述着陆焊盘层的蚀刻过程中,大气压力为24mtorr至36mtorr,射频功率为1150w,过蚀刻射频功率为600w,偏置射频电压为300v,过蚀刻偏置射频电压为100v,工艺时间为18.4s至27.6s,过蚀刻时间为4.8s至7.2s,o2为40sccm至60sccm,sf6为320sccm至480sccm,过蚀刻sf6为128sccm至192sccm,以及ar为72sccm至108sccm。

19.基于上述方法的进一步改进,在所述阻挡金属层的蚀刻过程中,大气压力为5.6mtorr至8.4mtorr,射频功率为400w,偏置射频电压100v,工艺时间为11.2s至16.8s,过

蚀刻时间为7.2s至10.8s,cl2为22.4sccm至33.6sccm,过蚀刻cl2为19.2sccm至28.8sccm,ar为128sccm至192sccm以及过蚀刻ar为136sccm至204sccm。

20.基于上述方法的进一步改进,着陆焊盘的形成方法进一步包括:通过干清洁工艺去除工艺室中的残留物。

21.基于上述方法的进一步改进,所述残留物包括:tin颗粒、w颗粒、c,f,cfx聚合物、c,f,sixfy聚合物和涂层。

22.基于上述方法的进一步改进,通过cl2去除所述工艺室中的tin颗粒;通过sf6去除所述工艺室中的w颗粒;通过nf3去除所述工艺室中的c,f,cfx聚合物;通过o2去除所述工艺室中的c,f,sixfy聚合物;以及通过sicl4去除所述工艺室中的涂层。

23.另一方面,本发明实施例提供了一种dram的形成方法,包括:使用以上所述的着陆焊盘的形成方法形成着陆焊盘,其中,所述着陆焊盘用于连接存储节点和sti。

24.与现有技术相比,本发明至少可实现如下有益效果之一:

25.1、将acp(array close photo)光刻转换为acp蚀刻工艺,省略了焊盘图案掩模层的回蚀刻和清洁工艺和侧壁清洁工艺等,从而简化了连接sn与snc的着陆焊盘形成工艺。

26.2、在相同的工艺室中对阻挡金属层、着陆焊盘层、底部掩模层和焊盘图案掩模层实施原位蚀刻工艺,避免在不同工艺室中实施6个不同工艺步骤,例如,图案掩模层回蚀刻工艺、图案掩模层清洁工艺、侧壁清洁工艺、掩模蚀刻工艺、钨蚀刻工艺和阻挡金属蚀刻工艺,节省了不同工艺室中转移时间和器件装卸时间,仅使用单个工艺室,大幅度缩短了工艺时间,降低了工艺成本。

27.3、工艺室在蚀刻期间会形成很多聚合物,在形成着陆焊盘之后,将多种蚀刻气体提供给工艺室以去除这些聚合物,以能够维持工艺室干净。

28.本发明中,上述各技术方案之间还可以相互组合,以实现更多的优选组合方案。本发明的其他特征和优点将在随后的说明书中阐述,并且,部分优点可从说明书中变得显而易见,或者通过实施本发明而了解。本发明的目的和其他优点可通过说明书以及附图中所特别指出的内容中来实现和获得。

附图说明

29.附图仅用于示出具体实施例的目的,而并不认为是对本发明的限制,在整个附图中,相同的参考符号表示相同的部件。

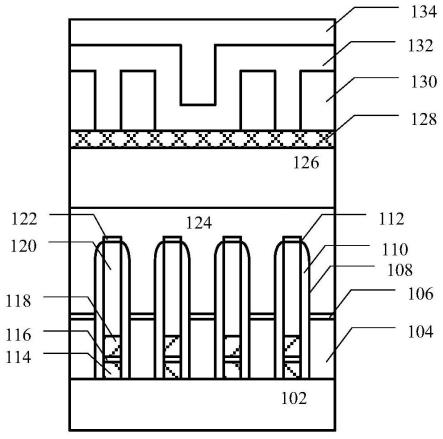

30.图1为根据本发明实施例的着陆焊盘的形成方法的中间阶段的截面图。

31.图2为根据本发明实施例的着陆焊盘的形成方法的中间阶段的截面图。

32.图3为根据本发明实施例的着陆焊盘的形成方法已形成着陆焊盘的截面图。

33.图4为根据本发明实施例的着陆焊盘的形成方法的蚀刻过程中具体参数设置的图表。

34.图5为根据本发明实施例的干清洁工艺中的具体参数设置的图表。

具体实施方式

35.以下,将参照附图来描述本公开的实施例。但是应该理解,这些描述只是示例性的,而并非要限制本公开的范围。此外,在以下说明中,省略了对公知结构和技术的描述,以

避免不必要地混淆本公开的概念。在附图中示出了根据本公开实施例的各种结构示意图。这些图并非是按比例绘制的,其中为了清楚表达的目的,放大了某些细节,并且可能省略了某些细节。图中所示出的各种区域、层的形状以及它们之间的相对大小、位置关系仅是示例性的,实际中可能由于制造公差或技术限制而有所偏差,并且本领域技术人员根据实际所需可以另外设计具有不同形状、大小、相对位置的区域/层。

36.在本公开的上下文中,当将一层/元件称作位于另一层/元件“上”时,该层/元件可以直接位于该另一层/元件上,或者它们之间可以存在居中层/元件。另外,如果在一种朝向中一层/元件位于另一层/元件“上”,那么当调转朝向时,该层/元件可以位于该另一层/元件“下”。

37.本发明的一个具体实施例,公开了一种着陆焊盘的形成方法。下文中,将参考图1,对着陆焊盘的形成方法进行详细描述。

38.参考图1,提供半导体衬底102。

39.半导体衬底102上形成有位线结构108和位于相邻位线结构108之间的存储节点接触部。具体地,形成位线结构108可以包括在半导体衬底102上方顺序地形成氮化物层114、阻挡层116、金属层118和盖层120。然后,自上而下对盖层120、金属层118、阻挡层116和氮化物层114进行顺序蚀刻,以形成多条位线112,其中,每条位线112自下而上包括位线氮化物层114、位线阻挡层116、位线金属层118和位线盖层120。最后,在多条位线上方沉积绝缘材料层;将绝缘材料层蚀刻为位于多条位线112的相对侧壁上的位线侧墙110以形成位线结构108,其中,位线结构108包括多条位线112和位线侧墙110。在一个实施例中,位线侧墙110可以采用氮化物-氧化物-氮化物(n-o-n)结构。

40.参考图1,在半导体衬底102上方形成位线结构108之后,在半导体衬底102上方形成sti 104。具体地,在多个位线结构108之间形成绝缘材料层。然后通过蚀刻处理将绝缘材料层形成为sti 104,以通过sti 104将多个位线结构108间隔开。sti 104的顶面可以位于位线盖层120的顶面和底面之间。在可选实施例中,sti 104的顶面位于位线结构108的1/2高度处。

41.参考图1,在半导体衬底102上方形成sti 104之后,在位线结构108和sti 104上方自下而上顺序形成阻挡金属层122和106、着陆焊盘层124、底部掩模层和焊盘图案掩模层。具体地,进一步包括在多条位线结构112和sti 104上方形成阻挡金属层122和106;在阻挡金属层122和106上方形成着陆焊盘层124;在着陆焊盘层124上方形成底部掩模层,其中,底部掩模层包括非晶碳硬掩模层126和位于非晶碳硬掩模层126上方的氮氧化硅掩模层128。参考图1,具体地,形成焊盘图案掩模层进一步包括:在氮氧化硅掩模层128上方形成第一旋涂硬掩模层(soh,spin-on hard mask);将第一旋涂硬掩模层形成为多个第二凸起130,其中,多个第二凸起130在垂直方向上与待形成的多个着陆焊盘相对应;在多个第二凸起130上方沉积氧化物层132,其中,氧化物材料的一部分填充相邻第二凸起130之间的沟槽而形成氧化物侧壁;以及在氧化物层132上方形成具有流动性的第二旋涂硬掩模层134以自动填充氧化物层中的缝隙。

42.参考图2,在位线结构108上方自下而上顺序形成阻挡金属层112和106、着陆焊盘层124、底部掩模层和焊盘图案掩模层之后,通过蚀刻工艺将焊盘图案掩模层形成为焊盘图案掩模,其中,焊盘图案掩模包括多个第一凸起136、138和位于多个第一凸起136、138中的

任意两个相邻第一凸起之间的第一开口140,其中,多个第一凸起136、138与待形成的着陆焊盘相对应。具体地,通过蚀刻工艺将焊盘图案掩模层形成为焊盘图案掩模进一步包括:通过第一蚀刻工艺蚀刻第二旋涂硬掩模层134并过蚀刻第二旋涂硬掩模层下面的氧化物层132。在第一蚀刻工艺中,大气压力为4mtorr至6mtorr,射频功率为440w,偏置射频电压为400v,工艺时间为48s至72s,过蚀刻为16%至24%,o2为32sccm至48sccm,ar为120sccm至180sccm。在优选实施例中,大气压力为5mtorr,射频功率为440w,偏置射频电压为400v,工艺时间为60s,过蚀刻为20%,o2为40sccm,ar为150sccm。通过第二蚀刻工艺蚀刻暴露的氧化物层132并过蚀刻氧化物层132下面的第一旋涂硬掩模层,而保持未暴露的氧化物层未被蚀刻,以形成多个第一开口140和位于每个第一开口140相对侧的多个第一凸起136、138,其中,第一凸起138包括第一旋涂硬掩模142和氧化物掩模144的组合,或者第一凸起136仅包括第一旋涂硬掩模。在第二蚀刻工艺中,大气压力为8mtorr至12mtorr,射频功率为550w,偏置射频电压为100v,工艺时间为18.4s至27.6s,过蚀刻为24%至36%,cf4为80sccm至120sccm。在优选实施例中,大气压力为10mtorr,射频功率为550w,偏置射频电压为100v,工艺时间为23s,过蚀刻为30%,cf4为100sccm。

43.参考图2,在多个第一开口140中继续向下蚀刻底部掩模层、着陆焊盘层124和阻挡金属层122,以暴露位线结构的顶面。在相同的工艺室中对阻挡金属层122、着陆焊盘层124、底部掩模层和焊盘图案掩模层实施原位蚀刻工艺。下文中,参考图2,将对底部掩模层、着陆焊盘层124和阻挡金属层122进行蚀刻工艺进行详细描述。

44.参考图2,在多个第一开口140中向下蚀刻底部掩模层,以将底部掩模层形成为底部掩模进一步包括:在多个第一开口140中继续向下蚀刻氮氧化硅掩模层128。在氮氧化硅掩模层的蚀刻过程中,大气压力为4mtorr至6mtorr,射频功率为400w,偏置射频电压为600v,工艺时间为44.8s至67.2s,过蚀刻时间为4.8s至7.2s,o2为4sccm至6sccm,ar为120sccm至180sccm、c4f8为5.6sccm至8.4sccm以及c4f6为6.4sccm至9.6sccm。在优选实施例中,大气压力为5mtorr,射频功率为400w,偏置射频电压为600v,工艺时间为56s,过蚀刻时间为6s,o2为5sccm,ar为150sccm、c4f8为7sccm以及c4f6为8sccm。然后,在多个第一开口140中继续向下蚀刻非晶碳(alc,amorphous carbon layer)硬掩模层128。在非晶碳硬掩模层的蚀刻过程中,大气压力为4mtorr至6mtorr,射频功率为440w,偏置射频电压为300v,工艺时间为40s至60s,过蚀刻时间为8s至12s,过蚀刻为16%至24%,o2为32sccm至48sccm,n2为64sccm至96sccm,ar为120sccm至180sccm以及cf4为12sccm至18sccm。在优选实施例中,大气压力为5mtorr,射频功率为440w,偏置射频电压为300v,工艺时间为50s,过蚀刻时间为10s,过蚀刻为20%,o2为40sccm,n2为80sccm,ar为150sccm以及cf4为15sccm。

45.再次参考图2,在着陆焊盘层的蚀刻过程中,大气压力为24mtorr至36mtorr,射频功率为1150w,过蚀刻射频功率为600w,偏置射频电压为300v,过蚀刻偏置射频电压为100v,工艺时间为18.4s至27.6s,过蚀刻时间为4.8s至7.2s,o2为40sccm至60sccm,sf6为320sccm至480sccm,过蚀刻sf6为128sccm至192sccm,以及ar为72sccm至108sccm。在优选实施例中,大气压力为30mtorr,射频功率为1150w,过蚀刻射频功率为600w,偏置射频电压为300v,过蚀刻偏置射频电压为100v,工艺时间为23s,过蚀刻时间为6s,o2为50sccm,sf6为400sccm,过蚀刻sf6为160sccm,以及ar为90sccm。在阻挡金属层的蚀刻过程中,大气压力为5.6mtorr至8.4mtorr,射频功率为400w,偏置射频电压100v,工艺时间为11.2s至16.8s,过蚀刻时间为

7.2s至10.8s,cl2为22.4sccm至33.6sccm,过蚀刻cl2为19.2sccm至28.8sccm,ar为128sccm至192sccm以及过蚀刻ar为136sccm至204sccm。在优选实施例中,大气压力为7mtorr,射频功率为400w,偏置射频电压100v,工艺时间为14s,过蚀刻时间为9s,cl2为28sccm,过蚀刻cl2为24sccm,ar为160sccm以及过蚀刻ar为170sccm。在优选实施例中,图4示出了具体参数设置。

46.参考图3,在多个第一开口140中继续向下蚀刻底部掩模层、着陆焊盘层和阻挡金属层之后,去除剩余的多个第一凸起136、138和底部掩模以形成多个着陆焊盘146和介于相邻的着陆焊盘146之间的开口148。着陆焊盘146直接形成在sti 104,以经由着陆焊盘146将sti 104连接至上方的存储节点。

47.与现有技术相比,本实施例提供的着陆焊盘的形成方法,将acp(array close photo)光刻转换为acp蚀刻工艺,省略了焊盘图案掩模层的回蚀刻和清洁工艺和侧壁清洁工艺等,从而简化了连接sn与snc的着陆焊盘形成工艺。

48.在形成着陆焊盘146之后,通过干清洁工艺去除工艺室中的残留物。残留物可以包括:tin颗粒、w颗粒、c,f,cfx聚合物、c,f,sixfy聚合物和涂层。具体地,通过cl2去除工艺室中的tin颗粒,通过sf6去除工艺室中的w颗粒,通过nf3去除工艺室中的c,f,cfx聚合物,通过o2去除工艺室中的c,f,sixfy聚合物,以及通过sicl4去除工艺室中的涂层。在优选实施例中,图5示出了具体参数设置。

49.与现有技术相比,本实施例提供的着陆焊盘的形成方法,在蚀刻工艺期间工艺室中会形成很多聚合物,在形成着陆焊盘之后,将多种蚀刻气体提供给工艺室以去除这些聚合物,以能够维持工艺室干净。

50.本发明的一个具体实施例,公开了一种dram的形成方法,包括:使用以上所述的着陆焊盘的形成方法形成着陆焊盘,其中,着陆焊盘用于连接上面存储节点和下面sti。

51.与现有技术相比,本发明至少可实现如下有益效果之一:

52.1、将acp(array close photo)光刻转换为acp蚀刻工艺,省略了焊盘图案掩模层的回蚀刻和清洁工艺和侧壁清洁工艺等,从而简化了连接sn与snc的着陆焊盘形成工艺。

53.2、在相同的工艺室中对阻挡金属层、着陆焊盘层、底部掩模层和焊盘图案掩模层实施原位蚀刻工艺,避免在不同工艺室中实施6个不同工艺步骤,例如,图案掩模层回蚀刻工艺、图案掩模层清洁工艺、侧壁清洁工艺、掩模蚀刻工艺、钨蚀刻工艺和阻挡金属蚀刻工艺,节省了不同工艺室中转移时间和器件装卸时间,仅使用单个工艺室,大幅度缩短了工艺时间,降低了工艺成本。

54.3、工艺室在蚀刻期间会形成很多聚合物,在形成着陆焊盘之后,将多种蚀刻气体提供给工艺室以去除这些聚合物,以能够维持工艺室干净。

55.在以上的描述中,对于各层的构图、刻蚀等技术细节并没有做出详细的说明。但是本领域技术人员应当理解,可以通过各种技术手段,来形成所需形状的层、区域等。另外,为了形成同一结构,本领域技术人员还可以设计出与以上描述的方法并不完全相同的方法。另外,尽管在以上分别描述了各实施例,但是这并不意味着各个实施例中的措施不能有利地结合使用。

56.以上对本公开的实施例进行了描述。但是,这些实施例仅仅是为了说明的目的,而并非为了限制本公开的范围。本公开的范围由所附权利要求及其等价物限定。不脱离本公

开的范围,本领域技术人员可以做出多种替代和修改,这些替代和修改都应落在本公开的范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1