半导体结构及半导体结构的形成方法与流程

1.本发明涉及半导体制造的技术领域,尤其涉及一种半导体结构及半导体结构的形成方法。

背景技术:

2.随着元件的微型化及集成度的增加,单层金属的半导体结构已经不能够满足现阶段对半导体材料的性能和速度要求,半导体结构由原先的单层金属层演变为多层金属层,半导体结构中的互连金属导线的数目也不断增多。

3.随着金属层以及金属导线不断增多,半导体结构的电阻(r)及电容(c)寄生效应增大,而寄生效应的增大造成严重的传输延迟(rc delay),传输延迟在130纳米及更先进的技术中成为电路中讯号传输速度受限的主要因素。现有技术在半导体工艺中采用新的低电阻材料铜作为互连导线和具有低k值(低介电常数)的介电薄膜作为金属内和金属层间的绝缘材料,以降低传输延迟。

4.然而,现有工艺形成的介电薄膜,已经不能满足现阶段的半导体结构对性能和速度的要求。

技术实现要素:

5.本技术实施例通过提供一种半导体结构及半导体结构的形成方法,解决了现有工艺形成的介电薄膜,已经不能满足现阶段的半导体结构对性能和速度的要求的技术问题。

6.一方面,本技术通过本技术的一实施例提供如下技术方案:

7.一种半导体结构,包括:金属结构;以及设置在所述金属结构之间的介电薄膜,其中,所述介电薄膜包括:择优取向层及设置于所述择优取向层之上的无定型非结晶层,所述择优取向层为晶体定向的膜层,所述无定型非结晶层为晶体不定向的膜层。

8.在一个实施例中,所述择优取向层的厚度占所述介电薄膜的总厚度的5%-50%,其中,所述介电薄膜的总厚度是指所述择优取向层与所述无定型非结晶层的厚度之和。

9.另一方面,本技术通过本技术的一实施例提供如下技术方案:

10.一种半导体结构的形成方法,所述半导体结构包括金属结构及设置于所述金属结构之间的介电薄膜,所述介电薄膜的形成方法包括:形成择优取向层,所述择优取向层为晶体定向的膜层;在所述择优取向层上形成无定型非结晶层,所述无定型非结晶层为晶体不定向的膜层。

11.在一个实施例中,所述形成择优取向层,包括:在原子层沉积设备中对前驱体进行沉积,形成所述择优取向层。

12.在一个实施例中,在执行所述形成所述择优取向层的步骤时,所述原子层沉积设备的工艺腔室的温度为400℃~700℃,所述原子层沉积设备的功率为1000w~3000w。

13.在一个实施例中,在执行所述形成所述择优取向层的步骤时,若所述介电薄膜为二氧化硅,所述前驱体所提供的硅原子和氧原子的原子数量比为0.6~1。

14.在一个实施例中,在执行所述形成所述择优取向层的步骤时,控制所述择优取向层的厚度为所述介质薄膜的总厚度的5%-50%,所述介电薄膜的总厚度是指所述择优取向层与所述无定型非结晶层的厚度之和。

15.在一个实施例中,所述择优取向层上形成无定型非结晶层,包括:在原子层沉积设备中对前驱体进行沉积,形成所述无定型非结晶层。

16.在一个实施例中,在执行所述形成所述无定型非结晶层的步骤时,所述原子层沉积设备的工艺腔室的温度为200℃~400℃,所述原子层沉积设备的功率为50w~1000w。

17.在一个实施例中,在执行所述形成所述无定型非结晶层的步骤时,若所述介电薄膜为二氧化硅,所述前驱体所提供的硅原子和氧原子的原子数量比为0.1~0.7。

18.本技术实施例中提供的一个或多个技术方案,至少具有如下技术效果或优点:

19.本技术所提供的半导体结构中,设置在金属结构之间的介电薄膜的结构包括位于下层的择优取向层、以及位于择优取向层之上的无定型非结晶层,该结构的介电薄膜,由于下层择优取向层的存在,使得诱电率得以降低,从而有效降低了择优取向层和无定型非结晶层的介电常数,从而使得整个介电薄膜的介电常数得以降低,解决了现有工艺形成的介电薄膜,已经不能满足现阶段的半导体结构对性能和速度的要求的技术问题。

20.本技术所提供的半导体结构的形成方法中,在形成位于金属结构之间的介电薄膜时,先形成位于下层的择优取向层,然后再形成位于择优取向层之上的无定型非结晶层,该工艺所得的介电薄膜,由于下层择优取向层的存在,使得诱电率得以降低,从而有效降低了择优取向层和无定型非结晶层的介电常数,从而使得整个介电薄膜的介电常数得以降低,解决了现有工艺形成的介电薄膜,已经不能满足现阶段的半导体结构对性能和速度的要求的技术问题。

附图说明

21.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

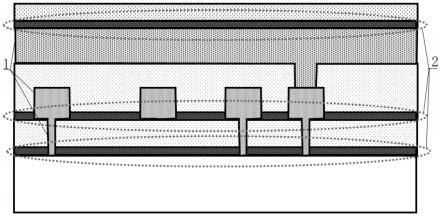

22.图1为本技术实施例一提供的一种半导体结构的结构示意图;

23.图2为图1中的介电薄膜的放大图;

24.图3为本技术实施例二提供的一种半导体结构的形成方法的流程图。

具体实施方式

25.本技术实施例通过提供一种半导体结构及半导体结构的形成方法,解决了现有工艺形成的介电薄膜,已经不能满足现阶段的半导体结构对性能和速度的要求的技术问题。

26.本技术实施例的技术方案为解决上述技术问题,总体思路如下:

27.本技术所提供的半导体结构中,设置在金属结构之间的介电薄膜的结构包括位于下层的择优取向层、以及位于择优取向层之上的无定型非结晶层,该结构的介电薄膜,由于下层择优取向层的存在,使得诱电率得以降低,从而有效降低了择优取向层和无定型非结晶层的介电常数,从而使得整个介电薄膜的介电常数得以降低,解决了现有工艺形成的介

电薄膜,已经不能满足现阶段的半导体结构对性能和速度的要求的技术问题。

28.本技术所提供的半导体结构的形成方法中,在形成位于金属结构之间的介电薄膜时,先形成位于下层的择优取向层,然后再形成位于择优取向层之上的无定型非结晶层,该工艺所得的介电薄膜,由于下层择优取向层的存在,使得诱电率得以降低,从而有效降低了择优取向层和无定型非结晶层的介电常数,从而使得整个介电薄膜的介电常数得以降低,解决了现有工艺形成的介电薄膜,已经不能满足现阶段的半导体结构对性能和速度的要求的技术问题。

29.以下,将参照附图来描述本公开的实施例。但是应该理解,这些描述只是示例性的,而并非要限制本公开的范围。此外,在以下说明中,省略了对公知结构和技术的描述,以避免不必要地混淆本公开的概念。

30.实施例一

31.如图1所示,本实施例提供了一种半导体结构,包括:

32.金属结构1,以及设置在金属结构1之间的介电薄膜2,如图1中的虚线部分,具体实施过程中,金属结构1可以指多层半导体结构中的金属层,对应的,介电薄膜2可以指位于两个金属层之间的层间介质层;金属结构1也可以指半导体结构中用于积淀导电材料以导通两个金属层的通孔结构,对应的,介电薄膜2可以指位于两个通孔结构之间的介质层;金属结构1还可以指单层金属层中的互连金属导线,对应的,介电薄膜2可以指位于两根互连金属导线之间的介质层。

33.如图2所示,该图为图1中的介电薄膜2的放大图,介电薄膜2包括:

34.设置于下层的择优取向层21、及设置于择优取向层21之上的无定型非结晶层22,择优取向层21为晶体定向的膜层,无定型非结晶层22为晶体不定向的膜层。

35.具体实施过程中,介电薄膜2还可以在无定型非结晶层22的上方叠加现有技术中的介质层。

36.本实施例中,由于下层择优取向层的存在,使得诱电率得以降低,从而有效降低了择优取向层21和无定型非结晶层22的介电常数,从而使得整个介电薄膜的介电常数得以降低。

37.作为一种可选的实施例,择优取向层21的厚度占介电薄膜2的总厚度的5%-50%,其中,介电薄膜2的总厚度是指择优取向层21与无定型非结晶层22的厚度之和。

38.本实施例中,当择优取向层21的厚度占介电薄膜2的总厚度的5%-50%时,择优取向层21的介电常数能够达到1~2.4,无定型非结晶层22的介电常数能够达到2.5~5。该介电常数的介电薄膜2较现有技术中的介电薄膜,具有更低的介电常数,能够减少rc(resistive-capacitive)延迟,提高信号传输的速度,进而提升元件的性能。

39.上述本技术实施例中的技术方案,至少具有如下的技术效果或优点:

40.本技术所提供的半导体结构中,设置在金属结构之间的介电薄膜的结构包括位于下层的择优取向层、以及位于择优取向层之上的无定型非结晶层,该结构的介电薄膜,由于下层择优取向层的存在,使得诱电率得以降低,从而有效降低了择优取向层和无定型非结晶层的介电常数,从而使得整个介电薄膜的介电常数得以降低,解决了现有工艺形成的介电薄膜,已经不能满足现阶段的半导体结构对性能和速度的要求的技术问题。

41.实施例二

42.如图2、3所示,本实施例提供了一种半导体结构的形成方法,如图1所示,半导体结构包括金属结构及设置于金属结构1之间的介电薄膜2,如图1中的虚线部分,具体实施过程中,金属结构1可以指多层半导体结构中的金属层,对应的,介电薄膜2层可以指位于两个金属层之间的层间介质层;金属结构1也可以指半导体结构中用于积淀导电材料以导通两个金属层的通孔结构,对应的,介电薄膜2层可以指位于两个通孔结构之间的介质层;金属结构1还可以指单层金属层中的互连金属导线,对应的,介电薄膜2可以指位于两根互连金属导线之间的介质层。

43.介电薄膜2的形成方法包括:

44.步骤s101:形成择优取向层21,择优取向层21为晶体定向的膜层。

45.作为一种可选的实施例,步骤s101包括:

46.在原子层沉积设备中对前驱体进行沉积,形成择优取向层21。

47.具体实施过程中,形成择优取向层21的沉积工艺可以通过等离子体增强化学的气相沉积工艺pecvd(plasma enhanced chemical vapor deposition)实现,具体按照如下工艺条件执行:

48.在执行步骤s101时,原子层沉积设备的工艺腔室的温度为400℃~700℃,作为一个示例,温度可以为401℃、500℃、535℃、603℃、695℃,原子层沉积设备的功率为1000w~3000w,作为一个示例,功率可以为1005w、1988w、2100w、2530w、2983w。

49.在执行步骤s101时,若介电薄膜2为二氧化硅,前驱体所提供的硅原子和氧原子的原子数量比为0.6~1,作为一个示例,可以为0.6、0.7、0.8、0.9、1,前驱体可以选用sioc;若介电薄膜2为三氧化二铝,前驱体所提供的铝原子和氧原子的原子数量比为0.7~1,作为一个示例,可以为0.7、0.8、0.85、0.9、1。实际实施过程中,介电薄膜2还可以为其他类型的材料,例如:金属氧化物或半导体材料,前驱体所提供的原子数量比需要打破中性状态(例如:当介电薄膜2为二氧化硅时,硅原子与氧原子的原子数量比为1:2,则为中性状态),呈现正带电状态,即容易失去外层电子的原子与容易得到电子的原子的数量比要大于中性状态时的比例。

50.步骤s102:在择优取向层21上形成无定型非结晶层22,无定型非结晶层22为晶体不定向的膜层。

51.作为一种可选的实施例,步骤s102包括:

52.在原子层沉积设备中对前驱体进行沉积,形成无定型非结晶层22。

53.具体实施过程中,形成无定型非结晶层22的沉积工艺可以通过等离子体增强化学的气相沉积工艺pecvd(plasma enhanced chemical vapor deposition)实现,具体按照如下工艺条件执行:

54.在执行步骤s102时,原子层沉积设备的工艺腔室的温度为200℃~400℃,作为一个示例,温度可以为210℃、280℃、300℃、310℃、396℃,原子层沉积设备的功率为50w~1000w,作为一个示例,功率可以为50w、300w、500w、700w、950w。

55.在执行步骤s102时,若介电薄膜2为二氧化硅,前驱体所提供的硅原子和氧原子的原子数量比为0.1~0.7,作为一个示例,可以为0.1、0.3、0.4、0.5、0.6,前驱体可以选用sioc;若介电薄膜2为三氧化二铝,前驱体所提供的铝原子和氧原子的原子数量比为0.1~0.5,作为一个示例,可以为0.1、0.25、0.3、0.4、0.45。实际实施过程中,介电薄膜2还可以为

其他类型的材料,例如:金属氧化物或半导体材料,前驱体所提供的原子数量比为需要打破中性状态(例如:当介电薄膜2为二氧化硅时,硅原子与氧原子的原子数量比为1:2,则为中性状态),呈现负带电状态,即容易失去外层电子的原子与容易得到电子的原子的数量比要小于中性状态时的比例。

56.进一步地,作为一种可选的实施例,在执行步骤s101时,控制择优取向层21的厚度为介质薄膜的总厚度的5%-50%,作为一个示例,可以为5%、10%、25%、35%、45%,介电薄膜2的总厚度是指择优取向层21与无定型非结晶层22的厚度之和。

57.具体实施过程中,可以通过控制沉积时间,来控制择优取向层21的厚度为介质薄膜的总厚度的5%-50%。

58.本实施例中,当按照上述工艺进行沉积,将能够得到具有晶向定向的择优取向层21和晶向不定向的无定型非结晶层22,当择优取向层21的厚度占介电薄膜2的总厚度的5%-50%时,择优取向层21的介电常数能够达到1~2.4,无定型非结晶层22的介电常数能够达到2.5~5。该介电常数的介电薄膜2较现有技术中的介电薄膜,具有更低的介电常数,能够减少rc(resistive-capacitive)延迟,提高信号传输的速度,进而提升元件的性能。

59.上述本技术实施例中的技术方案,至少具有如下的技术效果或优点:

60.本技术所提供的半导体结构的形成方法中,在形成位于金属结构之间的介电薄膜时,先形成位于下层的择优取向层,然后再形成位于择优取向层之上的无定型非结晶层,该工艺所得的介电薄膜,由于下层择优取向层的存在,使得诱电率得以降低,从而有效降低了择优取向层和无定型非结晶层的介电常数,从而使得整个介电薄膜的介电常数得以降低,解决了现有工艺形成的介电薄膜,已经不能满足现阶段的半导体结构对性能和速度的要求的技术问题。

61.在以上的描述中,对于各层的构图、刻蚀等技术细节并没有做出详细的说明。但是本领域技术人员应当理解,可以通过各种技术手段,来形成所需形状的层、区域等。另外,为了形成同一结构,本领域技术人员还可以设计出与以上描述的方法并不完全相同的方法。另外,尽管在以上分别描述了各实施例,但是这并不意味着各个实施例中的措施不能有利地结合使用。

62.尽管已描述了本发明的优选实施例,但本领域内的技术人员一旦得知了基本创造性概念,则可对这些实施例作出另外的变更和修改。所以,所附权利要求意欲解释为包括优选实施例以及落入本发明范围的所有变更和修改。

63.显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1