多次外延制作超结屏蔽栅结构IGBT及制造方法与流程

多次外延制作超结屏蔽栅结构igbt及制造方法

技术领域

1.本发明属于微电子技术领域,具体地说是一种多次外延制作超结屏蔽栅结构igbt及制造方法。

背景技术:

2.目前的igbt器件结构如图13所示,它包括第二导电类型集电极1、第一导电类型缓冲层2、第一导电类型衬底3、第二导电类型体区5、第一导电类型发射极6、绝缘介质层7、发射极金属8、栅极氧化层12与栅极导电多晶硅13。它在第一导电类型衬底3的正面向下开设有沟槽,在沟槽的侧面以及底面设置栅极氧化层12,在栅极氧化层12内设置栅极导电多晶硅13,在第一导电类型衬底3的正面经过高浓度第二导电类型杂质离子注入与推进,形成第二导电类型体区5,在第二导电类型体区5的正面经过高浓度第一导电类型杂质离子注入与推进,形成第一导电类型发射极6,在第一导电类型发射极6的正面设置绝缘介质层7,在绝缘介质层7的正面设置发射极金属8,发射极金属8通过通孔与第二导电类型体区5以及第一导电类型发射极6欧姆接触;在第一导电类型衬底3的背面设置第一导电类型缓冲层2,在第一导电类型缓冲层2的背面设置第二导电类型集电极1。

技术实现要素:

3.本发明的目的是克服现有技术中存在的不足,提供一种可在同等面积下实现更优效果的多次外延制作超结屏蔽栅结构igbt及制造方法。

4.按照本发明提供的技术方案,所述多次外延制作的超结屏蔽栅结构igbt,它包括第二导电类型集电极、第一导电类型缓冲层、第一导电类型衬底、第一导电类型外延层、第一导电类型柱、第二导电类型柱、第二导电类型体区、第一导电类型发射极、绝缘介质层、发射极金属、屏蔽栅氧化层、屏蔽栅多晶硅、屏蔽栅盖板、栅极氧化层与栅极导电多晶硅;在第一导电类型衬底的正面设置第一导电类型外延层,在第一导电类型外延层的正面向下开设沟槽,在沟槽的下段侧面以及底面设置屏蔽栅氧化层,在屏蔽栅氧化层内设置屏蔽栅多晶硅,在屏蔽栅多晶硅上设置屏蔽栅盖板,在沟槽的上段侧面设置栅极氧化层,在栅极氧化层内设置栅极导电多晶硅;在第一导电类型外延层的正面经过高浓度第二导电类型杂质离子注入与推进,形成第二导电类型体区,在第二导电类型体区的正面经过高浓度第一导电类型杂质离子注入与推进,形成第一导电类型发射极,在第一导电类型发射极的正面设置绝缘介质层,在绝缘介质层的正面设置发射极金属,发射极金属通过通孔与第二导电类型体区以及第一导电类型发射极欧姆接触;在第一导电类型衬底的背面设置第一导电类型缓冲层,在第一导电类型缓冲层的背面设置第二导电类型集电极;在对应第二导电类型体区位置的第一导电类型外延层内设有第二导电类型柱,相邻第二导电类型柱之间设有第一导电类型柱,且第二导电类型柱深入到第一导电类型衬底内。

5.作为优选,所述沟槽的宽度为0.2um

‑

2um,屏蔽栅盖板的背面至沟槽的底面之间的距离为1um

‑

10um。

6.作为优选,所述栅极导电多晶硅的宽度大于屏蔽栅多晶硅的宽度,栅极氧化层的厚度小于屏蔽栅氧化层的厚度。

7.作为优选,对于n型器件,第一导电类型为n型导电,第二导电类型为p型导电;对于p型器件,第一导电类型为p型导电,第二导电类型为n型导电。

8.上述多次外延制作的超结屏蔽栅结构igbt的制造方法包括以下步骤:步骤一、提供第一导电类型第一衬底,在第一导电类型衬底的正面淀积外延单元层,在外延单元层内注入低浓度第一导电类型杂质离子,以形成第一导电类型外延单元层;步骤二、以光刻胶为阻挡,在第一导电类型外延单元层的部分区域中注入第二导电类型杂质离子;步骤三、连续做若干次外延单元层淀积、低浓度第一导电类型杂质离子注入以及部分区域中第二导电类型杂质离子注入,然后再淀积一层外延单元层,在该外延单元层内注入低浓度第一导电类型杂质离子,以形成第一导电类型外延层;步骤四、在第一导电类型外延层中进行第二导电类型杂质离子推进形成第二导电类型柱,相邻第二导电类型柱之间设有第一导电类型柱,然后光刻和刻蚀出沟槽;步骤五、在沟槽的侧面以及底面生长出二氧化硅;步骤六、在沟槽内淀积出多晶硅,然后光照刻蚀掉部分二氧化硅与多晶硅,以形成屏蔽栅氧化层与屏蔽栅多晶硅;步骤七、在屏蔽栅多晶硅的正面淀积出二氧化硅进行光照刻蚀,以形成屏蔽栅盖板;步骤八、先在沟槽的上段侧面生长出二氧化硅,再在沟槽内淀积出多晶硅,最后进行光照刻蚀,以形成栅极氧化层与栅极导电多晶硅;步骤九、在位于最上方的第一导电类型外延单元层的正面进行高浓度第二导电类型杂质离子注入与推进,以形成第二导电类型体区;步骤十、首先以光刻胶为阻挡,在第二导电类型体区的正面进行高浓度第一导电类型杂质离子注入与推进,然后去除光刻胶,以形成第一导电类型发射极,最后进行硼磷硅玻璃淀积回流,以形成绝缘介质层;步骤十一、首先以光刻胶为阻挡,在绝缘介质层上光刻刻蚀出接触孔,接触孔部分伸入第二导电类型体区内,然后去除光刻胶,最后进行正面金属沉积、金属光刻刻蚀,以形成发射极金属;步骤十二、在第一导电类型衬底的背面进行高浓度第一导电类型杂质离子注入与推进,以形成第一导电类型缓冲层,在第一导电类型缓冲层的背面进行高浓度第二导电类型杂质离子注入,以形成第二导电类型集电极。

9.本发明可调节器件的电场分布,实现在低的阈值下有更有效的饱和电流,提高开关速度,降低开关损耗,实现更加稳定的安全工作区域。

附图说明

10.图1是经过实施例1的步骤一处理后的结构图。

11.图2是经过实施例1的步骤二处理后的结构图。

12.图3是经过实施例1的步骤三处理后的结构图。

13.图4是经过实施例1的步骤四处理后的结构图。

14.图5是经过实施例1的步骤五处理后的结构图。

15.图6是经过实施例1的步骤六处理后的结构图。

16.图7是经过实施例1的步骤七处理后的结构图。

17.图8是经过实施例1的步骤八处理后的结构图。

18.图9是经过实施例1的步骤九处理后的结构图。

19.图10是经过实施例1的步骤十处理后的结构图。

20.图11是经过实施例1的步骤十一处理后的结构图。

21.图12是经过实施例1的步骤十二处理后的结构图。

22.图13是现有技术中的igbt的结构图。

具体实施方式

23.下面结合具体实施例对本发明作进一步说明。

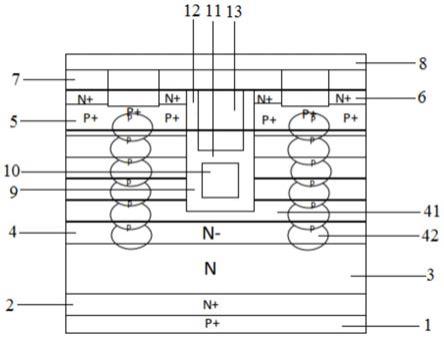

24.实施例1一种多次外延制作的超结屏蔽栅结构igbt,如图12所示,它包括第二导电类型集电极1、第一导电类型缓冲层2、第一导电类型衬底3、第一导电类型外延层4、第一导电类型柱41、第二导电类型柱42、第二导电类型体区5、第一导电类型发射极6、绝缘介质层7、发射极金属8、屏蔽栅氧化层9、屏蔽栅多晶硅10、屏蔽栅盖板11、栅极氧化层12与栅极导电多晶硅13;在第一导电类型衬底3的正面设置第一导电类型外延层4,在第一导电类型外延层4的正面向下开设沟槽,在沟槽的下段侧面以及底面设置屏蔽栅氧化层9,在屏蔽栅氧化层9内设置屏蔽栅多晶硅10,在屏蔽栅多晶硅10上设置屏蔽栅盖板11,在沟槽的上段侧面设置栅极氧化层12,在栅极氧化层12内设置栅极导电多晶硅13;在第一导电类型外延层4的正面经过高浓度第二导电类型杂质离子注入与推进,形成第二导电类型体区5,在第二导电类型体区5的正面经过高浓度第一导电类型杂质离子注入与推进,形成第一导电类型发射极6,在第一导电类型发射极6的正面设置绝缘介质层7,在绝缘介质层7的正面设置发射极金属8,发射极金属8通过通孔与第二导电类型体区5以及第一导电类型发射极6欧姆接触;在第一导电类型衬底3的背面设置第一导电类型缓冲层2,在第一导电类型缓冲层2的背面设置第二导电类型集电极1;在对应第二导电类型体区5位置的第一导电类型外延层4内设有第二导电类型柱42,相邻第二导电类型柱42之间设有第一导电类型柱41,且第二导电类型柱42深入到第一导电类型衬底3内。

25.所述沟槽的宽度为0.2um

‑

2um,屏蔽栅盖板11的背面至沟槽的底面之间的距离为1um

‑

10um。

26.所述栅极导电多晶硅13的宽度大于屏蔽栅多晶硅10的宽度,栅极氧化层12的厚度小于屏蔽栅氧化层9的厚度。

27.上述多次外延制作的超结屏蔽栅结构igbt的制造方法包括以下步骤:

步骤一、提供第一导电类型第一衬底3,在第一导电类型衬底3的正面淀积外延单元层,在外延单元层内注入低浓度第一导电类型杂质离子,以形成第一导电类型外延单元层,如图1所示;步骤二、以光刻胶为阻挡,在第一导电类型外延单元层的部分区域中注入第二导电类型杂质离子,如图2所示;步骤三、连续做若干次外延单元层淀积、低浓度第一导电类型杂质离子注入以及部分区域中第二导电类型杂质离子注入,以形成第一导电类型外延层4,然后在第一导电类型外延层4的正面再淀积一层外延单元层,在该外延单元层内注入低浓度第一导电类型杂质离子,如图3所示;步骤四、在第一导电类型外延层4中进行第二导电类型杂质离子推进形成第二导电类型柱42,相邻第二导电类型柱42之间设有第一导电类型柱41,然后光刻和刻蚀出沟槽,如图4所示;步骤五、在沟槽的侧面以及底面生长出二氧化硅,如图5所示;步骤六、在沟槽内淀积出多晶硅,然后光照刻蚀掉部分二氧化硅与多晶硅,以形成屏蔽栅氧化层9与屏蔽栅多晶硅10,如图6所示;步骤七、在屏蔽栅多晶硅10的正面淀积出二氧化硅进行光照刻蚀,以形成屏蔽栅盖板11,如图7所示;步骤八、先在沟槽的上段侧面生长出二氧化硅,再在沟槽内淀积出多晶硅,最后进行光照刻蚀,以形成栅极氧化层12与栅极导电多晶硅13,如图8所示;步骤九、在位于最上方的第一导电类型外延单元层的正面进行高浓度第二导电类型杂质离子注入与推进,以形成第二导电类型体区5,如图9所示;步骤十、首先以光刻胶为阻挡,在第二导电类型体区5的正面进行高浓度第一导电类型杂质离子注入与推进,然后去除光刻胶,以形成第一导电类型发射极6,最后进行硼磷硅玻璃淀积回流,以形成绝缘介质层7,如图10所示;步骤十一、首先以光刻胶为阻挡,在绝缘介质层7上光刻刻蚀出接触孔,接触孔部分伸入第二导电类型体区5内,然后去除光刻胶,最后进行正面金属沉积、金属光刻刻蚀,以形成发射极金属8,如图11所示;步骤十二、在第一导电类型衬底3的背面进行高浓度第一导电类型杂质离子注入与推进,以形成第一导电类型缓冲层2,在第一导电类型缓冲层2的背面进行高浓度第二导电类型杂质离子注入,以形成第二导电类型集电极1,如图12所示。

28.在实施例1中,第一导电类型为n型导电,第二导电类型为p型导电,其中,第二导电类型集电极1为p

+

型,第一导电类型缓冲层2为n

+

型,第一导电类型衬底3为n型,第一导电类型外延层4为n

‑

型,第二导电类型体区5为p

+

型,第一导电类型发射极6为n

+

型,第二导电类型柱42为p

+

型。

29.本发明的igbt器件是在现有技术的基础上,是通过多次生长出的区分了第一导电类型柱41与第二导电类型柱42的外延结构,其中,第一导电类型柱41位于沟槽的正下方,第二导电类型柱42位于第二导电类型体区4的正下方,即增添了栅极屏蔽结构。

30.在第一导电类型发射极6上开设有沟槽,沟槽向下第一导电类型发射极6与第二导电类型体区5并最终进入第一导电类型外延层4内,在沟槽的下段侧面以及底面设置屏蔽栅

氧化层9,在屏蔽栅氧化层9内设置屏蔽栅多晶硅10,在屏蔽栅多晶硅10上设置屏蔽栅盖板11,在沟槽的上段侧面设置栅极氧化层12,在栅极氧化层12内设置栅极导电多晶硅13,形成屏蔽栅结构;通过需要实现的更稳定的击穿电压,调整第一导电类型柱41与第二导电类型柱42的掺杂浓度,形成超结结构。

31.本发明中,屏蔽栅结构的作用主要是实现更快开关速度和更低的开关损耗;超结结构的作用主要是实现更稳点的耐压和更大的安全工作范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1