热电分离的基板结构及封装结构的制作方法

1.本实用新型涉及半导体封装技术领域,尤其涉及一种热电分离的基板结构及封装结构。

背景技术:

2.垂直腔面发射激光器(vertical cavity surface emitting laser,vcsel)是一种沿垂直于顶面方向发射激光的半导体器件,根据芯片制造工艺要求,需要对vcsel芯片进行模块化封装、性能测试及老化测试。

3.vcsel芯片属于面射型激光芯片,其激光发射方向不同于边射型激光芯片,导致vcsel芯片的性能及老化测试过程与边射型激光芯片的性能及老化测试过程存在差异,现有的芯片封装结构散热效果较差,且焊盘排布设计一般只支持单一芯片封装,兼容性差,无法同时满足边射型激光芯片和面射型激光芯片封装测试,在对常规芯片封装结构进行封装、性能测试及老化测试时,每个工艺流程均需要配置专业设备进行辅助,测试效率低,测试成本高。

技术实现要素:

4.本实用新型提供一种热电分离的基板结构,解决了现有的封装结构兼容性及散热效果差的问题,有利于提高散热性能,提高封测兼容性。

5.第一方面,本实用新型实施例提供了一种热电分离的基板结构,包括:铜基板、走线层、绝缘层、芯片焊盘、正极焊盘和负极焊盘,其中,所述芯片焊盘和所述负极焊盘与所述铜基板为一体化结构,所述芯片焊盘用于固定安装芯片本体;所述绝缘层设置于所述铜基板朝向所述芯片焊盘及所述负极焊盘的一侧;所述走线层设置于所述绝缘层背离所述铜基板的一侧,所述走线层形成有走线线路和所述正极焊盘,所述走线线路通过键合金线与所述芯片本体电连接。

6.可选地,所述热电分离的基板结构还包括散热底座,所述散热底座设置于所述铜基板背离所述走线层的一侧,所述散热底座上设有用于与所述铜基板热传导接触的导热介质。

7.可选地,所述热电分离的基板结构还包括形成于所述走线层的走线金属镀层,所述走线金属镀层呈半包围结构设置于所述芯片焊盘周围,所述走线金属镀层通过键合金线与所述芯片本体电连接。

8.可选地,所述热电分离的基板结构还包括阻焊油墨层,所述阻焊油墨层涂覆于所述铜基板上的非走线金属镀层区域及非焊盘区域。

9.可选地,所述铜基板设有至少两个定位通孔,所述定位通孔用于固定安装所述铜基板。

10.可选地,所述铜基板采用中心对称型结构。

11.可选地,所述铜基板具有第一面积s1,所述芯片焊盘具有第二面积s2,所述第一面

积s1和所述第二面积s2满足:s1≥2*s2。

12.第二方面,本实用新型实施例还提供了一种封装结构,包括芯片本体及上述热电分离的基板结构。

13.可选地,所述芯片本体包括激光芯片。

14.本实用新型实施例提供的封装结构,设置热电分离的基板结构,该基板结构包括铜基板、走线层、绝缘层、芯片焊盘、正极焊盘和负极焊盘,采用铜基板作为基板底材,芯片焊盘和负极焊盘与铜基板采用一体化结构,芯片本体通过粘晶技术固定于芯片焊盘,芯片本体通过键合金线与走线线路电连接,走线线路与铜基板之间设有绝缘层,利用绝缘层实现铜基板与走线线路的电气隔离,并且利用铜基板对芯片本体和负极焊盘进行散热,形成热电分离的结构,以使得芯片产生的热量及时通过铜基板实现散热,同时不影响芯片上电使用,解决了现有的封装结构兼容性及散热效果差的问题,有利于提高散热性能,简化对封装测试设备的硬件要求,提高封测兼容性,提升芯片测试效率,降低测试成本。

附图说明

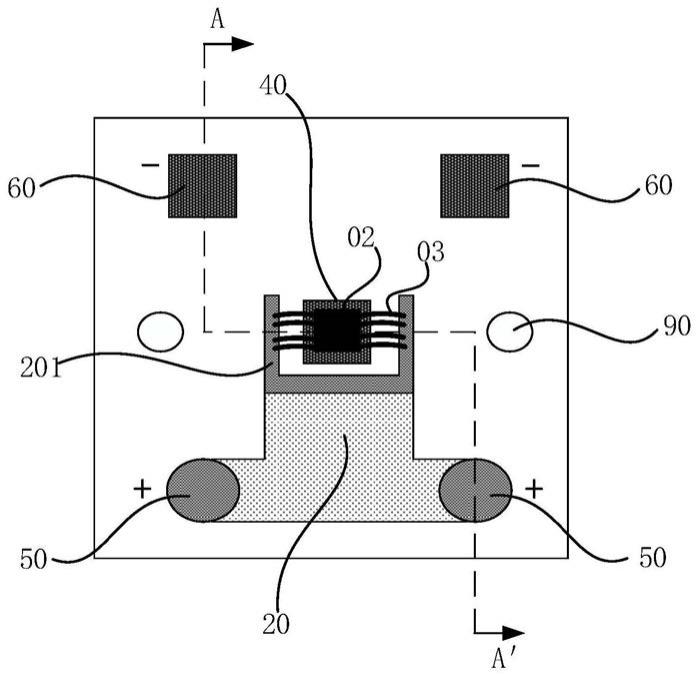

15.图1为本实用新型实施例一提供的一种热电分离的基板结构的结构示意图;

16.图2为沿图1中a-a'的剖面图;

17.图3为本实用新型实施例一提供的另一种热电分离的基板结构的结构示意图;

18.图4是本实用新型实施例二提供的一种封装结构的结构示意图。

具体实施方式

19.下面结合附图和实施例对本实用新型作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释本实用新型,而非对本实用新型的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本实用新型相关的部分而非全部结构。

20.实施例一

21.本实用新型实施例提供了一种热电分离的基板结构。图1为本实用新型实施例一提供的一种热电分离的基板结构的结构示意图。图2为沿图1中a-a'的剖面图。本实施例可适用于对vcsel芯片及应用其的激光模组产品进行封测的应用场景。

22.参考图1和图2所示,该基板结构01包括:铜基板10、走线层20、绝缘层30、芯片焊盘40、正极焊盘50和负极焊盘60,其中,芯片焊盘40和负极焊盘60与铜基板10为一体化结构,芯片焊盘40用于固定安装芯片本体02;绝缘层30设置于铜基板10朝向芯片焊盘40及负极焊盘60的一侧;走线层20设置于绝缘层30背离铜基板10的一侧,走线层20形成有走线线路和正极焊盘50,正极焊盘50与走线线路电连接,走线线路通过键合金线03与芯片本体02电连接。

23.本实施例中,铜基板10可采用紫铜、无氧铜等具有高导热率特性的铜材,绝缘层30可采用环氧玻璃布层压板fr-4制作而成,走线层20可采用本领域技术人员选用的常规铜箔材料,例如标准电解铜箔,铜箔材料的厚度可综合基板的性能要求及制作成本进行优选,对此不作限制。在进行基板结构加工时,首先在铜基板10上涂敷绝缘层30,然后在绝缘层30上涂敷铜箔材料,通过印刷、刻蚀及热压等工艺工序,在走线层20形成走线线路,走线线路与正极焊盘50电连接。

24.在本实施例中,芯片焊盘40、正极焊盘50和负极焊盘60表面均设有焊盘镀层(图示未显示),其中,焊盘镀层可采用镍钯金镀层或者其他金属镀层,通过化学沉金工艺对焊盘进行金属化处理,有利于提高设备可靠性。

25.具体地,在采用本实施例中的基板结构01进行封装测试时,可采用银浆粘贴材料或金锡低熔点镀金层将芯片本体02固晶于芯片焊盘40,芯片本体02与走线线路通过键合金线03电连接,芯片本体02和芯片焊盘40之间通过粘晶材料形成牢固的物理连接,粘晶材料具有良好的热传导特性,有利于粘晶材料作为介质将芯片本体02产生的热量传导至芯片焊盘40,芯片焊盘40与铜基板10一体成型,通过铜基板10对外传导散热。

26.参考图1所示,在进行封装测试时,正极焊盘50和负极焊盘60分别与外部电源的正极端和负极端,芯片本体02的正极端通过走线线路与正极焊盘50连接,芯片本体02的负极端通过芯片焊盘40及铜基板10与负极焊盘60连接,形成芯片供电回路,实现芯片本体02上电,完成芯片性能测试和老化测试,芯片本体02工作过程中,芯片的高速运行会导致芯片供电回路中产生热损耗,供电回路产生的热损耗也通过铜基板10对外传导,有利于提高负极焊盘60散热效率,避免焊盘过热损坏基板结构。

27.参考图1和图2所示,可通过金属沉金工艺在走线层20上形成走线金属镀层201,例如走线金属镀层201可呈半包围结构设置于芯片焊盘40周围,走线金属镀层201通过键合金线03与芯片本体02电连接有利于固定键合金线03,实现芯片本体02与走线层20的电连接。

28.由此,本实用新型实施例提供的热电分离的基板结构,设置铜基板、走线层、绝缘层、芯片焊盘、正极焊盘和负极焊盘,采用铜基板作为基板底材,芯片焊盘和负极焊盘与铜基板采用一体化结构制作而成,芯片本体通过粘晶技术固定于芯片焊盘,芯片本体通过键合金线与走线线路电连接,走线线路与铜基板之间设有绝缘层,利用绝缘层实现铜基板与走线线路的电气隔离,并且利用铜基板对芯片本体和负极焊盘进行快速散热,形成热电分离的结构,以使得芯片产生的热量及时通过铜基板实现散热,同时不影响芯片上电使用,解决了现有的封装结构兼容性及散热效果差的问题,有利于提高散热性能,简化对封装测试设备的硬件要求,提高封测兼容性,提升芯片测试效率,降低测试成本,通过采用焊盘镀层、固晶、键合金线等结构,有利于提供测试可靠性。

29.图3为本实用新型实施例一提供的另一种热电分离的基板结构的结构示意图。本实施例适用于通过加装热传导结构提高铜基板的散热效率的应用场景。

30.可选地,如图3所示,热电分离的基板结构01还包括散热底座70,散热底座70设置于铜基板10背离走线层20的一侧,散热底座70上设有用于与铜基板10热传导接触的导热介质。

31.本实施例中,可将铜基板10固定于散热底座70,散热底座70通过导热介质与铜基板10,有利于进一步提高基板结构01的散热效率。

32.示例性地,散热底座70包括热传导材料底座或者散热治具,导热介质可采用导热硅胶材料。

33.可选地,参考图1至图3所示,热电分离的基板结构01还包括阻焊油墨层80,阻焊油墨层80涂覆于铜基板10上的非走线金属镀层201区域及非焊盘区域。

34.具体地,在阻焊油墨层80在铜基板上的正投影与走线金属镀层201、芯片焊盘40、正极焊盘50及负极焊盘60在铜基板上的正投影不交叠,即言,在不设置金属镀层的走线层

上方涂覆阻焊油墨层80,在基板结构01表面形成保护膜层,有利于保护走线线路的图形,提高基板结构01的绝缘性能、耐焊性能及防潮耐热性能。

35.可选地,铜基板10设有至少两个定位通孔90,定位通孔90用于固定安装铜基板10。

36.参考图1所示,定位通孔90可设置于非走线区域,定位通孔90贯穿阻焊油墨层80和铜基板10,在安装基本结构时,可采用紧固结构穿过定位通孔90,将铜基板10固定安装于安装底座上。

37.可选地,铜基板10可采用中心对称型结构。

38.示例性地,铜基板10可采用方形、圆形或者矩形中心对称型结构,例如,该中心对称型结构可与安装底座中设置的基板安装槽的形状结构相匹配,在进行基板安装时,中心对称型结构设计可以简化安装工艺,提高测试效率。

39.可选地,铜基板10具有第一面积s1,芯片焊盘40具有第二面积s2,第一面积s1和第二面积s2满足:s1≥2*s2。

40.在本实施例中,芯片本体02的体积较小,一般只有几百微米见方,芯片本体02的运行功耗大,设置铜基板10具有的第一面积s1大于芯片焊盘40具有的第二面积s2的两倍,有利于增大铜基板10的散热面积,提高散热效率,满足芯片本体02快速散热的需求,避免热干扰对芯片测试造成的干扰。

41.示例性地,铜基板10通过物理切割加工工艺制作成方形平板结构,例如,可将铜基板10加工为长度为30毫米,宽度为30毫米,厚度为1.5毫米的方形平板结构。

42.实施例二

43.本实用新型实施例还提供了一种封装结构。图4是本实用新型实施例二提供的一种封装结构的结构示意图。如图4所示,该封装结构100包括芯片本体02及上述热电分离的基板结构01,芯片本体02通过键合金线03与热电分离的基板结构01电连接,且芯片本体02固定于热电分离的基板结构01的芯片焊盘上。

44.可选地,芯片本体02包括激光芯片。

45.在本实施例中,芯片本体02包括面射型激光芯片,例如为vcsel激光芯片或者具有vcsel激光芯片的激光模组。其中,激光模组可为激光雷达探测器。

46.本实用新型实施例提供的封装结构,设置热电分离的基板结构,该基板结构包括铜基板、走线层、绝缘层、芯片焊盘、正极焊盘和负极焊盘,采用铜基板作为基板底材,芯片焊盘和负极焊盘与铜基板采用一体化结构,芯片本体通过粘晶技术固定于芯片焊盘,芯片本体通过键合金线与走线线路电连接,走线线路与铜基板之间设有绝缘层,利用绝缘层实现铜基板与走线线路的电气隔离,并且利用铜基板对芯片本体和负极焊盘进行散热,形成热电分离的结构,以使得芯片产生的热量及时通过铜基板实现散热,同时不影响芯片上电使用,解决了现有的封装结构兼容性及散热效果差的问题,有利于提高散热性能,简化对封装测试设备的硬件要求,提高封测兼容性,提升芯片测试效率,降低测试成本。

47.注意,上述仅为本实用新型的较佳实施例及所运用技术原理。本领域技术人员会理解,本实用新型不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整和替代而不会脱离本实用新型的保护范围。因此,虽然通过以上实施例对本实用新型进行了较为详细的说明,但是本实用新型不仅仅限于以上实施例,在不脱离本实用新型构思的情况下,还可以包括更多其他等效实施例,而本实用新型的范围由所附

的权利要求范围决定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1