一种TFT阵列基板结构的制作方法

一种tft阵列基板结构

技术领域

1.本实用新型涉及tft阵列基板制作领域,尤其涉及一种tft阵列基板结构。

背景技术:

2.铟镓锌氧化物igzo(indium gallium zinc oxide),其载流子迁移率为非晶硅的20

‑

30倍,可以实现超高的分辨率的tft

‑

lcd,同时由于其高透明性,低成本,低制造温度等特点,在工业生产中得到广泛应用。

3.由于低温多晶硅(ltps)作为沟道层材料拥有更高的载流子迁移率(约为igzo

‑

tft的3~10倍),因此可作为周边gip区域驱动tft,利用其高载流子迁移率的特点,可以实现窄边框设计,但由于igzo

‑

tft相比于ltps

‑

tft 拥有更小的ioff,显示区域使用igzo

‑

tft只需要单栅极就可抑制漏电问题,从而实现低功耗的目的。现有ltpo技术,ltps

‑

tft作为gip区域,igzo

‑

tft 作为显示区域(aa区),可以利用ltps技术的高迁移率特性实现窄边框化,同时利用igzo技术的低ioff特性实现低功耗。因此,业界诸如厂商均开始投入ltpo型tft开发,实现窄边框低功耗显示技术,现有ltpo技术,ltps tft1 通常采用顶栅自对准结构结构,igzo tft2通常采用bce结构,在ltps工艺中,ild层通常使用siox/sinx双层结构,其中sinx膜质h离子含量较高,在后续退火制程中h离子移动,可起到poly

‑

si沟道晶格修补作用,改善器件的亚阈值摆幅,siox膜质因为其低介电常数可以减少寄生电容;但tft2中 igzo层对h离子较敏感,大量h离子移动易造成tft2 vth漂移,因此要减少 igzo tft2退火制程中h离子扩散。

技术实现要素:

4.为此,需要提供一种tft阵列基板结构,减少第二tft退火制程中h离子扩散。

5.为实现上述目的,本申请提供了一种tft阵列基板结构,所述基板上设置有第一tft区域和第二tft区域,所述基板上设置有第一有源层、第一栅极绝缘层、第一金属层、隔离层、第一源极和第一漏极;

6.所述基板的第一tft区域上设置有第一有源层设置于基板上,且所述第一有源层分为沟道区域和导体化区域,所述第一栅极绝缘层设置于所述沟道区域上,所述第一金属层设置于所述第一栅极绝缘层上,所述隔离层覆盖在第一有源层、第一栅极绝缘层和第一金属层上,所述第一源极和第一漏极通过所述隔离层上的第一通孔与所述导体化区域连接;

7.所述第二tft包括:第二金属层、第二栅极绝缘层、第二有源层、第二源极和第二漏极;所述第二金属层置于基板上,且所述第二栅极绝缘层覆盖在所述第二金属层以及所述第一tft上;所述第二有源层置于所述第二栅极层上,且位于所述第二金属层上方;于所述第二有源层两侧分别设置有第二源极和第二漏极,所述第二源极和第二漏极与所述第二有源层连接。

8.进一步地,还包括:绝缘层、钝化层、氧化铟锡公共电极层、氧化铟锡像素电极层;

9.所述钝化层置于所述第一tft、第二tft上,且所述绝缘层上设置有以第二源极或者第二漏极为底的第二通孔,所述氧化铟锡公共电极层分别置于所述第二通孔两侧;所述钝化层置于所述绝缘层上,且于所述第二通孔处开设有第三通孔,所述第三通孔与所述第二通孔共用一个底面,所述氧化铟锡像素电极层通过第三通孔与底部的第二源极或者第二漏极连接。

10.进一步地,还包括:平坦层;所述平坦层设置于所述绝缘层与所述钝化层之间,且所述平坦层位于第二通孔上设置有第四通孔,所述第四通孔与所述第二通孔、第三通孔相导通设置;所述氧化铟锡公共电极层设置于所述平坦层上,且设置于第四通孔的两侧。

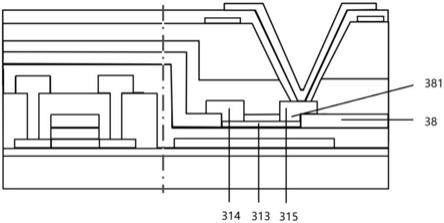

11.进一步地,还包括:蚀刻阻挡层;所述蚀刻阻挡层设置于所述绝缘层与所述第二栅极绝缘层之间,且位于所述第二有源层的两侧上设置有第五通孔,所述第二源极、第二漏极通过所述第五通孔与所述第二有源层连接。

12.区别于现有技术,上述技术方案通过tft阵列基板定义为两个区域,其中第一tft采用顶栅自对准结构,为gip区域;第二tft采用底栅结构(bce/ 蚀刻阻挡层结构),为显示区域(aa区),由于ltps工艺中,隔离层通常使用 siox/sinx双层结构,sinx膜质h离子含量较高,在后续退火制程中h离子移动,可起到第一有源层晶格修补作用,改善器件ss,但第二tft中的第二有源层对h离子较敏感,大量h离子移动易造成vth漂移,因此将第一tft的所述间隔离层ild蚀刻至仅保留在第一tft区域中,减少第二tft退火制程h 离子扩散,提升第二tft器件稳定性,同时由于隔离层仅保留在第一tft区域,aa区第二tft膜层厚度减薄,透过率增大,可提升显示效果。

附图说明

13.图1为背景技术ltpo阵列基板的结构剖面示意图;

14.图2为具体实施方式所述第一有源层结构图;

15.图3为具体实施方式所述第一tft结构图;

16.图4为具体实施方式所述第二tft结构图;

17.图5为一种tft阵列基板结构图。

18.图6为具体实施方式所述蚀刻阻挡层结构图。

19.附图标记说明:

20.1、基板;2、第一tft区域;3、第二tft区域;

21.21、第一tft;

22.31、第二tft;32、绝缘层;33、氧化铟锡公共电极层;34、钝化层; 35、氧化铟锡像素电极层;36、平坦层;37、缓冲层;38、蚀刻阻挡层;

23.211、第一有源层;212、第一栅极绝缘层;213、第一金属层;214、隔离层;215、第一通孔;216、第一源极;217、第一漏极;

24.311、第二金属层;312、第二栅极绝缘层;313、第二有源层;314、第二源极;315、第二漏极;381、第五通孔;

25.321、第二通孔;341、第三通孔;361、第四通孔;

26.2111、沟道区域;2112、导体化区域。

具体实施方式

27.为详细说明技术方案的技术内容、构造特征、所实现目的及效果,以下结合具体实施例并配合附图详予说明。

28.请参阅图1至6,本实施例提供了tft阵列基板的制作方法,包括步骤:将基板1分为第一tft区域2和第二tft区域3;于第一tft区域2制作第一有源层211,并将第一有源层211划分为沟道区域2111和导体化区域2112,所述导体化区域2112设置于所述沟道区域2111两侧;于所述沟道区域2111 上制作第一栅极绝缘层212;于第一栅极绝缘层212上制作第一金属层213;制作隔离层214,并蚀刻位于所述第二tft区域3上的所隔离层214;蚀刻隔离层214,形成以所述导体化区域2112为底的两个第一通孔215;制作第一源极216、第一漏极217和第二金属层311,所述第一源极216、第一漏极217 分别通过两个所述第一通孔215与所述有源层上的导体化区域2112连接;所第二金属层311置于所述第二tft区域3上;所述基板1为玻璃基板。需要说明的是,在本实施例中,所述第一有源层211为多晶硅有源层。在实际工艺中,通过掩膜板制作所述第一有源层211,在制作所述第一有源层211后,可以对所述第一有源层211进行部分的导体化,将所述第一有源层211分为导体化区域2112以及沟道区域2111,所述导体化区域2112设置于所述沟道区域2111两侧;通过一掩膜板制作所述第一栅极绝缘层212于所述沟道区域 2111上,需要说明的是,所述第一栅极绝缘层212将所述沟道区域2111完全覆盖,制作所述第一金属层213于所述第一栅极绝缘层212上。需要进一步说明的是,所述隔离层214为ild隔离层214,且材料为sinx,在制作所述隔离层214时,先将将所述隔离层214涂布至所有区域,在通孔掩膜板蚀刻去除位于所述第二tft区域3上的所述隔离层214,再通过掩膜板蚀刻两个第一通孔215,使所述第一源极216和第一漏极217与所述第一有源层211的所述导体化区域2112连接。在制作完成第一tft21后与所述第二tft区域3上制作第二tft31。在制作第一源极216、第一漏极217和第二金属层311的时候,通过掩膜板整体制备一层金属层,再经图案化后,于所述第一tft区域2 上的所述隔离层214上形成所述第一源极216和第一漏极217,在第二tft区域3的所述基板1上形成第二金属层311,在制作第一源极216、第一漏极217 和第二金属层311使用一层光罩,且三者的材料相同。上述技术方案通过tft 阵列基板1定义为两个区域,其中第一tft21采用顶栅自对准结构,为gip 区域;第二tft31采用底栅结构(bce/蚀刻阻挡层结构),为显示区域(aa区),由于ltps工艺中,隔离层214通常使用siox/sinx双层结构,sinx膜质h离子含量较高,在后续退火制程中h离子移动,可起到第一有源层211晶格修补作用,改善器件ss,但第二tft31中的第二有源层313对h离子较敏感,大量h离子移动易造成vth漂移,因此将第一tft21的所述间隔离层214ild蚀刻至仅保留在第一tft区域2中,减少第二tft31退火制程h离子扩散,提升第二tft31器件稳定性,同时由于隔离层214仅保留在第一tft区域2,aa 区第二tft31膜层厚度减薄,透过率增大,可提升显示效果。所述隔离层的h 离子大于所述第二栅极绝缘层中的h离子。

29.在某些实施例前,在所述“于第一tft区域2制作第一有源层211,并将第一有源层211划分为沟道区域2111和导体化区域2112,所述导体化区域 2112设置于所述沟道区域2111两侧”步骤前,还包括步骤:制作缓冲层37 与所述基板1上。

30.请参阅图4,在本实施例中,还步骤包括:制作第二栅极绝缘层312,所述第二栅极绝缘层312设置在所述第一tft区域2和第二tft区域3上;制作第二有源层313于第二栅极绝

缘层312上,且所述第二有源层313位于所述第二金属层311上方;制作第二源极314和第二漏极315,所述第二源极 314和第二漏极315分别与第二有源层313两侧连接。需要说明的是,所述第二栅极绝缘层312覆盖于所述第二金属层311和所述第一tft21上,且所述第二栅极绝缘层312采用的材料为siox;位于所述第二tft区域3的所述第二栅极绝缘层312的高度小于所述第一tft区域2的所述第二栅极绝缘层312 的高度。所述第二有源层313为igzo,制作所述第二有源层313于所述第二栅极层上,且位于所述第二金属层311的上方。并于第二有源层313两侧制作第二源极314和第二漏极315。第二tft31厚度在防止第二tft31 vth漂移的同时,减薄第二tft31的厚度,可进一步增大透过率,提升显示效果。

31.请参阅图4至5,在本实施例中,制作绝缘层32,所述绝缘层32设置在所述第一tft区域2和第二tft区域3上,并于所述绝缘层32上制作以第二源极314或第二漏极315为底的第二通孔321;于所述第二通孔321两侧分别制作两个氧化铟锡公共电极层33;制作钝化层34,所述钝化层34设置在所述第一tft区域2和第二tft区域3上,并于所述钝化层34上蚀刻第三通孔 341,所述第三通孔341与所述第二通孔321共用一个底面;制作氧化铟锡像素电极层35,使所述氧化铟锡像素电极层35与所述第二源极314或第二漏极 315连接。需要说明的是,在本实施例中,所述绝缘层32为绝缘层32pv;所述第二通孔321与所述第三通孔341共用一个底面,底面为第二源极314或者第二漏极315,且所述钝化层34置于所述绝缘层32上,同时覆盖在所述第二通孔321的侧壁上,所述氧化铟锡像素电极层35通过第三通孔341与所述第二源极314或第二漏极315连接。第二tft31厚度在防止第二tft31 vth 漂移的同时,减薄第二tft31的厚度,可进一步增大透过率,提升显示效果。

32.请参阅图5,在本实施例中,所述“于第二通孔321两侧分别制作两个氧化铟锡公共电极层33”步骤替换为:于所述绝缘层32上制作平坦层36,所述平坦层36设置在所述第一tft区域2和第二tft区域3上,且覆盖于所述绝缘层32上;并于所述平坦层36上蚀刻形成第四通孔361,所述第四通孔 361与所述第二通孔321、第三通孔341相导通设置;于所述第四通孔361两侧分别制作两个氧化铟锡公共电极层33。需要进一步说明的是,所述第四通孔361与所述第二通孔321是相导通设置,所述钝化层34置于所述平坦层36 上,且覆盖于所述第四通孔361和第二通孔321的侧壁上;所述钝化层34为钝化层34ch、所述平坦层36为平坦层36oc。

33.请参阅图6,在另一实施例中,在所述“制作第二有源层313于第二栅极绝缘层312上,且所述第二有源层313位于所述第二金属层311上方”步骤后,还包括步骤:在所述第二栅极绝缘层312上制作蚀刻阻挡层38,所述蚀刻阻挡层38设置在所述第一tft区域2和第二tft区域3上,即,将第一tft 区域2和第二tft区域3完全覆盖;蚀刻所述蚀刻阻挡层38,形成以所述第二有源层313为底的两个第五通孔381,且所述第二源极314和第二漏极315 分别通过一个第五通孔381与所述第二有源层313连接。在本实施例中,可保护所述第二有源层313不受后续工艺及环境影响。

34.所述第一tft区域2上设置有第一tft21;第二tft区域3上设置有第二 tft31;第一tft21为ltps型tft,采用顶栅自对准结构,为gip区域;第二 tft31为igzo型tft,采用bce结构,为显示区域(aa区)由于在所在玻璃基板上的不同区域前后进行两种不同类型的tft制备,使得第一tft21的制备不会影响第二tft31制备,从而降低了整个tft阵列基板的制程风险,进而提升了本申请tft阵列基板上的器件的稳定性。

35.请参阅图5至6,在本实施例中还提供了一种tft阵列基板结构,所述基板上设置有第一tft区域和第二tft区域,且所述第一tft区域上设置有第一tft,所述第二tft区域上设置有第二tft;所述第一tft21包括:第一有源层211、第一栅极绝缘层212、第一金属层213、隔离层214、第一源极216 和第一漏极217;所述第一有源层211设置于基板1上,且所述第一有源层 211分为沟道区域2111和导体化区域2112,所述第一栅极绝缘层212设置于所述沟道区域2111上,所述第一金属层213设置于所述第一栅极绝缘层212 上,所述隔离层214覆盖在第一有源层211、第一栅极绝缘层212和第一金属层213上,所述第一源极216和第一漏极217通过所述隔离层214上的第一通孔215与所述导体化区域2112连接;所述第二tft31包括:第二金属层311、第二栅极绝缘层312、第二有源层313、第二源极314和第二漏极315;所述第二金属层311置于基板1上,且所述第二栅极绝缘层312覆盖在所述第二金属层311以及所述第一tft21上;所述第二有源层313置于所述第二栅极层上,且位于所述第二金属层311上方;于所述第二有源层313两侧分别设置有第二源极314和第二漏极315,所述第二源极314和第二漏极315与所述第二有源层313连接。需要说明的是,所述基板1为玻璃基板。在本实施例中,所述第一有源层211为多晶硅有源层。所述第一有源层211部分为导体化区域2112,将所述第一有源层211分为导体化区域2112以及沟道区域2111,所述导体化区域2112设置于所述沟道区域2111两侧;需要说明的是,所述第一栅极绝缘层212将所述沟道区域2111完全覆盖。需要进一步说明的是,所述隔离层214为ild隔离层214,且材料为sinx,且所述隔离层214仅位于所述第一tft区域2内,同时所述隔离层214上还设置有两个第一通孔215,所述第一源极216和第一漏极217与所述第一有源层211的所述导体化区域 2112连接。所述第一源极216、第一漏极217和第二金属层311三者的材料相同,且一同制作。所述第一tft区域2上设置有第一tft21;第二tft区域 3上设置有第二tft31;第一tft21为ltps型tft,采用顶栅自对准结构,为 gip区域;第二tft31为igzo型tft,采用bce结构,为显示区域(aa区) 由于在所在玻璃基板上的不同区域前后进行两种不同类型的tft制备,使得第一tft21的制备不会影响第二tft31制备,从而降低了整个tft阵列基板的制程风险,进而提升了本申请tft阵列基板上的器件的稳定性。

36.请参阅图5,在某些实施中,还包括:绝缘层32、钝化层34、氧化铟锡公共电极层33、氧化铟锡像素电极层35;所述钝化层34置于所述第一tft21、第二tft31上,且所述绝缘层32上设置有以第二源极314或者第二漏极315 为底的第二通孔321,所述氧化铟锡公共电极层33分别置于所述第二通孔321 两侧;所述钝化层34置于所述绝缘层32上,且于所述第二通孔321处开设有第三通孔341,所述第三通孔341与所述第二通孔321共用一个底面,所述氧化铟锡像素电极层35通过第三通孔341与底部的第二源极314或者第二漏极315连接。需要说明的是,在本实施例中,所述绝缘层32为绝缘层32pv;所述第二通孔321与所述第三通孔341共用一个底面,底面为第二源极314 或者第二漏极315,且所述钝化层34置于所述绝缘层32上,同时设置在所述第二通孔321的侧壁上,所述氧化铟锡像素电极层35通过第三通孔341与所述第二源极314或第二漏极315连接。第二tft31厚度在防止第二tft31 vth 漂移的同时,减薄第二tft31的厚度,可进一步增大透过率,提升显示效果。

37.请参阅图5,在本实施例中,还包括:平坦层36;所述平坦层36设置于所述绝缘层32与所述钝化层34之间,且所述平坦层36位于第二通孔321上设置有第四通孔361,所述第四通孔361与所述第二通孔321、第三通孔341 相导通设置;所述氧化铟锡公共电极层33设置

于所述平坦层36上,且设置于第四通孔361的两侧。需要进一步说明的是,所述第四通孔361与所述第二通孔321是相导通设置,所述钝化层34置于所述平坦层36上,且覆盖于所述第四通孔361和第二通孔321的侧壁上;所述钝化层34为钝化层34ch、所述平坦层36为平坦层oc。

38.请参阅图6,在本实施例中,还包括:蚀刻阻挡层;所述蚀刻阻挡层设置于所述绝缘层32与所述第二栅极绝缘层312之间,且位于所述第二有源层313 的两侧上设置有第五通孔381,所述第二源极314、第二漏极315通过所述第五通孔381与所述第二有源层313连接。在本实施例中,可保护所述第二有源层313不受后续工艺及环境影响。

39.需要说明的是,尽管在本文中已经对上述各实施例进行了描述,但并非因此限制本实用新型的专利保护范围。因此,基于本实用新型的创新理念,对本文所述实施例进行的变更和修改,或利用本实用新型说明书及附图内容所作的等效结构或等效流程变换,直接或间接地将以上技术方案运用在其他相关的技术领域,均包括在本实用新型的专利保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1