具有用于降低的EMI的集成屏蔽拓扑结构的隔离变压器的制作方法

具有用于降低的emi的集成屏蔽拓扑结构的隔离变压器

背景技术:

1.集成隔离电源产品是具有半导体管芯和集成变压器的封装电子器件,其具有与外部可接近的引线(例如,引脚或焊盘)的电连接,用于焊接到印刷电路板(pcb)。隔离式dc到dc转换器可以使用集成高压隔离变压器构建,其中变压器线圈可以被制造成层压结构,以便集成到封装电子器件中。许多dc到dc转换器具有用于电磁干扰(emi)的设计规范,诸如cispr32和cispr25对额定均方根ac或dc电源电压不超过由comit

é

international sp

é

cial des perturbations radio

é

lectriques(cispr)设定的600v的多媒体设备(mme)的emi辐射要求。dc到dc转换器中的初级侧和/或次级侧晶体管的切换可导致传导和/或发射emi,例如,隔离式dc到dc转换器的变压器由于其绕组间电容而可能成为电磁能的路径。可以使用铁氧体磁珠、附加电容器或其它外部(例如,板层级)组合件来控制emi,但这会增加电路面积、重量和成本。此外,每种设计在电场、效率和电磁干扰(emi)性能方面都具有不同的规范。其它emi控制方法包括用于控制dc到dc转换器开关的扩频调制(ssm),但这需要额外的管芯空间,并且通常只能提供递增的emi改善。

技术实现要素:

2.根据一个方面,一种封装电子器件包括至少部分暴露于封装结构的外部的导电引线、至少部分暴露于封装结构的外部的第二导电引线,以及在封装结构中的多级层压结构。多级层压结构包括第一和第二图案化导电特征部以及导电屏蔽迹线。第一图案化导电特征部在多级层压结构的第一层级中具有多个线匝以形成耦合至第一电路中的第一导电引线中的至少一个第一导电引线的第一绕组。第二图案化导电特征部在不同层级中具有多个线匝以形成耦合至与第一电路隔离的第二电路中的第二导电引线中的至少一个第二导电引线的第二绕组。导电屏蔽迹线在与第一图案化导电特征部和第二图案化导电特征部间隔开并位于它们之间的第二层级中具有多个线匝。导电屏蔽迹线耦合在第一电路中。

3.在一个示例中,多级层压结构包括第二导电屏蔽迹线,该第二导电屏蔽迹线在第一图案化导电特征部和第二图案化导电特征部之间的另一层级中具有多个线匝。第二导电屏蔽迹线耦合在第二电路中,并且第二导电屏蔽迹线与第一导电屏蔽迹线间隔开。在一个示例中,第一导电屏蔽迹线耦合至第一电路的接地参考节点,并且第二导电屏蔽迹线耦合至第二电路的第二接地参考节点。在某些实施方式中,一个或多个屏蔽件可以相对于图案化导电特征部位于外围。在一个示例中,第一导电屏蔽迹线包括从第一层级中的第一图案化导电特征部的最外侧横向范围向外横向间隔开的线匝,并且第二导电屏蔽迹线包括与不同层级中的第二图案化导电特征部的最外侧线匝横向间隔开的线匝。在某些实施方式中,一个或多个屏蔽件可以与图案化导电特征部交错。在一个示例中,第一导电屏蔽迹线与第一层级中的第一图案化导电特征部的线匝交错,并且第二导电屏蔽迹线与不同层级中的第二图案化导电特征部的线匝交错。

4.根据另一方面,一种多级层压结构包括在第一层级中具有多个线匝以形成第一绕组的第一图案化导电特征部,以及在不同层级中具有多个线匝以形成第二绕组的第二图案

化导电特征部,以及在与第一图案化导电特征部和第二图案化导电特征部间隔开并位于它们之间的第二层级中具有多个线匝的导电屏蔽迹线。在一个示例中,多级层压结构进一步包括第二导电屏蔽迹线,该第二导电屏蔽迹线在第一图案化导电特征部和第二图案化导电特征部之间的另一层级中具有多个线匝。在一个示例中,第一导电屏蔽迹线包括从第一层级中的第一图案化导电特征部的最外侧横向范围向外横向间隔开的线匝,并且第二导电屏蔽迹线包括与不同层级中的第二图案化导电特征部的最外侧线匝横向间隔开的线匝。在一个示例中,第一导电屏蔽迹线与第一层级中的第一图案化导电特征部的线匝交错,并且第二导电屏蔽迹线与不同层级中的第二图案化导电特征部的线匝交错。

5.根据另一方面,一种方法包括将具有多级层压结构的磁性组合件附接至支撑结构,将第一半导体管芯附接至第一管芯附接焊盘,并将第二半导体管芯附接至第二管芯附接焊盘,以及执行电连接工艺和模制工艺。电连接工艺耦合第一半导体管芯、多级层压结构的第一绕组、多级层压结构的第一导电屏蔽迹线以及第一电路中的一组第一导电引线中的至少一个第一导电引线。此外,电连接工艺耦合第二半导体管芯、多级层压结构的第二绕组、多级层压结构的第二导电屏蔽迹线以及与第一电路隔离的第二电路中的一组第二导电引线中的至少一个第二导电引线。模制工艺将磁性组合件、管芯附接焊盘、半导体管芯、第一和第二导电引线的一些部分包封在封装结构中。在一个示例中,电连接工艺将第一导电屏蔽迹线耦合至第一电路的接地参考节点,并将第二导电屏蔽迹线耦合至第二电路的第二接地参考节点。

附图说明

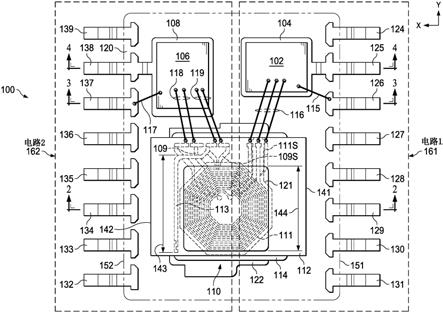

6.图1是包括具有导电屏蔽迹线的磁性组合件的封装电子器件的仰视图。

7.图2是沿图1中的线2

‑

2截取的封装电子器件的局部截面端视图。

8.图3是沿图1中的线3

‑

3截取的封装电子器件的局部截面端视图。

9.图4是沿图1中的线4

‑

4截取的封装电子器件的局部截面端视图。

10.图5是图1

‑

图4的封装电子器件的俯视图。

11.图6是图1

‑

图5的封装电子器件的底部透视图。

12.图7是制造封装电子器件的方法的流程图。

13.图8

‑

图13是根据图7的方法进行制造的图1

‑

图6的封装电子器件的局部截面端视图。

14.图14是具有第一和第二绕组以及第一和第二导电屏蔽迹线的图1

‑

图6的封装电子器件的多级层压结构的仰视图。

15.图15是具有图14的多级层压结构和上下磁芯的图1

‑

图6的封装电子器件的磁性组合件的仰视图。

16.图16是沿图15中的线16

‑

16截取的磁性组合件的一个实施例的局部截面端视图。

17.图17是沿图15中的线16

‑

16截取的磁性组合件的另一实施例的局部截面端视图。

18.图18是沿图15中的线16

‑

16截取的磁性组合件的第三实施例的局部截面端视图。

19.图19是沿图15中的线16

‑

16截取的磁性组合件的第四实施例的局部截面端视图。

20.图20是沿图15中的线16

‑

16截取的磁性组合件的第五实施例的局部截面端视图。

21.图21是沿图15中的线16

‑

16截取的磁性组合件的第六实施例的局部截面端视图。

22.图22是沿图15中的线16

‑

16截取的磁性组合件的第七实施例的局部截面端视图。

23.图23是具有耦合至第一电路的第一接地参考节点的第一导电屏蔽迹线的图1

‑

图6的封装电子器件的一个实施例的示意图。

24.图24是具有耦合至第二电路的第二接地参考节点的第二导电屏蔽迹线的图1

‑

图6的封装电子器件的另一实施例的示意图。

25.图25是具有耦合至第一和第二电路的相应第一和第二接地参考节点的第一和第二导电屏蔽迹线的图1

‑

图6的封装电子器件的另一实施例的示意图。

具体实施方式

26.在附图中,相同的附图标记始终指代相同的元件,并且各种特征不一定按比例绘制。在以下讨论和权利要求中,术语“包括”、“包含”、“具有”、“拥有”、“带有”或其变体旨在以类似于术语“包括”的方式包含在内,并且因此应解释为“包括但不限于

……”

。此外,术语“耦合”或“耦接”旨在包括间接或直接的电气或机械连接或其组合。例如,如果第一器件耦合至第二器件或与第二器件耦合,则该连接可以是通过直接电连接,或通过经由一个或多个中间器件和连接件的间接电连接。

27.首先参考图1

‑

图6,所描述的示例提供了具有集成磁体的封装电子器件,诸如带有集成隔离变压器的dc到dc转换器,其具有一个或多个导电屏蔽迹线以减轻或控制emi辐射。所示示例的emi解决方案在降低emi方面优于ssm,并提供优于使用附加板级组合件(诸如铁氧体磁珠和/或附加电容器)的电路面积、重量和成本的优势。使用具有集成屏蔽技术的变压器允许终端用户降低emi,而无需增加解决方案成本的分立铁氧体磁珠,并且无需具备降低emi的专业知识来设计使用封装电子器件的系统。横跨dc到dc转换器的隔离屏障阻抗的不对称电压会通过两个隔离的接地平面产生辐射,该接地平面成为偶极天线并辐射噪声。图1

‑

图6示出具有层压磁性组合件的示例封装电子器件100,该层压磁性组合件在不同电压域的绕组(诸如初级和次级变压器绕组)之间具有导电屏蔽迹线。

28.导电屏蔽迹线解决方案可用于具有对称或非对称磁性组合件定位的产品中,并提供可扩展的解决方案以适应具有不同电场、效率和/或emi性能规范的设计。导电屏蔽迹线解决方案可与磁性组合件一起使用,该磁性组合件与半导体管芯一起安装到图1

‑

图6中所示的共享管芯附接焊盘,或者磁性组合件可以被单独地支撑在与集成半导体管芯和相关联的导电管芯附接焊盘间隔开的导电支撑结构上。导电屏蔽迹线可以设置在多级层压结构的一个或多个层或层级中。图1示出示例器件100的仰视图,并且图2

‑

图4示出沿图1中的相应线2

‑

2、3

‑

3和4

‑

4的局部截面视图和正视图。图5示出封装电子器件100的俯视图,并且图6示出封装电子器件100的底部透视图。

29.示例电子器件100具有小外形集成电路(soic)封装类型,其在相对两侧具有鸥翼引线(gull wing lead)。可以在不同的实施方式中提供其它封装电子器件,包括可焊接到另一个结构或多个结构以用于电互连的导电特征部,诸如所谓的无引线封装类型(例如扁平无引线封装,诸如四方扁平无引线封装(qfn)、双扁平无引线(dfn)、微型引线框架(mlf))和带有平面导电引线(诸如在封装底部和/或侧面上提供到印刷电路板(pcb)的电气连接的周边焊盘)的小外形无引线(son)类型。在其它示例中,器件100包括球栅阵列(bga)封装或焊盘栅阵列(lga)类型,诸如模制阵列工艺球栅阵列(mapbga)或过模制bga(例如塑料bga或

pbga)。

30.此外,图1

‑

图6的示例器件100提供了用于第一和第二电路的电互连件,其中的一些或全部使用键合线来实现。在其它实施方式中,可以使用不同形式的互连类型,包括基于衬底的互连件(bga、lga等),并且其中衬底包括单独或与键合线电连接件结合使用的电互连件和信号路由结构(例如,一个或多个层或层级上的铜或铝迹线)。如图1中所示,示例器件100包括用于安装和支撑第一和第二半导体管芯以及层压磁性组合件的导电特征部(例如,导电管芯附接焊盘或支撑件)。管芯附接焊盘和器件引线可以包括任何合适的导电结构,诸如铜、铝等。

31.图1中的示例器件100包括附接至引线框架组合件的第一导电管芯附接焊盘104的第一半导体管芯102。器件100还包括附接至第二导电管芯附接焊盘108的第二半导体管芯106。电子器件100包括与第一电压域(例如,集成功率器件的高压初级电路)相关联的第一电路(例如,161,图1中标记为“电路1”)。器件100还包括与第二电压域(例如,隔离的较低电压次级电路)相关联的第二电路(例如,162,标记为“电路2”)。该示例中的第二电路162包括由磁性组合件110的第二图案化导电特征部109(也称为第二绕组)形成的次级绕组。层压磁性组合件110包括多级层压结构112中的第一图案化导电特征部111(也称为第一绕组)。在所示示例中,多级层压结构112包括形成变压器的初级绕组和次级绕组的多个导电特征部。第一图案化导电特征部111在第一层级(例如,下面的图16

‑

图18)中具有多个线匝以形成第一绕组(例如,隔离变压器的初级绕组)。多级层压结构112包括第二图案化导电特征部109,该第二图案化导电特征部109在不同层级中具有多个线匝以形成第二绕组(例如,变压器次级绕组)。多级层压结构112还包括与第一图案化导电特征部111间隔开并且位于第一导电特征部111的最外侧线匝和与第二电压域相关联的器件100的一侧之间的导电保护迹线113。这有助于保持与层压结构112内侧的第一(例如,初级)绕组和第二(例如,次级)电路的引线之间的第一和第二域电压差相关联的高电场。在其它实施方式中,可以省略保护迹线113。

32.示例多级层压结构112包括第一导电屏蔽迹线111s,该第一导电屏蔽迹线111s在第一图案化导电特征部111和第二图案化导电特征部109之间的第二层级中具有多个线匝。导电屏蔽迹线111s耦合在第一电路161中。图1

‑

图6中的示例多级层压结构112还包括第二导电屏蔽迹线109s,该第二导电屏蔽迹线109s在第一图案化导电特征部111和第二图案化导电特征部109之间的另一层级中具有多个线匝。在图1

‑

图6的示例中,第二导电屏蔽迹线109s耦合至第二电路162中的导电保护迹线113。在另一示例中,省略第二导电屏蔽迹线109s。

33.磁性组合件110还包括一个或多个磁芯结构以便于结合图案化导电特征部111形成磁路。图示的示例包括如在图1、图2、图5和图6中可见的第一(下部或底部)磁芯结构114。第一磁芯结构114附接至层压结构112的第一侧。电子器件100包括电连接件,诸如在某些部件和引线之间形成电互连件的键合线115、116、117、118和119。封装电子器件100还包括封装结构120,该封装结构120包封导电管芯附接焊盘104和108、半导体管芯102和106、磁性组合件110以及器件100的全部或部分导电引线。在一个示例中,封装结构120是或者包括模制材料,诸如塑料。在另一示例中,封装结构120是或者包括陶瓷材料。

34.磁性组合件110还包括第二(上部或顶部)磁芯结构121(在图1、图2、图5和图6中可

见)。第一磁芯结构114附接到层压结构112的第一侧,而第二磁芯结构121附接到层压结构112的第二侧。在一个示例中,第一磁芯结构114具有与第二磁芯结构121相同的尺寸。在另一示例中,第一磁芯结构114大于第二磁芯结构121。在另一示例中,第一磁芯结构114小于第二磁芯结构121。在一个示例中,磁芯结构114和121中的一个或两者是使用环氧树脂膏附接的预制磁芯。在另一示例中,磁芯结构114和121中的一个或两者是使用厚磁膏层制造的。层压磁性组合件110附接至与第二导电管芯附接焊盘108成一整体的支撑结构122。在另一实施方式中,磁性组合件110被安装到支撑结构(未示出),该支撑结构与第一管芯附接焊盘104和第二管芯附接焊盘108分离并间隔开。

35.第一组电连接件包括第一组键合线115和116,该第一组键合线115和116耦合第一导电屏蔽迹线111s(如果包括的话)、第一半导体管芯102、第一图案化导电特征部111和器件100的第一(例如,高压初级)电路161中的一组第一导电引线124

‑

131中的至少一个第一导电引线。如图1中最佳示出的,第一导电管芯附接焊盘104直接耦合至单个第一引线125。在其它示例中,第一管芯附接焊盘104直接耦合至多个导电第一引线。在示例器件100中,管芯附接焊盘104和引线125是单个连续金属结构,诸如铜或铝。第一键合线115将第一半导体管芯102的导电特征部(例如,键合焊盘)耦合至第一引线126,并且键合线116将第一半导体管芯102的另外的键合焊盘耦合至第一图案化导电特征部111的第一端和第二端,并且还将第一半导体管芯102的接地参考节点耦合至第一导电屏蔽迹线111s。

36.在该示例中,第二组电连接件包括第二组键合线117、118和119,该第二组键合线117、118和119耦合第二导电屏蔽迹线109s(如果包括的话)、第二半导体管芯106、第二图案化导电特征部109、导电保护迹线113(如果包括的话)以及与第一电路161隔离的第二电路162(例如,较低电压次级电路)中的一组第二导电引线132

‑

139中的至少一个第二导电引线。第二导电管芯附接焊盘108直接耦合到单个引线138,并且连接的支撑结构122直接连接到单个引线132。在其它示例中,第二管芯附接焊盘108和/或支撑结构122直接耦合到多个导电引线。在示例器件100中,第二管芯附接焊盘108、支撑结构122以及引线132和138是单个连续金属结构,例如铜或铝。键合线117将第二半导体管芯106的键合焊盘耦合至第二引线137。键合线118将第二半导体管芯106的另外的键合焊盘耦合至第二图案化导电特征部的第一端和第二端。此外,键合线119将第二半导体管芯106耦合至第二导电屏蔽迹线109s和导电保护迹线113。

37.如图2

‑

图4和图6中最佳示出的,封装结构120包封管芯附接焊盘104和108以及相关联的支撑结构122。此外,封装结构120包封导电引线124

‑

139的内部部分。在一个示例中,导电引线124

‑

139是所谓的鸥翼引线,该鸥翼引线如图2

‑

图4和图6中所示从封装结构120向下和向外延伸。在其它示例中使用了不同类型和形状的导电引线(例如,j引线)。图2

‑

图4示出沿图1和图5中的线2

‑

2、3

‑

3和4

‑

4截取的封装电子器件100的相应截面视图。如图2

‑

图4中最佳示出的,示例封装结构120包括顶侧211和相对的底侧212。

38.多级层压结构112具有面向第一导电引线124

‑

131的第一侧141和面向第二导电引线132

‑

139的第二侧142。在该取向中,导电保护迹线113与由第一图案化导电特征部111形成的第一绕组和第二导电引线132

‑

139间隔开并位于它们之间。封装结构120具有沿第一方向(例如,图1

‑

图6中的x方向)彼此间隔开的相应第一侧151和第二侧152。第一导电引线124

‑

131沿着封装结构120的第一侧151定位并向外延伸,而第二导电引线132

‑

139沿着封装

结构120的第二侧152定位并向外延伸。导电保护迹线113与第一图案化导电特征部111和封装结构120的第二侧152间隔开并位于它们之间。如图1和图6中所示,导电保护迹线113沿垂直的第二方向(例如图1

‑

图6中的y方向)具有长度143,并且第一图案化导电特征部111的最外侧线匝沿第二方向具有较短的长度144。

39.在电子器件100的操作中,第一图案化导电特征部111的电压可以远高于沿着封装结构120的第二侧152的第二导电引线132

‑

139的电压。第二导电引线132

‑

139的内部部分由封装结构120的模制化合物或陶瓷材料包封,该模制化合物或陶瓷材料具有比多级层压结构112的层压层或层级的介电常数更低的介电常数。此外,第二导电引线132

‑

139的外部部分暴露于环境空气,该环境空气具有比封装结构120和多级层压结构112的介电常数更低的介电常数。导电保护迹线113在多级层压结构112内的较长长度和定位有助于保持多级层压结构112的高介电材料中的高电场,以减轻或避免在封装电子器件100的生产测试和正常操作期间的电弧放电。

40.图7示出用于制造诸如图1

‑

图6的器件100的封装电子器件的方法700,而图8

‑

图13示出根据方法700进行制造的示例封装电子器件100。方法700包括在701处制造具有导电屏蔽迹线的层压磁性组合件。在某些实施方式中,磁性组合件被单独组装并作为输入提供给方法700。在图示的示例中,在701处的磁性组合件制造包括在702处将底部磁芯(例如,片材)附接至多级层压结构的背面上。图8示出一个示例,其中执行将第一(下部或底部)磁芯结构114附接至示例多级层压结构112的底侧的附接工艺800。

41.多级层压结构112可以是具有图案化导电特征部109和111(诸如变压器绕组)和导电保护迹线113的任何合适的多层层压体。图案化导电特征部109、111和113可以通过任何合适的工艺(诸如将导电材料丝网印刷到层压层上)来产生。多级层压结构112可以包括一个或多个键合步骤以将层压层或片材彼此键合以形成多级层压结构112。在一个示例中,层压结构层级分别包括双马来酰亚胺三嗪(bt)层压层,并且一个、一些或所有层级包括图案化导电特征部(例如,铜或其它导电材料),诸如形成绕组或绕组线匝的迹线。在一些示例中,多级层压结构112是逐层构建的,例如,从中央或中间介电层(例如,核心介电层)开始,并且每一层添加有任何图案化的铜导电特征部和导电通孔以互连不同层级的导电特征部,从而形成多级层压结构112。为了高电压隔离,多级层压结构112的各个层级是或包括高压bt层压材料,该高压bt层压材料提供高电压击穿强度并且可以用树脂(诸如环氧树脂)预浸渍。可以使用任何合适的粘合剂以任何所需的固化(诸如通过加热和压力的组合固化)来组装各个bt层压层。

42.在一个示例中,磁芯结构114是磁片材结构,但是不是所有可能的实施方式都需要这样。附接工艺800可以包括将环氧树脂或其它粘合剂沉积到多级层压结构112的底表面和/或磁芯结构114的表面上。在一个示例中,粘合剂是印刷的磁性油墨环氧树脂,但是在其它示例中可以使用非磁性的粘合剂。附接工艺800还包括使核心结构114与多级层压结构112的底侧接触和/或与形成在其上的环氧树脂接触。在一个示例中,附接工艺800还包括任何必要的固化步骤(例如,热、光、紫外线(uv)等)。

43.方法700在704处继续,在层压结构的前侧上附接顶部磁芯(例如,片材)。图9示出一个示例,其中执行将第二(上部或顶部)磁芯结构121附接至层压结构112的第二侧的第二附接工艺900。附接工艺900可以是与用于将第一磁芯结构114附接至层压结构112的第一附

接工艺800相同或相似的工艺。通过环氧树脂或其它合适的附接结构和/或技术将相应的上部磁芯结构121和下部磁芯结构114附接至多级层压结构112以形成磁性耦合的变压器设备。在其它示例中,可以省略上部磁芯结构121或下部磁芯结构114中的一个,而剩余的磁芯结构为器件100的变压器提供磁性耦合。

44.方法700进一步包括在706处分离(例如,分割(singulating))磁性组合件。在一个示例中,磁性组合件工艺被用于同时制造多个层压磁性组合件,诸如使用单个大型多级层压结构112,以及将一个或多个磁芯结构114、121附接至其相对侧。图10示出一个示例,其中此类大型层压结构112被划片或切割以将各个层压磁性组合件110从初始整体结构中分割或分离。在图10的示例中执行分割过程1000,其例如使用锯刀、蚀刻、激光切割等将多个层压磁性组合件110从起始整体结构中分割或分离。

45.在708处,将磁性组合件110附接至支撑结构122。在一个实施方式中,708处的附接包括将磁性组合件110附接至支撑结构122,其中多级层压结构112的第一侧141面向第一导电引线124

‑

131,并且多级层压结构112的第二侧142面向第二导电引线132

‑

139。在该示例中,708处的附接还包括将磁性组合件110定向成使得导电保护迹线113(如果包括的话)与多级层压结构112的第一绕组111和第二导电引线132

‑

139间隔开并且位于它们之间。

46.在一个示例中,提供了一种引线框架结构,其包括导电引线(例如,上面图1

‑

图6中的124

‑

139)和导电管芯附接焊盘104和108。在一个实施方式中,在粘性胶带或其它粘合剂载体上提供该引线框架结构,其中各种组成结构以预定的相对布置组装以促进方法700中的后续组装步骤。图11示出一个示例,其中执行将磁性组合件110的多级层压结构112附接至支撑结构122的相应表面的附接工艺1100。可以使用任何合适的附接工艺1100,诸如施加粘合剂,连结组合件,以及任何必要的固化。在另一示例中,可以在708处将多级层压结构112的导电特征部焊接到支撑结构122。

47.工艺700在图7中的710和712处继续,例如使用粘合剂或焊接将半导体管芯附接至相应的管芯附接焊盘。图12示出一个示例,其中执行将第一半导体管芯102附接至第一管芯附接焊盘104的管芯附接工艺1200(例如,其中管芯附接焊盘104是包括引线125的一个连续导电结构)。在712处,工艺1200还将第二半导体管芯106附接至相应的第二管芯附接焊盘108(例如,也包括引线138的一个连续导电结构)。

48.方法700还包括在714处的电连接处理(例如,线键合)。图13示出一个示例,其中执行线键合工艺1300,该工艺在半导体管芯和磁性组合件110的一个或多个导电引线和/或导电特征部之间形成连接(例如,上面图1

‑

图6中的键合线115

‑

119),以形成第一电路161和第二电路162。在图13所示的截面视图中,连接工艺1300包括在第一半导体管芯102的第一导电特征部和导电引线126之间形成第一键合线连接件115,以及在第二半导体管芯106的第一导电特征部和导电引线137之间形成键合线连接件117。在另一示例中,形成不同的电连接件以创建第一电路161,诸如倒装芯片处理以在电路中将结构的焊球、导电柱、键合焊盘等互连在一起。电连接工艺1300耦合第一半导体管芯102、多级层压结构112的第一绕组111、多级层压结构112的第一导电屏蔽迹线111s以及第一电路161中的一组第一导电引线124

‑

131中的至少一个第一导电引线。

49.此外,电连接工艺1300耦合第二半导体管芯106、多级层压结构112的第二绕组109、第二导电屏蔽迹线109s以及与第一电路隔离的第二电路中的一组第二导电引线132

‑

139中的至少一个第二导电引线。在一个示例中,电连接工艺1300将第二导电屏蔽迹线109s耦合至任何包括的导电保护迹线113。在一个示例中,电连接工艺1300将第一导电屏蔽迹线111s耦合至第一电路161的接地参考节点,并且将第二导电屏蔽迹线109s耦合至第二电路162的第二接地参考节点(例如,下面的图23)。可以在714处为特定设计做出进一步的连接件,例如以形成图1

‑

图6中所示的键合线115

‑

119。

50.在一个示例中,线接合工艺1300将多级层压结构112的第一导电屏蔽迹线111s耦合至第一电路161。在一个实施方式中,线接合工艺1300将多级层压结构112的第二导电屏蔽迹线109s耦合至第二电路162。此外,在一个示例中,线接合工艺1300将导电保护迹线113耦合至多级层压结构112的第二导电屏蔽迹线109s。在另一示例中,形成不同的电连接件以创建第一电路161,诸如倒装芯片处理以在第二电路中将结构的焊球、导电柱、键合焊盘等互连在一起。在某些示例中,可以使用支撑结构来执行714处的线键合或其它互连处理,以便在键合线附接期间为磁性组合件110的一个或多个特征提供机械结构支撑。在一个示例中,磁芯结构114和121中的一个或两者可以在键合线焊接操作期间由定制键合线夹持工具(未示出)支撑。在一个示例中,键合线夹持工具可以包括用于支撑延伸超出被支撑的磁芯结构的层压键合焊盘区域的腔体。

51.方法700在716处继续形成最终封装结构120。在一个示例中,在716处的封装包括执行形成封装结构120以包封管芯102和106、导电管芯附接焊盘104和108、支撑结构122、磁性组合件110、电连接件(例如,键合线115

‑

119)和导电引线124

‑

139的一些部分的模制工艺(未示出)。上面的图1

‑

图6示出在图7中的716处形成的示例模制塑料封装结构120。在另一示例中,可以在716处形成陶瓷封装结构。在图7中的718处,可以执行进一步的后端处理,诸如引线形成和修整等。

52.图14

‑

图18示出示例多级层压结构112的进一步细节。图14示出具有第一绕组和第二绕组以及导电保护迹线的多级层压结构112的仰视图,而图15示出磁性组合件110的仰视图,其中多级层压结构112和相应的上磁芯114和下磁芯121附接。图16

‑

图18示出沿图15的16

‑

16线截取的磁性组合件110的三个不同实施例的局部截面端视图。多级层压结构112是多层结构,其具有形成变压器的一些部分的图案化导电特征部109、109s、111、111s和113。在一个示例中,第一图案化导电特征部111形成变压器初级绕组,第二图案化导电特征部109形成变压器次级绕组。在一个示例中,另外的图案化导电特征部形成一个或多个第二次级绕组、一个或多个导电(例如,法拉第)屏蔽件、一个或多个感测线圈以及一个或多个导电屏蔽迹线和导电保护迹线113。

53.在一个示例中,图案化导电特征部在多级层压结构112的多个层级(例如,层)上具有部件,但是不是所有可能的实施方式都需要。在一个示例中,各个初级和/或次级绕组的图案化绕组线匝在多级层压结构112的不同层上延伸,但是并非所有可能的实施方式都需要。示例图案化绕组特征包括在多级层压结构112的各个层上的呈现螺旋图案的多个线匝,但是其它实施方式也是可能的,诸如在相应层上的单线匝绕组结构。形成变压器绕组109和111、屏蔽件109s和111s以及保护迹线113的示例图案化导电特征部包括允许绕组互连到器件100的引脚或半导体管芯的导电端连接特征,诸如用于键合线连接件115

‑

119或封装电子器件100中的其它导电互连类型(例如,焊球,未示出)。半导体管芯102和106包括柱、焊料凸块、导电焊盘或其它导电特征部(例如,键合焊盘),它们可以使用键合线115

‑

119或通过使

用任何合适的电互连技术(例如,线键合、倒装芯片附接等)的直接焊接电互连到其它结构。

54.图16

‑

图18示出多级层压结构112的示例实施方式的外部部分,为了清楚起见省略了内部部分或中心部分。如图16

‑

图18中所示,多级层压结构112具有沿x方向彼此间隔开的第一侧141和相对的第二侧142,以及z方向的层级(例如,层)1601

‑

1607的堆叠。多级层压结构112具有附接至磁芯121的第三侧1613和附接至磁芯114并沿z方向与第三侧1613间隔开的第四侧1614。第一图案化导电特征部111包括在第一层级1601中的多个线匝以形成第一绕组,并且第二图案化导电特征部109在两个不同层级1606和1607中具有多个线匝以形成第二绕组。在该示例中,第二导电屏蔽件109s被形成在第五层级1605中,并且层级1603和1604形成初级电路和次级电路之间的隔离屏障。在图16的示例中,导电保护迹线113和第一导电屏蔽件111s被形成在第二层级1602中,其中导电保护迹线113与第一图案化导电特征部111和多级层压结构112的第二侧142间隔开并位于它们之间。图17示出另一示例,其中导电保护迹线113被形成在第一层1601中,与第一图案化导电特征部111和多级层压结构112的第二侧142间隔开并位于它们之间。在图18的示例中,导电保护迹线113被形成在相应的第一层级1601和第二层级1602中,并且导电保护迹线113与第一图案化导电特征部111和多级层压结构112的第二侧142间隔开并位于它们之间。

55.图16

‑

图18的示例中的第一导电屏蔽迹线111s在与第一图案化导电特征部111和第二图案化导电特征部109间隔开并位于它们之间的第二层1602中具有多个线匝。在这些示例中,第二导电屏蔽迹线109s在第一图案化导电特征部111和第二图案化导电特征部109之间的另一层级1605中具有多个线匝。另外,第二导电屏蔽迹线109s与导电屏蔽迹线111s间隔开。在替代实施方式中,保护迹线113可以从图16

‑

图18的示例中省略。图16

‑

图18的实施例为初级电路161和次级电路162提供具有相应的第一屏蔽件111s和第二屏蔽件109s的双屏蔽实施方式。

56.还参考图19

‑

图22,其示出了几个进一步的屏蔽迹线示例。图19示出沿图15的线16

‑

16截取的磁性组合件110的第四实施例的局部截面端视图。该示例是单个屏蔽件,其中耦合在第五层级1605中的第二(例如,次级)电路162中的第二导电屏蔽迹线109s沿z方向与相应的第一导电迹线109和第二导电迹线111的线匝间隔开并位于它们之间。在该示例中,次级线圈迹线109在相应的第六层级1606和第七层级1607中延伸。第二导电屏蔽迹线109s在第五层级1605中具有线匝,这些线匝与次级线圈迹线109间隔开并且与次级线圈迹线109大致共同延伸。

57.图20示出沿图15的线16

‑

16截取的磁性组合件110的双屏蔽示例。该示例提供双外围屏蔽迹线109s和111s以及相应的第一导电迹线109和第二导电迹线111的相应层级中的外围屏蔽迹线。该示例进一步包括第二层级1602中的保护迹线113,其可以在另一实施方式中被省略。在图20的示例中,导电屏蔽迹线111s包括从第一层级1601中的第一图案化导电特征部111的最外侧横向范围沿x方向横向向外间隔开的线匝。如图20中所示,第一导电迹线109和第二导电迹线111沿着横向宽度尺寸2001占据磁性组合件110的中心部分,并且导电屏蔽迹线109s和111s的外围线匝与图案化导电特征部111和109的最外侧横向范围间隔开非零距离2002。该示例中的第二导电屏蔽迹线109s包括在层级1605和1606中与第二图案化导电特征部109的最外侧线匝横向向外间隔开的线匝。在该实施方式中,如图20中所示,导电屏蔽迹线109s和111s的外围线匝横跨层级1603、1604和1605的电介质彼此面对,并形

成一个或多个寄生电容器2000。如下面图25中示意性所示,一个或多个寄生电容器2000(cp)通过在隔离的第一电路161和第二电路162之间提供电容阻抗来促进emi降低。此外,图20的示例提供交错屏蔽迹线,其中第六层级1606中的第二导电屏蔽迹线109s与第二图案化导电特征部109的线匝交错。

58.图21示出沿图15中的线16

‑

16截取的磁性组合件110的第六实施例。该示例还提供交错屏蔽迹线配置,其中第二图案化导电特征部109和第二导电屏蔽迹线109s两者的线匝被形成在第五层级1605和第七层级1607中。图22的示例磁性组合件110提供交错的外围屏蔽件,并且第一层级1601和第二层级1602两者包括第一图案化导电特征部111以及第一导电屏蔽迹线111s的线匝。此外,层压结构层级1605、1606和1607各自包括第二图案化导电特征部109和第二导电屏蔽迹线109s两者的线匝。此外,像上面图20的示例一样,导电屏蔽迹线111s和109s各自包括与第二层级1602和第五层级1605中的相应图案化导电特征部111和109的最外侧线匝横向向外间隔开的线匝,以提供一个或多个相应的寄生电容器2000。

59.图23

‑

图25示出第一电路161和第二电路162的三个示例电互连件。图23提供了示出一个示例的示意图2300,其中第一导电屏蔽迹线111s耦合至第一电路161的第一接地参考节点。如图23中示意性示出的,第一导电屏蔽迹线111s在形成变压器的初级绕组和次级绕组的第一导电特征部111和第二导电特征部109之间延伸。图23的示意图2300还示出了第一电路161和第二电路162的示例电路部件。在该实施方式中,输入电压源2302向参考第一电路161的接地参考节点2306的输入节点2304提供输入电压vin。输入电容器ci耦合在输入节点2304和第一接地参考节点2306之间。一对交叉耦合的pmos晶体管2311和2312具有耦合至输入节点2304的源极以及耦合至初级绕组111的相对端(第一图案化导电特征部111的端部)的漏极。开关nmos晶体管2313和2314分别耦合在相应的晶体管2311和2312的漏极与第一接地参考节点2306之间。次级电路162在参考第二电路162的第二接地参考节点2326的输出端子2324处提供输出电压vo。输出电容器co耦合在端子2324和2326之间。第二电路162还包括一对交叉耦合的pmos晶体管2331和2332,它们各自耦合在输出节点2324和次级绕组109的相应端部(第二图案化导电特征部109)之间。nmos晶体管2333和2334各自耦合在相应的pmos晶体管2331和2332的漏极与第二接地参考节点2326之间。

60.图24示出图1

‑

图6的封装电子器件的另一实施例的示意图2400,其中第二导电屏蔽迹线109s耦合至第二电路162的第二接地参考节点2326。图23和图24提供了第一电路161和第二电路162的单屏蔽互连件,其在初级绕组111和次级绕组109之间具有用于emi控制或降低的接地参考屏蔽。在一个模拟示例中,提供图23或图24中的单侧法拉第屏蔽可提供3

‑

5db的emi降低。

61.图25示出图1

‑

图6的封装电子器件的双屏蔽实施例的示意图2500,其中第一导电屏蔽迹线111s和第二导电屏蔽迹线109s位于初级绕组111和次级绕组109之间。此外,图25中的双屏蔽迹线111s和109s提供耦合至第一电路161和第二电路162的相应第一接地参考节点2306和第二接地参考节点2326的寄生电容器cp(例如,上面图20和图22中的电容器2000)。在该实施方式中,第一导电屏蔽迹线111s耦合至第一电路161的接地参考节点2306,并且第二导电屏蔽迹线109s耦合至第二电路162的第二接地参考节点2326。在一个模拟示例中,图25中的双法拉第屏蔽提供大约10

‑

12db的emi辐射降低。

62.所描述的示例为具有集成emi降低特征的封装电子器件提供了集成磁体,而没有

增加成本并且没有用于隔离dc到dc转换器或其它应用的外部电路或部件。此外,由于不需要附加的板级电路部件,因此降低emi与终端用户的设计专业知识无关。在各种实施方式中,导电屏蔽迹线在多级层压结构112的一个或多个层级上被图案化,并且在制造中的线键合或其它电互连工艺期间,它们可以连接到相关联的第一或第二电路,诸如连接到其接地参考节点。各种实施方式提供在变压器线圈之间的单层屏蔽、位于变压器线圈之间或外围例如用于创建一个或多个寄生电容器的双屏蔽,以及交错屏蔽。在操作中,交错屏蔽示例提供了双屏蔽配置的最优emi降低性能和提供高耦合的单屏蔽示例之间的临时选项。某些示例中的屏蔽线圈可以围绕电源线圈定位。在其它实施方式中,导电屏蔽迹线提供块电容器(block capacitor)屏蔽。块电容器屏蔽形成在不同层级中的电容器极板,这些极板由一个或多个介电层隔开,其中相应的电容器极板连接到第一电路和第二电路中的相应电路,并且电容器极板结构可以但不需要形成围绕功率线圈的线匝,以便通过增加电容(例如,上面图20和图22中的电容器2000)来解决近场辐射。所描述的示例还提供了解决电磁干扰的封装级解决方案,并且可以单独使用或与外部电路部件和/或基于硅的解决方案(如ssm)结合使用。此外,所描述的示例提供独立于硅工艺节点和/或系统级板设计的集成emi解决方案。

63.在权利要求的范围内,对所描述的实施例进行修改是可能的,并且其它实施例也是可能的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1