带有暴露的夹的电子器件倒装芯片封装的制作方法

带有暴露的夹的电子器件倒装芯片封装

背景技术:

1.电子电路容易受到由寄生电感引起的效率降低和操作性能下降的影响,尤其是在较高的操作频率下。高频器件在升高的操作温度下也会降低效率。仅通过印刷电路板(pcb)进行底侧冷却的常规器件封装的热限制阻止了器件尺寸的减小并抑制了器件功率密度的增加。此外,通过将包括一个或多个电源电路开关晶体管的半导体管芯的背侧接地,增强了开关电路的良好电性能。当前采用线键合管芯和引线框架的封装解决方案存在高寄生电感问题,并且无法提供顶侧冷却或背侧管芯接地。带盖嵌入式管芯封装具有在顶侧上带有用于散热的盖子的倒置管芯或倒装芯片,但不提供顶侧接地连接。其他倒装芯片途径没有实现到管芯背侧的接地连接。在具有再分布层(rdl)的嵌入式管芯上具有直接镀铜层的其他封装是昂贵的。

技术实现要素:

2.描述了一种封装的电子器件,其具有附接到多层衬底的导电夹和倒置管芯,以及包围导电夹的一部分和半导体管芯的封装结构。描述的示例提供具有良好管芯散热和电性能的节省成本的电子器件封装解决方案。描述的示例封装的电子器件包括多层衬底,该多层衬底具有带有第一导电结构的第一层和带有第二导电结构的第二层。该示例器件还包括具有电子部件的半导体管芯。该管芯包括导电特征件,导电特征件电连接到电子部件的端子并直接连接到第一层的对应导电结构。示例器件还包括直接连接到第一层的第一导电结构中的一个导电结构的导电夹。导电夹直接连接到半导体管芯的一侧。示例器件还包括包围导电夹的一部分和半导体管芯的封装结构。

3.在某些示例中,多层衬底包括在第一层与第二层之间的具有导电通孔的第三层或多个中间层,该导电通孔将第一导电结构中的一些导电结构与第二导电结构中的一些导电结构单独连接。第三层还包括将通孔彼此分离的绝缘体结构。在一个示例中,多层衬底是层压结构,其中绝缘体结构包括层压堆积材料。在另一示例中,多层衬底是陶瓷或绝缘金属衬底(ims),其中绝缘体结构包括陶瓷材料。在一个示例中,封装结构包括包围导电夹的一部分和半导体管芯的模制材料。在一个示例中,模制材料在第一层中将第一导电结构中的至少一些导电结构彼此分离,并且在第二层中将第二导电结构中的至少一些导电结构彼此分离。在一个示例中,导电夹被焊接到第一层的第一导电结构中的一个导电结构,并且导电夹被焊接或用环氧树脂胶合(epoxied)到半导体管芯。在一个示例中,器件还包括具有第二导电特征件的第二半导体管芯,该第二导电特征件直接连接到第一层的导电结构中的对应导电结构。

4.描述了一种用于制造电子器件的方法。该方法包括将半导体管芯的第一侧的导电特征件焊接到多层衬底的第一层的第一组导电结构,并且将导电夹附接到多层衬底和半导体管芯。在一个示例中,附接导电夹包括将导电夹的第一部分焊接到第一层的第一侧的另一导电结构,并且将导电夹的第二部分附接到半导体管芯的第二侧。在一个示例中,导电夹的第二部分被焊接到半导体管芯的第二侧。在另一示例中,导电夹的第二部分用环氧树脂

胶合到半导体管芯的第二侧。该方法还包括将导电夹的一部分和半导体管芯包围在封装结构中。在一个示例中,该方法还包括在将导电夹附接到多层衬底和半导体管芯之前,将第二半导体管芯焊接到第二组导电结构。

附图说明

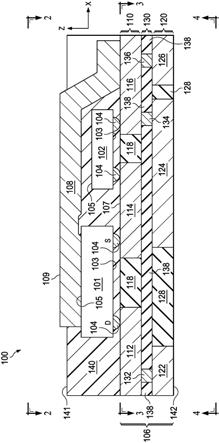

5.图1是倒装芯片封装的电子器件的截面侧视图,该电子器件具有包括多层层压结构的多层层压衬底和暴露的夹。

6.图2是沿着图1中的线2

‑

2截取的封装的电子器件的俯视图。

7.图3是沿着图1中的线3

‑

3截取的封装的电子器件的截面俯视图。

8.图4是沿着图1中的线4

‑

4截取的封装的电子器件的仰视图。

9.图5是制造封装的电子器件的方法的流程图。

10.图6

‑

图12是根据图5的方法正在制造的图1

‑

图4的封装的电子器件的截面侧视图。

11.图13是具有多层陶瓷或绝缘金属衬底和暴露的夹的另一示例倒装芯片封装的电子器件的截面侧视图。

具体实施方式

12.在附图中,相同的附图标记始终指代相同的元件,并且各种特征件不一定按比例绘制。在下面的讨论和权利要求中,术语“包括”、“包含”、“具有”、“含有”、“带有”或其变体旨在以类似于术语“包含”的方式包含在内,并且因此应被解释为意味着“包括但不限于

……”

。此外,术语“耦合”或“耦接”旨在包括间接或直接的电或机械连接或其组合。例如,如果第一器件耦合到第二器件或与第二器件耦合,则该连接可以通过直接电连接,或者通过经由一个或多个中间器件和连接件的间接电连接。

13.图1

‑

图4示出具有第一半导体管芯101和第二半导体管芯102的示例封装的电子器件100。尽管示例器件100包括多个半导体管芯101和102,但是其他示例可以包括单个半导体管芯,或者多于两个半导体管芯。在所示的示例中,两个半导体管芯都包括具有导电特征件104的下部第一表面103,导电特征件104以倒装芯片方式焊接到多层衬底106的导电结构。示例导电特征件104从半导体管芯101和102的下部第一侧103向外(例如,向下)延伸。可以使用可以被焊接或以其他方式直接连接到多层衬底106的铜垫或其他导电结构的任何合适的导电特征件104。在一个示例中,管芯101和102的导电特征件104是焊料凸块。在另一示例中,导电特征件104是铜柱。

14.在一个示例中,管芯101和102被制造为具有一个或多个电子部件(例如,晶体管、电阻器、电容器、二极管等),如下面结合图7进一步讨论的。在一个示例中,第一管芯101包括功率晶体管,诸如高电子迁移率晶体管(hemt),例如碳化硅(sic)晶体管或氮化镓(gan)晶体管。示例管芯101和102还包括一个或多个金属化层,其中上侧103具有从上侧103向外延伸的铜柱、焊料凸块或其他导电特征件104。至少一些导电特征件104经由一个或多个金属化层电连接到管芯101和102内的一个或多个电子部件的端子。在该示例中,管芯101和102被倒置或“倒装”,以使用倒装芯片附接工艺将第一侧103的导电特征件104向下焊接到多层衬底106的导电结构上。在图1中,管芯101和102的倒置定位使管芯的第二侧105面朝上(例如,沿着正z方向)。倒装芯片工艺将管芯101和102直接附接到多层衬底106的第一侧(例

如,上侧)107。导电特征件104到多层衬底106的导电结构的直接电连接有利地减轻或避免了与线键合或其他互连技术相关联的寄生电感。

15.器件100还包括导电夹108。夹108可以是任何合适的导电材料,诸如铝、铜等。导电夹108直接连接到多层衬底106的第一侧107上的一个或多个导电结构。在一个示例中,夹108的下部第一部分被直接焊接到多层衬底106的第一侧107上的一个或多个导电结构。此外,导电夹108直接连接到第一半导体管芯101的第二侧105。在一个示例中,导电夹108的上部第二部分被直接焊接到第一半导体管芯101的第二侧105上的导电特征件。在另一示例中,导电夹108的第二部分用环氧树脂胶合到第一半导体管芯101的第二侧105的一部分。在一个实施方式中,导电夹108被焊接到多层衬底106的第一侧107上的接地导电结构,例如接地连接。

16.还参考图2

‑

图4,图2示出沿着图1中的线2

‑

2截取的封装的电子器件100的俯视图。图1和图2中的导电夹108在第二半导体管芯102的一部分之上延伸,并与其分开。该示例中的夹108提供接地屏蔽,以保护第一半导体管芯101和/或第二半导体管芯102在器件100的操作期间免受电磁干扰(emi),无论是焊接还是用环氧树脂胶合到第一半导体管芯101的第二侧105。在图1的示例中,导电夹108包括暴露于封装的电子器件100外部的上部第一侧109。夹108还用于促进从附接的第一半导体管芯101散热。在使用中,散热器(未示出)可以被焊接、用环氧树脂胶合或以其他方式附接到导电夹108的暴露的第一侧109,以进一步促进散热。

17.图1中的示例多层衬底106是多层层压衬底结构。在另一实施方式中(例如,下面的图13),多层衬底106是陶瓷衬底或绝缘金属衬底(ims)。如图1所示,多层层压衬底106包括在第一侧(例如,顶侧)107处的第一层110,以及底部第二层120。多层衬底106有助于信号路由(routing)和互连位置,这些对于引线框架是不可能的或不切实际的。图1的示例还包括中间第三层130。第一层110包括第一多个导电结构112、114和116,它们延伸穿过第一层110到达多层衬底106的第一侧107。导电结构112、114和116彼此横向分开(例如,沿着图1中的x方向)。此外,导电结构112、114和116通过第一绝缘结构118彼此分离。

18.在图1的示例中,第一导电结构112被焊接到半导体管芯101的第一导电特征件104。在一个示例中,第一半导体管芯101包括晶体管部件(例如,下面图7中的晶体管701),第二半导体管芯102包括晶体管驱动器电路(未示出)。在该示例中,半导体管芯101的第一导电特征件104电连接到晶体管的漏极端子(在图1中标记为“d”)。第一层110的第二导电结构114被焊接到半导体管芯101的第二导电特征件104,并且第三导电结构116被焊接到导电夹108的第一部分。在图1的示例中,半导体管芯101的第二导电特征件104电连接到晶体管的源极端子(在图1中标记为“s”)。在一个示例中,驱动器电路管芯102将晶体管管芯101的源极端子连接到电路接地节点或其他参考电压节点,并且第二管芯102的对应接地导电特征件104被焊接到第三导电结构116。

19.在所示示例中,导电夹108的第一部分被直接焊接到多层衬底106的第一侧107上的第三导电结构116。以这种方式,导电夹108直接电连接到电路接地,并且为管芯101和102提供接地屏蔽。此外,在一个示例中,第一半导体管芯101包括在第二侧(例如,上侧)105上的上主体触点(图1中未示出,下面在图7中示出),并且主体触点被焊接到导电夹108的第二部分。在该实施方式中,导电夹108提供到半导体管芯101的主体的焊接直接电接地连接。

20.图3是沿着穿过第一层110的线3

‑

3截取的截面俯视图,并且图4是示出沿着图1中的线4

‑

4截取的封装的电子器件的第二层(例如,底层)120的特征件的仰视图。第二层120包括第二多个导电结构122、124、126和128。导电结构122、124、126和128延伸穿过多层衬底106的第二层120。第二多个导电结构包括第四导电结构122、第五导电结构124和第六导电结构126。第四导电结构122通过多层衬底106的第三层130电连接到第一层110的第一导电结构112。第五导电结构124通过第三层130电连接到第三导电结构116。图示的示例第二层120还包括第六导电结构126。第六导电结构126通过第三层130电连接到第三导电结构116。

21.第三层130包括在第一层110与第二层120之间延伸的导电通孔132、134和136。通孔132、134和136可以是任何合适的导电材料,诸如铝、铜等。第三层130还包括将导电通孔132、134和/或136中的至少一些彼此分离的绝缘体结构138。在图1

‑

图4的层压衬底示例中,第三层130的绝缘体结构138包括层压堆积材料138。在所示的示例中,多层衬底106的绝缘体结构118、128和138均由层压堆积材料构成。在一个示例中,堆积材料以片材开始,该片材被压入或以其他方式安装到各个层110、120和130的导电结构或通孔之间的间隙中。这种技术被称为干膜层压。在一个示例中,绝缘体结构118、128和138以及组成的堆积材料片材是有机材料或包括有机材料。

22.封装的电子器件100还包括封装结构140。封装结构140可以是用以包围器件100的所有或部分部件的任何合适的封装材料,例如,模制塑料材料、陶瓷材料等。封装材料包括第一侧(例如,顶侧)141。在图1的示例中,导电夹108的第一侧109竖直延伸超过封装材料140的第一侧141,从而允许从夹108散热和/或允许外部散热器(未示出)附接到器件100。封装的电子器件100还包括第二侧(例如,底侧)142,其中图1示出了第二多个导电结构122、124和126的暴露的部分。在使用中,封装的电子器件100的第二侧142的暴露的导电结构122、124和126被焊接到主机pcb(未示出),以提供从主机pcb的电路到由半导体管芯101、102和多层衬底106形成的电路的电连接。

23.第三层130的导电通孔132、134和136将第一层110的导电结构112、114和116中的一些与第二层120的导电结构122、124和126中的一些单独连接。在图1的示例中,第一通孔132通过第一层110的第一导电结构112将第一半导体管芯101的晶体管漏极直接电连接到第二层120的第四导电结构122。在该示例中,第四导电结构122在可以焊接到pcb(未示出)的封装的电子器件100的底侧142处提供漏极连接。第三层130的第二通孔134将来自第三导电结构116的接地节点电连接到第二层120的第五导电结构124。此外,第三层130的第三通孔136将来自第三导电结构116的接地节点电连接到第六导电结构126。导电结构124和126在可以被焊接到用户pcb的器件100的底侧142处提供接地连接或源连接。

24.图1中的器件100的截面侧视图是沿着图2

‑

图4中的线1

‑

1截取的,并且未示出示例多层衬底106的所有特征。图3示出第一层110的示例俯视截面图,其包括第一导电结构112(标记为“d”),第一导电结构112的一部分延伸到第一层110的横向边缘。第一层110的示例第二导电结构114的左侧比右侧宽,以在第一半导体管芯101与第二半导体管芯102(图1)之间提供源极连接(标记为s)。第一层110还包括导电结构300(标记为“g”),其在驱动器电路管芯102与第一半导体管芯101中的晶体管的栅极端子之间提供栅极控制信号互连。该示例中的晶体管栅极端子通过焊接到导电结构300的顶表面的第一半导体管芯101的对应导电特征件(未示出)连接。该示例中的第二半导体管芯102包括栅极控制信号输出端,其具有焊

接到导电结构300的第二端的对应导电特征件(未示出)。导电结构300允许驱动器管芯102提供栅极控制信号以操作第一半导体管芯101的晶体管。图3还示出为导电夹108提供接地节点连接的第三导电结构116。此外,第一层110包括另一导电结构302,以促进连接到驱动器管芯102中的其他电路,以及将信号路由到驱动器管芯102中的其他电路或者从驱动器管芯102中的其他电路路由信号。

25.图4示出封装的电子器件100的第二层120的仰视图。第二层120包括第四导电结构122,其在封装的电子器件100的底侧142处提供漏极连接。第二层120的底侧还包括第五导电结构124(例如,接地节点连接)和第六导电结构126(例如,另一接地节点连接)。图4中的示例第二层120还包括另一导电结构400的暴露的部分。

26.示例封装的电子器件100有利地将多层衬底106与一个或多个以倒装芯片方式焊接的管芯101和102以及解决先前封装配置的各种热和电缺点的导电夹108相结合。示例器件100的各种特征可以与gan、sic或其他hemt晶体管电路结合使用,以结合与高功率密度和低成本相关联的优点来改善高频操作。在某些实施方式中,器件100促进倒装芯片gan管芯101和驱动器电路102的封装,而没有先前与键合线相关联的寄生电感。

27.描述的器件100还提供了附接到管芯101的背侧的暴露的导电夹108以通过顶侧冷却改善散热,以及附接到第一管芯101的背侧105的接地夹以获得良好的电性能。这代表了相对于在倒装芯片封装中未实现到管芯背侧的接地连接的其他解决方案的显著改进。与具有再分布层特征的嵌入式管芯封装解决方案相比,器件100还提供了显著的成本优势。此外,与引线框架技术相比,多层衬底106的使用有利地促进了复杂的互连路由能力。此外,示例多层层压结构106促进低的电寄生,以进一步改善高频电路应用。此外,示例器件100结合接地背侧连接提供良好的散热,这是使用带盖的ccc封装不可能实现的。如下面结合图13进一步讨论的,多层衬底106可以使用各种不同的构造来实现,包括多层层压衬底(例如,图1

‑

图4)、陶瓷衬底或绝缘金属衬底(例如,ims,图13)。

28.现在参考图5

‑

图12,图5示出用于制造封装的电子器件的示例方法500。在一个示例中,方法500可以用于制造上述图1

‑

图4的示例封装的电子器件100。方法500可以用于制造其他封装的电子器件,诸如下面结合图13描述的示例器件。下面结合示例器件100的制造来描述方法500,图6

‑

图12示出根据方法500正在制造的封装的电子器件100。

29.示例方法500包括在502处的晶片制造,以及在504处在晶片顶部上形成焊料凸块或铜柱。图6示出一个示例,其中执行工艺604以制造包括多个透视管芯区域的晶片600,每个透视管芯区域具有从晶片600的第一侧601向外延伸的一个或多个对应焊料凸块或铜柱导电特征件104。示例晶片600还包括背侧602。

30.方法500还包括在图5中的506处的管芯分离或分割。可以使用任何合适的锯切、激光切割、蚀刻或其他分离处理(未示出)将图6中的管芯600分离成多个半导体管芯(例如,图1中的第一管芯101)。图7示出示例第一管芯100的一部分,其与图6的晶片600分离并经历工艺700,该工艺700在分离的管芯101的第一侧103上形成导电特征件104(例如,铜柱或焊料凸块)的。

31.图7中的示例第一管芯101包括形成在半导体衬底702(例如,硅、氮化镓、碳化硅、绝缘体上硅(soi)等)上和/或中的晶体管部件701。虽然示例第一管芯101包括单个晶体管部件701,但是其他实施方式包括具有形成在管芯101中的多个电子部件的集成电路。在该

示例中,经处理的管芯101包括单独电连接到晶体管部件701的对应端子(源极“s”、漏极“d”、栅极“g”和背栅极触点)的多个导电特征件104。导电特征件104是铝、铜、焊接材料或适合于随后焊接到多层衬底106(例如,图1)的第一层110的导电结构112、114中的对应导电结构的其他导电材料。

32.示例管芯101还包括设置在衬底702的上表面或侧面的选定部分上的隔离结构703。在一些示例中,隔离结构703可以是浅沟槽隔离(sti)特征或场氧化物(fox)结构。示例管芯101还包括设置在衬底702上方的多层金属化结构。金属化结构包括形成在衬底702之上的第一电介质结构层704,以及多层上部金属化结构706、710。在一个示例中,第一电介质结构层704是设置在晶体管701和衬底702的上表面之上的前金属电介质(pmd)层。在一个示例中,第一电介质结构层704包括沉积在晶体管701、衬底702和隔离结构703之上的二氧化硅(sio2)。

33.金属化结构包括从晶体管701的各个端子延伸穿过pmd层704的钨插塞或触点705,以及上面的电介质层706和710,本文称为层间或层级间电介质(ild)层。在不同的实施方式中可以使用不同数量的层。在一个示例中,第一ild层706和最终ild层710由二氧化硅(sio2)或其他合适的电介质材料形成。在某些实施方式中,多层上部金属化结构的各个层以两级形成,包括金属内电介质(imd,未示出)子层和imd子层上面的ild子层。各个imd子层和ild子层可以由任何合适的一种或多种电介质材料形成,诸如基于sio2的电介质材料。

34.第一ild层706和上部ild层710包括在下面的层的顶表面上形成的导电金属化互连结构708和712(诸如铝),以及通孔709(诸如钨),从而提供从单个层的金属化特征件708、712到上面的金属化层的电连接。衬底702、电子部件701、第一电介质结构层704和上部金属化结构706、710形成具有上侧或上表面103的管芯101。顶部金属化层710包括示例导电特征件714,诸如最上面的铝通孔。导电特征件714包括在最上面的金属化层710的顶部处的管芯101的上侧103处的侧面或表面。可以提供任意数量的导电特征件714。一个或多个导电特征件714通过管芯101的金属化结构与晶体管701电耦合。

35.在一个示例中,上部ild电介质层710被一个或多个钝化层716(例如,保护性外涂层(po)和/或钝化层)(例如,氮化硅(sin)、氮氧化硅(sio

x

n

y

)或二氧化硅(sio2))覆盖。在一个示例中,一个或多个钝化层716包括一个或多个开口,该开口暴露导电特征件714的一部分,以允许特征件714电连接到对应触点或导电特征件104。导电特征件104从金属化结构的第一侧(例如,上侧)103向外(例如,沿着图7中的负“z”方向向上)延伸。在一个示例中,导电特征件104包括从金属化结构的上侧103向外延伸的导电种子层,诸如铜。在一个示例中,导电特征件104包括导电柱。在另一示例中,导电特征件104是焊料凸块。图7中的示例管芯101还包括形成在管芯101的第二侧105上的底部导电特征件718(图1中未示出)。

36.方法500在图5中的508处继续,制造或提供多层衬底(例如,上面图1中的106)。在一个示例中,多层衬底106是层压衬底(例如,图1

‑

图4)。在另一示例中,多层衬底在508处被制造为陶瓷衬底或绝缘金属衬底(例如,下面的图13)。图8示出一个示例,其中执行层压工艺800,该层压工艺800产生上面结合图1

‑

图4示出和描述的多层层压衬底106。

37.方法500在图5中的510处继续,将一个或多个管芯附接在多层衬底上。图9示出一个示例,其中执行倒装芯片管芯附接焊接工艺900,该工艺将半导体管芯101的第一侧103的导电特征件104焊接到示例多层层压衬底106的第一层110的第一组导电结构112、114和

116。在该示例中,第一管芯101和第二管芯102同时或分离地倒置并定位在多层层压衬底106的第一侧107上,并且加热器件100以使焊料凸块104的焊接材料回流,以便形成与导电结构112、114和116的焊料接合。

38.在图5中的512处,该方法还包括将导电夹附接到多层衬底和半导体管芯。图10示出一个示例,其中执行附接工艺1000,该附接工艺1000将导电夹108的下部第一部分焊接到第三导电结构116。在一个示例中,附接工艺1000还将导电夹108的上部第二部分焊接到第一半导体管芯101的第二侧105(例如,焊接到图7中的底部导电特征件718)。在该示例中,将导电夹108焊接附接到第一半导体管芯101的第二侧105,提供了通过导电夹108对导电结构116处的接地节点的电体连接。在另一示例中,夹附接工艺1000将导电夹的第二部分用环氧树脂胶合到第一半导体管芯101的第二侧105。在这两个示例中,夹操作为接地屏蔽以保护第一半导体管芯101和第二半导体管芯102的电路。此外,将夹108附接到第一半导体管芯101的第二侧105提供了从管芯101散热的热路径。如前所述,最终用户可以将散热器附接到导电夹108的顶侧109,以进一步促进散热。

39.在图5中的514处,方法500还包括将导电夹108的一部分和半导体管芯101和102包围在封装结构中。图11示出了一个示例,其中执行模制工艺1100,模制工艺1100将器件100的上部结构包围在塑料模制材料140中。在该示例中,模制工艺1100最初为模制封装结构140提供位于导电夹108的顶侧109上方的上表面或顶表面141。

40.在图5中的516处,示例方法500还包括暴露夹108的一部分。图12示出了一个示例,其中执行材料去除工艺1200,材料去除工艺1200去除模制封装结构140的顶表面的一部分,以暴露导电夹108的顶侧109的上部。

41.在另一个可能的示例中,陶瓷封装结构(未示出)可以用于包围半导体管芯101、102的全部或部分以及导电夹108的至少一部分。

42.图13示出另一示例封装的电子器件1300,其包括具有多层陶瓷或绝缘金属衬底1306和暴露的夹的倒装芯片封装。如上所述,器件1300包括第一半导体管芯101和第二半导体管芯102以及导电夹108。在该示例中,多层衬底1306包括第一侧107、第二侧142、第一层1310、第二层1320和第三层1330。第一层1310包括延伸穿过第一层1310到达第一侧107的第一多个导电结构1312、1314和1316,并且第二层1320包括延伸穿过第二层1320到达第二侧142的第二多个导电结构1322、1324和1326。第三层1330包括分别在第一层1310与第二层1320之间延伸穿过第三层1330的导电通孔1332、1334和1336。第三层1300还包括将通孔1332、1334和1336彼此分离的绝缘体结构1338。在该示例中,绝缘体结构1338包括陶瓷材料1338。

43.在一个示例中,第一层1300的导电结构1312、1314和1316被创建为直接键合铜(dbc)衬底,并且第三层1300的陶瓷绝缘体结构1338是电介质材料,其中通孔1332、1334和1336在第一层1310与第二层1320之间提供电互连。此外,在该示例中,封装结构140包括包围导电夹108的上部和半导体管芯101的模制材料。在该示例中,模制材料140还在第一层1310中将第一多个导电结构1312、1314和/或1316中的至少一些彼此分离。此外,图13中的模制材料140在封装的电子器件1300的底部处在第二层1320中将第二多个导电结构1322、1324和1326中的至少一些分离。

44.描述的封装解决方案通过简单且低成本的实施方式来促进良好的热和电性能,实

施方式允许超越引线框架设计能力之外的复杂信号路由。暴露的夹促进热量散发到周围环境或附接的散热器,并允许连接到地或其他参考电压。多层衬底避免线键合封装的寄生电感问题,而没有嵌入式管芯封装的额外成本和复杂性。此外,多层衬底能够实现比引线框架更复杂的路由。示例应用包括具有hemt器件(例如,gan或sic晶体管等)的电源电路,并且可以在单个封装的器件中容纳多个管芯。

45.在权利要求的范围内,在描述的实施例中修改是可能的,并且其他实施例是可能的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1