放大装置的制作方法

1.本公开涉及放大装置。本技术主张基于2019年5月27日申请的日本技术第2019

‑

098593号的优先权,引用上述日本技术中记载的所有的记载内容。

背景技术:

2.专利文献1中记载有与宽带放大器相关的技术。该宽带放大器具备信号放大用晶体管。在信号放大用晶体管的输入侧及输出侧分别连接有由电感构成的匹配电路、由电容器构成的匹配电路。而且,包含电阻及电容器的并联反馈电路连接在被分割的输入匹配电路的分割点与被分割的输出匹配电路的分割点之间。专利文献1所记载的宽带放大器通过具备这样的结构,试图减少高频区域的增益的降低,扩大作为放大器的频带。

3.专利文献2中记载有与微波放大器相关的技术。该微波放大器具有放大元件和反馈电路,该放大元件具有输入端子及输出端子,该反馈电路将输出到该放大元件的输出端子侧的输出的一部分反馈到放大元件的输入端子侧。反馈电路形成为通过放大元件所在的面的上方或下方。或者,反馈电路形成为通过由放大元件的接地端子接地的两处接地部位夹着的内侧区域。专利文献2所记载的微波放大器试图缩短反馈电路长度,提高特性。现有技术文献专利文献

4.专利文献1:日本特开平5

‑

315865号公报专利文献2:日本特开平6

‑

037559号公报

技术实现要素:

5.本公开的放大装置具备半导体芯片、封装体、第一反馈电路、第二反馈电路。半导体芯片具有半导体基板、多个晶体管、栅极焊盘组、漏极焊盘组、源极焊盘组。半导体基板具有彼此相对的第一端边及第二端边。各晶体管在半导体基板上具有源极电极、栅极电极及漏极电极。栅极焊盘组包括多个栅极焊盘,多个栅极焊盘沿着第一端边配置在半导体基板上且与多个晶体管各自的栅极电极连接。漏极焊盘组包括多个漏极焊盘,多个漏极焊盘沿着第二端边配置在半导体基板上且与多个晶体管各自的漏极电极连接。源极焊盘组包括多个源极焊盘,多个源极焊盘与多个晶体管各自的源极电极连接。封装体具有接合半导体芯片的底面的金属制的基座、包围半导体芯片的绝缘性的侧壁、与栅极焊盘组连接且从侧壁的内侧向外侧延伸的输入引线及与漏极焊盘组连接且从侧壁的内侧向外侧延伸的输出引线。第一反馈电路及第二反馈电路具有设置在金属制的基座上的电介质基板、配置在电介质基板上的反馈电阻及与反馈电阻串联连接的电容器。第一反馈电路及第二反馈电路电连接在栅极焊盘组与漏极焊盘组之间。第一反馈电路配置在第一端边及第二端边的延伸方向上的半导体芯片的一侧的基座上。第二反馈电路配置在所述延伸方向上的半导体芯片的另一侧的基座上。

附图说明

6.图1是表示本公开的一个实施方式的放大装置的结构的俯视图。图2是将半导体芯片放大而表示的俯视图。图3是表示从前壁部分观察半导体芯片及反馈电路的图。图4是放大装置的电路图。图5是第一变形例的放大装置的俯视图。图6是第二变形例的放大装置的俯视图。

具体实施方式

7.[本公开所要解決的课题]近年来,要求能够应对高频且宽频带的半导体放大装置。这里所说的宽频带是指,例如覆盖从数十khz至数百khz的lf(low freqency:低频)带至数ghz的rf(radio freqency:射频)带的频带。以这样的宽的频带为对象,作为提高晶体管的放大特性的方法,有从晶体管的漏极向栅极实施反馈的方法(例如参照专利文献1、2)。由于在晶体管的栅极与漏极上信号的位相相差180

°

,所以从漏极向栅极实施反馈的电路成为负反馈电路。而且,根据增益带宽积(gb积)一定的法则,频带扩大与增益减少相应的量。反馈电路例如由电阻及电容器的串联电路构成。

[0008]

另一方面,对近年来的高频晶体管要求能够应对更大的电流。因此,晶体管的尺寸逐渐大型化,例如具有数十条这样的多个栅极指的结构也正在实用化。在这样的尺寸大的晶体管中,连接栅极和漏极的反馈电路的布线路径变长,布线的电感诱发晶体管的频率特性的紊乱。

[0009]

因此,本公开的目的在于提供能够缩短反馈电路的布线路径而抑制晶体管的频率特性的紊乱的放大装置。

[0010]

[本公开的效果]根据本公开,能够提供能够缩短反馈电路的布线路径而抑制晶体管的频率特性的紊乱的放大装置。

[0011]

[本公开的实施方式的说明]首先,列举本公开的实施方式进行说明。一个实施方式的放大装置具备半导体芯片、封装体、第一反馈电路、第二反馈电路。半导体芯片具有半导体基板、多个晶体管、栅极焊盘组、漏极焊盘组、源极焊盘组。半导体基板具有彼此相对的第一端边及第二端边。各晶体管在半导体基板上具有源极电极、栅极电极及漏极电极。栅极焊盘组包括多个栅极焊盘,多个栅极焊盘沿着第一端边配置在半导体基板上,且与多个晶体管各自的栅极电极连接。漏极焊盘组包括多个漏极焊盘,多个漏极焊盘沿着第二端边配置在半导体基板上,且与多个晶体管各自的漏极电极连接。源极焊盘组包括多个源极焊盘,多个源极焊盘与多个晶体管各自的源极电极连接。封装体具有接合半导体芯片的底面的金属制的基座、包围半导体芯片的绝缘性的侧壁、与栅极焊盘组连接并从侧壁的内侧向外侧延伸的输入引线及与漏极焊盘组连接且从侧壁的内侧向外侧延伸的输出引线。第一反馈电路及第二反馈电路具有设置在金属制的基座上的电介质基板、配置在电介质基板上的反馈电阻及与反馈电阻串联连接的电容器。第一反馈电路及第二反馈电路电连接在栅极焊盘组与漏极焊盘组之间。第一

反馈电路配置在第一端边及第二端边的延伸方向上的半导体芯片的一侧的基座上。第二反馈电路配置在所述延伸方向上的半导体芯片的另一侧的基座上。

[0012]

在该放大装置中,在封装体内搭载半导体芯片的基座上,与半导体芯片并列地设置有第一反馈电路及第二反馈电路。因此,与例如在封装体的外部设置反馈电路的情况相比,能够缩短反馈电路的布线路径。因此,根据该放大装置,能够有效地抑制半导体芯片所具有的各晶体管的频率特性的紊乱。另外,在该放大装置中,至少设置两个反馈电路,第一反馈电路设置于半导体基板的第一端边及第二端边的延伸方向上的半导体芯片的一侧,第二反馈电路设置于所述延伸方向上的半导体芯片的另一侧。在该情况下,与仅在半导体芯片的单侧设置反馈电路的情况相比,能够降低由各栅极焊盘及各漏极焊盘与反馈电路的距离的偏差引起的特性偏差。

[0013]

在上述的放大装置中,也可以是,第一反馈电路的反馈电阻的电阻值与第二反馈电路的反馈电阻的电阻值彼此相等。在该情况下,对第一反馈电路及第二反馈电路赋予均等的特性,能够更有效地抑制半导体芯片所具有的各晶体管的频率特性的紊乱。

[0014]

在上述的放大装置中,也可以是,第一反馈电路及第二反馈电路的电容器是设置在输出引线上的管芯电容器。在该情况下,能够在狭窄的封装体内容易地配置电容器。

[0015]

在上述的放大装置中,也可以是,电介质基板经由含金属粘接剂固定于基座,第一反馈电路及第二反馈电路具有作为电连接在栅极焊盘组与反馈电阻之间的上述电容器的输入侧电容器和作为电连接在漏极焊盘组与反馈电阻之间的上述电容器的输出侧电容器。在多数情况下,栅极偏压为负电压,若固定电介质基板和基座的例如银膏这样的含金属粘接剂的金属因水分而离子化,则该金属离子向电介质基板上的负电位的布线爬升。将其称为离子迁移。如上所述,若设置输入侧电容器及输出侧电容器,则在这些电容器间,偏压被切断而电位不定。因此,能够抑制离子迁移。

[0016]

在上述的放大装置中,也可以是,含金属粘接剂为烧结型的金属糊剂。

[0017]

在上述的放大装置中,也可以是,半导体芯片还具有:第一辅助焊盘,设置在半导体基板的第一端边及第二端边的延伸方向上的栅极焊盘组的一侧的半导体基板上;及第二辅助焊盘,设置在所述延伸方向上的栅极焊盘组的另一侧的半导体基板上。而且,也可以是,第一反馈电路经由第一辅助焊盘而与栅极焊盘组电连接,第二反馈电路经由第二辅助焊盘而与栅极焊盘组电连接。在该情况下,能够容易地将第一反馈电路及第二反馈电路与栅极焊盘组连接。

[0018]

在上述的放大装置中,也可以是,第一反馈电路及第二反馈电路的反馈电阻是形成于电介质基板的主面的薄膜电阻。在该情况下,能够容易地实现反馈电阻。

[0019]

在上述的放大装置中,也可以是,电介质基板比半导体基板厚。在该情况下,能够将电介质基板上的反馈电路的布线与基座之间产生的寄生电容抑制得较小。

[0020]

在上述的放大装置中,也可以是,第一反馈电路及第二反馈电路的反馈电阻具有在反馈电阻的延伸方向上排列的多个接合焊盘。在该情况下,通过使用接合线使任意的接合焊盘间短路,能够容易地将反馈电阻的电阻值调整为任意的大小。

[0021]

在上述的放大装置中,也可以是,封装体的侧壁包括在与半导体基板的第一端边及第二端边的延伸方向交叉的方向上彼此相对的前壁部分及后壁部分,输入引线从前壁部分的内侧向外侧延伸,输出引线从后壁部分的内侧向外侧延伸。

[0022]

在上述的放大装置中,也可以是,第一反馈电路及第二反馈电路的电介质基板具有以半导体基板的第一端边及第二端边的延伸方向为短边方向的长方形状的平面形状。在该情况下,使电介质基板的一端接近输入引线、并使电介质基板的另一端接近输出引线而缩短接合线,能够降低接合线所具有的电感。

[0023]

在上述的放大装置中,也可以是,第一反馈电路及第二反馈电路的反馈电阻从电介质基板的长度方向上的一端到另一端多次弯折并延伸。在该情况下,能够延长反馈电阻而进一步成为高电阻。

[0024]

在上述的放大装置中,也可以是,第一反馈电路及第二反馈电路的电介质基板由陶瓷构成。

[0025]

在上述的放大装置中,也可以是,第一反馈电路的电容器的电容值与第二反馈电路的电容器的电容值彼此相等。

[0026]

[本公开的实施方式的详细内容]以下参照附图对本公开的放大装置的具体例进行说明。此外,本发明并不限定于这些例示,而是由权利要求书表示,意图包括与权利要求书等同含义及范围内的所有的变更。在以下的说明中,在附图的说明中对同一要素标注同一附图标记,并省略重复的说明。

[0027]

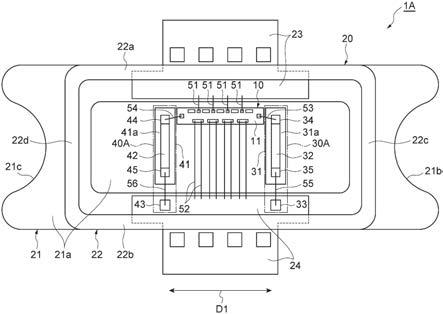

图1是表示本公开的一个实施方式的放大装置的结构的俯视图。该放大装置1a具备半导体芯片10、封装体20、第一反馈电路30a、第二反馈电路40a。半导体芯片10设有在半导体基板上具有源极电极、栅极电极及漏极电极的多个晶体管而成。构成半导体芯片10的晶体管例如是栅极宽度为6mm的fet,在一例中,是主要包含gan系半导体的高电子迁移率晶体管(hemt)。半导体芯片10的最大输出例如为30w。

[0028]

图2是放大表示半导体芯片10的俯视图。半导体芯片10具有半导体基板11、设置在半导体基板11的主面上的栅极焊盘组12、漏极焊盘组13、第一辅助焊盘14、第二辅助焊盘15及源极焊盘组16。半导体基板11具有以方向d1为长度方向的长方形状的平面形状。半导体基板11具有分别沿着方向d1延伸并在与方向d1交叉的方向上彼此相对的一对端边11a、11b。端边11a是本实施方式中的第一端边的例子。端边11b是本实施方式中的第二端边的例子。半导体基板11还具有将端边11a、11b的一端彼此相连并在与方向d1交叉的方向上延伸的侧边11c、将端边11a、11b的另一端彼此相连并在与方向d1交叉的方向上延伸的侧边11d。

[0029]

栅极焊盘组12包括与多个晶体管各自的栅极电极连接的多个栅极焊盘12a。多个栅极焊盘12a是形成在半导体基板11上的例如au膜这样的金属膜。多个栅极焊盘12a沿着一对端边11a、11b中的一方、例如端边11a在半导体基板11上排列配置。此外,图中以4个栅极焊盘12a为例示出,但栅极焊盘12a的个数为2以上的任意的个数。各栅极焊盘12a与设置在半导体基板11的活性区域上的未图示的1根或2根以上(例如6根)栅极电极即栅极指电连接。如图1所示,各栅极焊盘12a经由接合线51而与后述的封装体20的输入引线23电连接。此外,各栅极电极与半导体的接触宽度即单位栅极宽度例如为200μm。

[0030]

漏极焊盘组13包含与多个晶体管各自的漏极电极连接的多个漏极焊盘13a。多个漏极焊盘13a是形成在半导体基板11上的例如au膜这样的金属膜。多个漏极焊盘13a沿着一对端边11a、11b中的另一方例如端边11b在半导体基板11上排列配置。漏极焊盘13a的个数例如与栅极焊盘12a的个数相同。各漏极焊盘13a与设置在半导体基板11的活性区域上的未图示的2根以上的漏极电极即漏极指电连接。如图1所示,各漏极焊盘13a经由接合线52而与

后述的封装体20的输出引线24电连接。

[0031]

辅助焊盘14是形成在半导体基板11上的例如au膜这样的金属膜。辅助焊盘14设置于方向d1上的栅极焊盘组12的一侧的半导体基板11上的区域即栅极焊盘组12与侧边11c之间的区域。辅助焊盘14通过设置在半导体基板11上的布线而与栅极焊盘组12所包含的一部分栅极焊盘12a电连接。如图1所示,辅助焊盘14经由接合线53而与反馈电路30a电连接。

[0032]

辅助焊盘15是形成在半导体基板11上的例如au膜这样的金属膜。辅助焊盘15设置于方向d1上的栅极焊盘组12的另一侧的半导体基板11上的区域即栅极焊盘组12与侧边11d之间的区域。辅助焊盘15通过设置在半导体基板11上的布线而与栅极焊盘组12所包含的剩余的栅极焊盘12a电连接。如图1所示,辅助焊盘15经由接合线54而与反馈电路40a电连接。

[0033]

源极焊盘组16包含与多个晶体管各自的源极电极连接的多个源极焊盘16a。多个源极焊盘16a是形成在半导体基板11上的例如au膜这样的金属膜。多个源极焊盘16a沿着一对端边11a、11b中的一方、例如端边11a与栅极焊盘12a交替地在半导体基板11上排列配置。各源极焊盘16a与设置在半导体基板11的活性区域上的未图示的2根以上的源极电极即源极指电连接。各源极焊盘16a经由贯通半导体基板11的通孔而与半导体芯片10的未图示的背面电极膜电连接。

[0034]

此外,与1个栅极焊盘12a连接的1或2个以上的栅极指和夹着这些栅极指的源极指及漏极指构成1个晶体管单元。图2中示出了包含4个晶体管单元的半导体芯片10,但晶体管单元的个数是任意的。例如,在半导体芯片10包含8个晶体管单元的情况下,作为晶体管单元的排列方向的方向d1上的半导体芯片10的整个宽度例如也为6mm。

[0035]

再次参照图1。封装体20具有基座21、侧壁22、输入引线23及输出引线24。基座21是金属制的板状的部件。在方向d1上的基座21的两端,形成有用于通过螺纹固定来固定放大装置1a的半圆形的一对凹部21b、21c。基座21具有平坦的主面21a。在方向d1上的主面21a的中央部,半导体芯片10的底面即背面电极膜经由含金属粘接剂而导电接合。含金属粘接剂例如是烧结型的金属糊剂,在一例中为银膏。半导体芯片10与基座21的导电接合例如通过在基座21的主面21a上涂布金属糊剂、将半导体芯片10配置在该金属糊剂上后通过热处理使金属糊剂所包含的树脂挥发来进行。在多数情况下,基座21被规定为基准电位即gnd电位,因此半导体芯片10的源极电极通过背面电极膜及通孔而被规定为基准电位。

[0036]

侧壁22是包围半导体芯片10的绝缘性的部件。侧壁22立设在基座21的主面21a上。本实施方式的侧壁22的平面形状是以方向d1为长度方向的大致长方形的框状。具体而言,侧壁22包括前壁部分22a、后壁部分22b、侧壁部分22c及侧壁部分22d。前壁部分22a及后壁部分22b分别沿着方向d1延伸,并且在与方向d1交叉的方向上彼此相对。侧壁部分22c将前壁部分22a及后壁部分22b的各一端相连。侧壁部分22d将前壁部分22a及后壁部分22b的各另一端相连。半导体芯片10与前壁部分22a的距离比半导体芯片10与后壁部分22b的距离小。侧壁22例如为陶瓷制。在侧壁22的上表面接合有未图示的盖部即罩,由此侧壁22的内侧被气密地密封。

[0037]

输入引线23是金属制的板状部件。输入引线23贯通前壁部分22a,从前壁部分22a的内侧向外侧延伸。输入引线23的上表面在前壁部分22a的内侧及外侧的双方从前壁部分22a露出。前壁部分22a的内侧的输入引线23的上表面经由多个接合线51而与多个栅极焊盘12a电连接。在一例中,在1个栅极焊盘12a连接有1根接合线51。在位于前壁部分22a的外侧

的输入引线23的部分,导电连接放大装置1a的外部的布线。

[0038]

输出引线24是与输入引线23同样的金属制的板状部件。输出引线24贯通后壁部分22b,从后壁部分22b的内侧向外侧延伸。输出引线24的上表面在后壁部分22b的内侧及外侧的双方从后壁部分22b露出。后壁部分22b的内侧的输出引线24的上表面经由多个接合线52而与多个漏极焊盘13a电连接。在一例中,在1个漏极焊盘13a连接有2根接合线52。在位于后壁部分22b的外侧的输出引线24的部分,导电连接放大装置1a的外部的布线。

[0039]

反馈电路30a配置于方向d1上的半导体芯片10的一侧的基座21上的区域。反馈电路30a具有电介质基板31、反馈电阻32及电容器33。反馈电路40a配置于方向d1上的半导体芯片10的另一侧的基座21上的区域。反馈电路40a具有电介质基板41、反馈电阻42及电容器43。反馈电路30a、40a的一端侧分别经由辅助焊盘14、15而与栅极焊盘组12电连接。反馈电路30a、40a的另一端侧与输出引线24电连接。

[0040]

电介质基板31、41具有以方向d1为短边方向的长方形状的平面形状。电介质基板31、41例如由al2o3这样的陶瓷构成。图3是从前壁部分22a观察半导体芯片10及反馈电路30a、40a的图。如图3所示,电介质基板31、41比半导体基板11厚。在一例中,电介质基板31、41的厚度为250μm左右,半导体基板11的厚度为100μm左右。

[0041]

电介质基板31具有彼此相对的主面31a及背面31b。同样地,电介质基板41具有彼此相对的主面41a及背面41b。电介质基板31、41的背面31b、41b与基座21的主面21a相对,经由含金属粘接剂而与主面21a接合。含金属粘接剂例如为烧结型的金属糊剂,在一例中,为银膏。电介质基板31、41与基座21的接合方法和半导体芯片10与基座21的接合方法相同。即,将烧结型的金属糊剂涂布在基座21的主面21a上,将电介质基板31、41配置在该金属糊剂上后,通过热处理使金属糊剂所包含的树脂挥发来进行。电介质基板31、41与基座21的接合也可以和半导体芯片10与基座21的接合同时进行。

[0042]

反馈电阻32配置在电介质基板31上,沿电介质基板31的长度方向延伸。反馈电阻32例如是形成于电介质基板31的主面31a的薄膜电阻,在一例中,由nicr构成。反馈电阻32的电阻值例如为300ω。在主面31a的反馈电阻32的两端,设置有引线接合用的焊盘34、35。在一个焊盘34连接有前述的接合线53的一端,焊盘34经由接合线53与辅助焊盘14电连接。由此,反馈电阻32的dc电位被规定为栅极偏压。栅极偏压例如为

‑

2.8v。另一个焊盘35经由接合线55而与电容器33的一个电极电连接。

[0043]

反馈电阻42配置在电介质基板41上,沿电介质基板41的长度方向延伸。反馈电阻42与反馈电阻32同样地,例如是形成于电介质基板41的主面41a的薄膜电阻,在一例中,由nicr构成。反馈电阻42的电阻值例如与反馈电阻32的电阻值相等。在主面41a的反馈电阻42的两端,设置有引线接合用的焊盘44、45。在一个焊盘44连接有前述的接合线54的一端,焊盘44经由接合线54而与辅助焊盘15电连接。由此,反馈电阻42的dc电位被规定为栅极偏压。另一个焊盘45经由接合线56而与电容器43的一个电极电连接。

[0044]

电容器33在侧壁22的内侧的输出引线24与辅助焊盘14之间,与反馈电阻32串联连接。本实施方式的电容器33是配置在侧壁22的内侧的输出引线24上的管芯电容器。电容器33的一对电极中的与连接于接合线55的电极相反侧的电极与输出引线24导电接合。同样地,电容器43在侧壁22的内侧的输出引线24与辅助焊盘15之间,与反馈电阻42串联连接。本实施方式的电容器43是配置在侧壁22的内侧的输出引线24上的管芯电容器。电容器43的一

对电极中的与连接于接合线56的电极相反侧的电极与输出引线24导电接合。电容器43的电容值与电容器33的电容值相等。电容器33、43的电容值是在数ghz带到lf带中实质上可视为短接的大小,例如为20pf。

[0045]

在上述的例子中,反馈电路30a、40a的各一端分别经由辅助焊盘14、15而与栅极焊盘组12连接。不限于此,反馈电路30a、40a的各一端也可以不经由辅助焊盘14、15,而经由接合线等与栅极焊盘组12直接连接。另外,在上述的例子中,反馈电路30a、40a的各另一端经由输出引线24而与漏极焊盘组13连接。不限于此,反馈电路30a、40a的各另一端也可以不经由输出引线24,而经由接合线等与漏极焊盘组13直接连接。

[0046]

对由以上说明的本实施方式的放大装置1a得到的效果进行说明。图4是本实施方式的放大装置1a的电路图。在本实施方式中,为了在宽的频带中提高半导体芯片10的放大特性,通过反馈电路30a、40a,从半导体芯片10的漏极向栅极施加反馈。由于在半导体芯片10的栅极与漏极上信号的位相相差180

°

,所以从漏极向栅极施加反馈的电路成为负反馈电路。而且,根据增益带宽积(gb积)一定的法则,频带扩大与增益减少相应的量。此外,反馈主要取决于反馈电阻32、42,电容器33、43为了切断直流成分而设置。作为电容器33、43的电容值,设定在反馈作用的频带中实质上可视为短接(短路)的值。

[0047]

另一方面,对近年来的高频晶体管要求能够应对更大的电流。因此,半导体芯片的尺寸逐渐大型化,如本实施方式那样,例如具有数十条这样的多个栅极指的结构也在实用化。在具备这样的尺寸的大的半导体芯片的放大装置中,如以往那样,当在封装体20的外部在输入引线23与输出引线24之间连接反馈电路时,反馈电路的布线路径变长,布线的电感诱发晶体管的频率特性的紊乱。

[0048]

在本实施方式的放大装置1a中,在封装体20内,在搭载半导体芯片10的基座21上,与半导体芯片10并列地设置有反馈电路30a、40a。因此,与在封装体20的外部设置反馈电路的情况相比,能够缩短反馈电路的布线路径。因此,根据该放大装置1a,能够有效地抑制半导体芯片10所具有的各晶体管的频率特性的紊乱。

[0049]

另外,在反馈电路仅设置于半导体芯片10的单侧的情况下,方向d1上排列的栅极焊盘12a的个数越多,则根据各栅极焊盘12a的位置,各栅极焊盘12a与反馈电路的距离产生偏差。同样地,方向d1上排列的漏极焊盘13a的个数越多,则根据各漏极焊盘13a的位置,各漏极焊盘13a与反馈电路的距离产生偏差。连接各栅极焊盘12a和反馈电路的布线及连接各漏极焊盘13a和反馈电路的布线具有与它们的长度相应的电感。因此,这些距离的偏差成为反馈效果的偏差,从而成为半导体芯片10中包含的各晶体管的特性偏差的主要原因。特别是在超过数ghz的频率区域中,布线的电感对反馈效果的影响变大,晶体管的频率特性的紊乱显著显现。

[0050]

与此相对,在本实施方式中,设置有2个反馈电路30a、40a,一个反馈电路30a设置于方向d1上的半导体芯片10的一侧,另一个反馈电路40a设置于方向d1上的半导体芯片10的另一侧。在该情况下,与反馈电路仅设置于半导体芯片10的单侧的情况相比,能够减小反馈电路与各栅极焊盘12a的距离的偏差及反馈电路与各漏极焊盘13a的距离的偏差,能够降低因这些距离的偏差引起的各晶体管的特性偏差。另外,与反馈电路仅设置于半导体芯片10的单侧的情况相比,能够缩短连接反馈电路和半导体芯片10的布线的平均长度,因此能够进一步降低布线的电感对反馈效果的影响。

[0051]

如上所述,反馈电路30a的反馈电阻32的电阻值与反馈电路40a的反馈电阻42的电阻值也可以彼此相等。在该情况下,对反馈电路30a、40a赋予均等的特性,能够更有效地抑制半导体芯片10所具有的各晶体管的频率特性的紊乱。

[0052]

如上所述,反馈电路30a、40a的电容器33、43也可以是设置在输出引线24上的管芯电容器。在该情况下,能够在狭窄的封装体20内容易地配置电容器33、43。另外,不需要连接电容器33、43和输出引线24的接合线,能够降低布线的电感。

[0053]

如上所述,半导体芯片10也可以具有设置在方向d1上的栅极焊盘组12的一侧的半导体基板11上的辅助焊盘14和设置在方向d1上的栅极焊盘组12的另一侧的半导体基板11上的辅助焊盘15。而且,反馈电路30a也可以经由辅助焊盘14而与栅极焊盘组12连接,反馈电路40a经由辅助焊盘15而与栅极焊盘组12连接。在该情况下,能够容易地连接反馈电路30a、40a与栅极焊盘组12。

[0054]

如上所述,反馈电路30a的反馈电阻32也可以是形成于电介质基板31的主面31a的薄膜电阻。同样地,反馈电路40a的反馈电阻42也可以是形成于电介质基板41的主面41a的薄膜电阻。在这些情况下,能够容易地实现反馈电阻32、42。

[0055]

如上所述,反馈电路30a的反馈电阻32也可以设置在电介质基板31上。同样地,反馈电路40a的反馈电阻42也可以设置在电介质基板41上。在该情况下,能够将电介质基板31上的反馈电路30a的布线与基座21之间产生的寄生电容及电介质基板41上的反馈电路40a的布线与基座21之间产生的寄生电容抑制得较小。特别是在电介质基板31、41比半导体基板11厚的情况下,能够更有效地抑制它们的寄生电容。

[0056]

(第一变形例)图5是上述实施方式的第一变形例的放大装置1b的俯视图。本变形例与上述实施方式的不同点是反馈电路的结构及形状。具体而言,本变形例的放大装置1b具有反馈电路30b、40b来代替上述实施方式的反馈电路30a、40a。反馈电路30b具有反馈电阻36来代替上述实施方式的反馈电阻32。反馈电路40b具有反馈电阻46来代替上述实施方式的反馈电阻42。

[0057]

如图5所示,在本变形例中,由于延长反馈电阻而进一步形成高电阻,因此反馈电阻36、46从电介质基板31、41上的长度方向上的一端到另一端多次弯折并延伸。另外,在反馈电阻36上沿着反馈电阻36的延伸方向并列地设置有多个接合焊盘37。通过引线接合将任意一对接合焊盘37短路,能够使反馈电阻36的电阻值阶段性地可变。同样地,在反馈电阻46上沿着反馈电阻46的延伸方向并列地设置有多个接合焊盘47。通过引线接合将任意一对接合焊盘47短路,能够使反馈电阻46的电阻值阶段性地可变。这样,根据本变形例,能够容易地将反馈电阻36、46的电阻值调整为任意的大小。由于反馈电路30b、40b的反馈量与反馈电阻36、46的电阻值成反比,所以,由此,能够容易地调整反馈量。另外,反馈电阻36、46的电阻值的变更可以与半导体芯片10独立地实施。因此,即使在每个放大装置的半导体芯片10的晶体管特性存在偏差的情况下,通过根据各个晶体管特性设定反馈量,能够降低晶体管特性的偏差。

[0058]

(第二变形例)图6是上述实施方式的第二变形例的放大装置1c的俯视图。本变形例与上述第一变形例的不同点是反馈电路的结构。具体而言,本变形例的放大装置1c具有反馈电路30c、

40c来代替上述第一变形例的反馈电路30b、40b。

[0059]

反馈电路30c在第一变形例的反馈电路30b的结构的基础上,还具有电容器38。电容器38在侧壁22的内侧的输入引线23与输出引线24之间,与反馈电阻36及电容器33串联连接。电容器38是配置在侧壁22的内侧的输入引线23上的管芯电容器。电容器38的一个电极经由接合线57而与焊盘34电连接,另一个电极与输入引线23导电接合。

[0060]

同样地,反馈电路40c在第一变形例的反馈电路40b的结构的基础上,还具有电容器48。电容器48在侧壁22的内侧的输入引线23与输出引线24之间,与反馈电阻46及电容器43串联连接。电容器48是配置在侧壁22的内侧的输入引线23上的管芯电容器。电容器48的一个电极经由接合线58而与焊盘44电连接,另一个电极与输入引线23导电接合。电容器48的电容值与电容器38的电容值相等。

[0061]

电容器38、48相当于本变形例的输入侧电容器。电容器33、43相当于本变形例的输出侧电容器。本变形例的电容器38、48与输入引线23连接,但电容器38、48也可以不经由输入引线23,而经由接合线等与栅极焊盘组12直接连接。

[0062]

在多数情况下,栅极偏压为负电压。因此,当固定电介质基板31、41和基座21的例如银膏这样的含金属粘接剂的金属因水分而离子化时,该金属离子向电介质基板31、41上的负电位的布线爬升。而且,电介质基板31、41上的布线与作为基准电位的基座21有可能短路。将这样的现象称为离子迁移。若如本变形例那样设置输入侧的电容器38、48及输出侧的电容器33、43,则在这些电容器间,偏压被切断而电位不定,即成为浮动状态。因此,能够抑制离子迁移。

[0063]

此外,对这样的离子迁移的对策不限于陶瓷封装体,在树脂模塑封装体中也是有效的。在树脂模塑封装体中,水分向封装体内的侵入比陶瓷封装体多,因此使电介质基板31、41上的布线的dc电位为浮动状态是更有效的。

[0064]

本公开的放大装置不限于上述的实施方式,能够进行其他各种变形。例如,在上述实施方式及各变形例中,电容器33、43安装在输出引线24上,但电容器33、43也可以分别配置在电介质基板31、41上。在该情况下,通过接合线将电容器33、43和输出引线24或漏极焊盘组13连接。附图标记说明

[0065]

1a、1b、1c

…

放大装置10

…

半导体芯片11

…

半导体基板11a、11b

…

端边11c、11d

…

侧边12

…

栅极焊盘组12a

…

栅极焊盘13

…

漏极焊盘组13a

…

漏极焊盘14、15

…

辅助焊盘16

…

源极焊盘组16a

…

源极焊盘

20

…

封装体21

…

基座21a

…

主面21b、21c

…

凹部22

…

侧壁22a

…

前壁部分22b

…

后壁部分22c、22d

…

侧壁部分23

…

输入引线24

…

输出引线30a、30b、30c

…

第一反馈电路40a、40b、40c

…

第二反馈电路31、41

…

电介质基板31a、41a

…

主面31b、41b

…

背面32、42

…

反馈电阻33、43

…

电容器34、35、44、45

…

焊盘36、46

…

反馈电阻37、47

…

接合焊盘38、48

…

电容器51~58

…

接合线d1

…

方向。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1